EDA实验 16×16点阵字符显示设计

16x16点阵显示实验报告

16*16点阵显示实验报告一、实验目的(1)学习点阵显示字符的基本原理。

(2)掌握用数控分频控制速度,实现点阵扫描的基本方式。

(3)会使用Quartus II软件中的Verilog HDL语言实现点真的行列循环显示。

二、实验设备与器件Quartus II 软件、EP2C8Q208C8实验箱三、实验方案设计1.实验可实现的功能可通过编写Verilog HDL语言,实现点阵的行列交替扫描。

先是行扫描,扫描间隔为1s,16行都扫描完之后开始列扫描,扫描间隔仍然为1s,16列扫描完之后,行继续扫描,依次循环。

2.点阵基本知识16*16扫描LED点阵只要其对应的X、Y轴顺向偏压,即可使LED发亮。

例如如果想使左上角LED点亮,则Y0=1,X0=0即可。

应用时限流电阻可以放在X轴或Y轴。

它有16个共阴极输出端口,每个共阴极对应有16个LED显示灯。

LED点阵每个点都有一个红色的发光二极管。

点阵内的二极管间的连接都是行共阳,列共阴。

本实验采用共阴,当二极管的共阳极为高电平,共阴极为低电平时,所接点发光;反之处于截止状态,不放光。

3.系统工作原理本系统用了两个模块,其中dianzhen.v是顶层文件,而hangsaomiao.v和liesaomiao.v是两个子模块,总体的系统功能框图如图3.3.1所示。

图3.3.1 系统功能图示通过流程图可以看到,体统是先将试验箱的50MHz时钟信号分频为1s,因为要实现16*16的点阵扫描,所以用一个16s的计时器计时,每经过16s行扫描与列扫描的状态转换一次,通过点阵显示出来。

4.模块化程序设计(1)点阵显示顶层程序设计module dianzhen (clk50mhz,row,sel0,sel1,sel2,sel3,line);input clk50mhz; //实验箱提供50MHz时钟信号output sel0,sel1,sel2,sel3; //设置引脚选通点阵output reg [15:0] row; //行output reg [3:0] line; //列wire [15:0] row1,row2;wire [3:0] line1,line2;reg [24:0] cnt=0; //1Hz计数子reg [4:0] cnt1=0; //16s计数子assign sel0=1'b0;assign sel1=1'b1;assign sel2=1'b0;assign sel3=1'b0;always@(posedge clk50mhz)beginif(cnt>=25'd5*******)begincnt<=25'b0; //1Hz计时器cnt1<=cnt1+1; //16s计时器endelsecnt<=cnt+1;endhangsaomiao u1(.clk50mhz(clk50mhz),.row(row1),.line(line1)); liesaomiao u2(.clk50mhz(clk50mhz),.row(row2),.line(line2));always@(*)if(cnt1<=5'd15)beginrow<=row1; //行扫描line<=line1;endelsebeginrow<=row2; //列扫描line<=line2;endendmodule(2)行扫描模块hangsaomiao.v程序设计module hangsaomiao(clk50mhz,line,row);input clk50mhz; //实验箱输入50MHz时钟信号output reg [15:0] row; //列output reg [3:0] line; //行reg [24:0] cnt1,cnt2; //计数子reg clkrow,clkline; //行脉冲、列脉冲always@(posedge clk50mhz)beginif(cnt1>=25'd5*******)begincnt1<=25'b0;clkrow=~clkrow; //1s列脉冲endelsecnt1<=cnt1+1;endalways@(posedge clk50mhz)beginif(cnt2>=25'd500)begincnt2<=25'b0;clkline=~clkline; //50KHz行脉冲endelsecnt2<=cnt2+1;endalways@(posedge clkline)begincase(line)4'd0:line<=4'd1; //高速行扫描4'd1:line<=4'd2;4'd2:line<=4'd3;4'd3:line<=4'd4;4'd4:line<=4'd5;4'd5:line<=4'd6;4'd6:line<=4'd7;4'd7:line<=4'd8;4'd8:line<=4'd9;4'd9:line<=4'd10;4'd10:line<=4'd11;4'd11:line<=4'd12;4'd12:line<=4'd13;4'd13:line<=4'd14;4'd14:line<=4'd15;4'd15:line<=4'd0;default:line<=4'd0;endcaseendalways@(posedge clkrow) //时间间隔为1s的列扫描begincase(row)16'b0000000000000001: row<=16'b0000000000000010;16'b0000000000000010: row<=16'b0000000000000100;16'b0000000000000100: row<=16'b0000000000001000;16'b0000000000001000: row<=16'b0000000000010000;16'b0000000000010000: row<=16'b0000000000100000;16'b0000000000100000: row<=16'b0000000001000000;16'b0000000001000000: row<=16'b0000000010000000;16'b0000000010000000: row<=16'b0000000100000000;16'b0000000100000000: row<=16'b0000001000000000;16'b0000001000000000: row<=16'b0000010000000000;16'b0000010000000000: row<=16'b0000100000000000;16'b0000100000000000: row<=16'b0001000000000000;16'b0001000000000000: row<=16'b0010000000000000;16'b0010000000000000: row<=16'b0100000000000000;16'b0100000000000000: row<=16'b1000000000000000;16'b1000000000000000: row<=16'b0000000000000001;default : row<=16'b0000000000000001;endcaseendendmodule(3)列扫描模块liesaomiao.v程序设计module liesaomiao(clk50mhz,row,line);input clk50mhz; //实验箱输入50MHz 时钟信号output reg [15:0] row; //行output reg [3:0] line; //列reg [24:0] cnt; //计数子reg clk;always@(posedge clk50mhz)beginif(cnt>=25'd5*******)begincnt<=25'b0;clk=~clk; //1sendelsecnt<=cnt+1;endalways @ (posedge clk) //列扫描begincase(line)4'h0:begin row=16'b1111111111111111;line<=4'h1; end4'h1:begin row=16'b1111111111111111;line<=4'h2; end4'h2:begin row=16'b1111111111111111;line<=4'h3; end4'h3:begin row=16'b1111111111111111;line<=4'h4; end4'h4:begin row=16'b1111111111111111;line<=4'h5; end4'h5:begin row=16'b1111111111111111;line<=4'h6; end4'h6:begin row=16'b1111111111111111;line<=4'h7; end4'h7:begin row=16'b1111111111111111;line<=4'h8; end4'h8:begin row=16'b1111111111111111;line<=4'h9; end4'h9:begin row=16'b1111111111111111;line<=4'ha; end4'ha:begin row=16'b1111111111111111;line<=4'hb; end4'hb:begin row=16'b1111111111111111;line<=4'hc; end4'hc:begin row=16'b1111111111111111;line<=4'hd; end4'hd:begin row=16'b1111111111111111;line<=4'he; end4'he:begin row=16'b1111111111111111;line<=4'hf; end4'hf:begin row=16'b1111111111111111;line<=4'h0; enddefault:line<=4'h0;endcaseendendmodule5.下载电路及引脚分配设计设计中用实验箱自带的50MHz时钟信号作为输入端,用sel0、sel1、sel2、sel3四个使能端选通点阵,EP2C8Q208C8就会工作在给点阵下命令的状态,并用line和row分别作为点阵的行、列选通端,最终使得点阵正常工作,如图3.5.1所示。

16×16点阵显示实验 实验报告

1.实验现象

当设计文件加载到目标器件后,将数字信号源模块的时钟选择为1KHZ,按下矩阵键盘的某一个键,则在数码管上显示对应的这个键标识的键值,当再按下第二个键的时候前一个键的键值在数码管上左移一位。按下“*”键则在数码管是显示“E”键值。按下“#”键在数码管上显示“F”键值。

2.实验图片记录

2)新建VHDL File(程序)

3)编译仿真

4)管脚分配

5)下载调试

2)加强对总线产生地址定位的CPLD实现方法的理解

3)掌握在FPGA中调用ROM的方法

成绩: 教师:

实验报告

一、实验内容及步骤

1.实验内容

1)通过编程实现对16×16点阵的控制

2)在点阵循环中显示“欢迎使用嵌入式SDC开发系统”这几个汉字和字符

3)运用软件对程序进行编译和仿真

2.实验步骤:

1)新建工程

成绩: 教师: 批改日期:

பைடு நூலகம்湖南科技大学

物理与电子科学学院专业实验报告

实验课程:FPGA实验原理

实验项目:16×16点阵显示实验

专 业:物理与电子科学学院

班 级:电子信息科学与技术3班

***********

学 号:**********

实验日期: 年 月 日

实验预习报告

一、实验目的及要求

1)加强点阵字符产生的显示原理和系统的16×16点阵的工作原理

16×16点阵汉字设计-左移-右移-翻页-上移-下移-多种方式

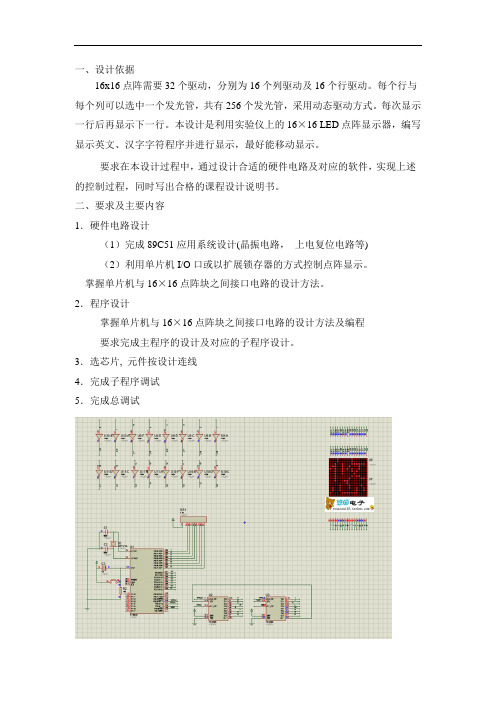

一、设计依据16x16点阵需要32个驱动,分别为16个列驱动及16个行驱动。

每个行与每个列可以选中一个发光管,共有256个发光管,采用动态驱动方式。

每次显示一行后再显示下一行。

本设计是利用实验仪上的16×16 LED点阵显示器,编写显示英文、汉字字符程序并进行显示,最好能移动显示。

要求在本设计过程中,通过设计合适的硬件电路及对应的软件,实现上述的控制过程,同时写出合格的课程设计说明书。

二、要求及主要内容1.硬件电路设计(1)完成89C51应用系统设计(晶振电路,上电复位电路等)(2)利用单片机I/O口或以扩展锁存器的方式控制点阵显示。

掌握单片机与16×16点阵块之间接口电路的设计方法。

2.程序设计掌握单片机与16×16点阵块之间接口电路的设计方法及编程要求完成主程序的设计及对应的子程序设计。

3.选芯片, 元件按设计连线4.完成子程序调试5.完成总调试三、途径和方法综合运用单片机和电子电路相关知识,实现本次设计。

进行程序设计时先画流程图再进行程序设计。

子程序调试按以下步骤进行:(1)实验板与PC机联机。

(2)利用实验系统16×16点阵实验单元,以两种方式控制点阵显示。

要求编制程序实现汉字点阵循环显示。

点阵时钟摘要LED点阵显示屏是利用发光二极管点阵模块或像素单元组成的平面式显示屏幕。

它具有发光效率高、使用寿命长、组态灵活、色彩丰富以及对室内外环境适应能力强等优点。

并广泛的应用于公交汽车,码头,商店,学校和银行等公共场合的信息发布和广告宣传。

LED显示屏经历了从单色,双色图文显示屏到现在的全彩色视频显示屏的发展过程,自20世纪八十年代开始,LED显示屏的应用领域已经遍布交通、电信、教育、证券、广告宣传等各方面。

LED点阵显示屏可以显示数字或符号,通常用来显示时间、速度、系统状态等。

文章给出了一种基于MCS-51单片机的16×16 点阵LED显示屏的设计方案。

eda16×16点阵字符发生器

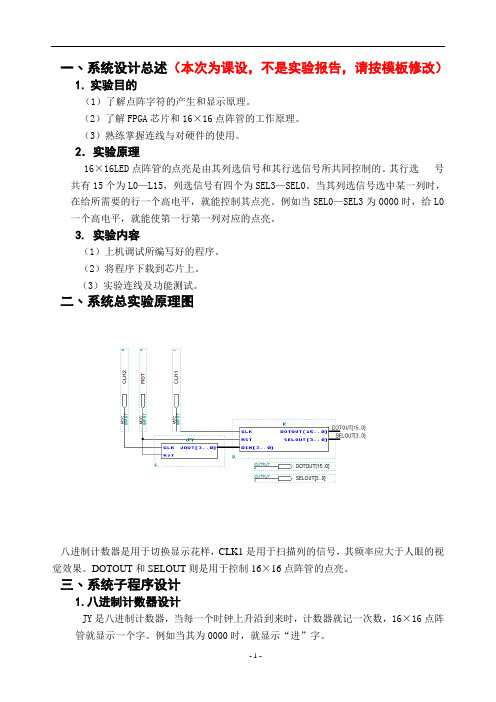

一﹑系统设计总述(本次为课设,不是实验报告,请按模板修改)1.实验目的(1)了解点阵字符的产生和显示原理。

(2)了解FPGA芯片和16×16点阵管的工作原理。

(3)熟练掌握连线与对硬件的使用。

2.实验原理16×16LED点阵管的点亮是由其列选信号和其行选信号所共同控制的。

其行选号共有15个为L0—L15,列选信号有四个为SEL3—SEL0。

当其列选信号选中某一列时,在给所需要的行一个高电平,就能控制其点亮。

例如当SEL0—SEL3为0000时,给L0一个高电平,就能使第一行第一列对应的点亮。

3. 实验内容(1)上机调试所编写好的程序。

(2)将程序下载到芯片上。

(3)实验连线及功能测试。

二﹑系统总实验原理图八进制计数器是用于切换显示花样,CLK1是用于扫描列的信号,其频率应大于人眼的视觉效果。

DOTOUT和SELOUT则是用于控制16×16点阵管的点亮。

三﹑系统子程序设计1.八进制计数器设计JY是八进制计数器,当每一个时钟上升沿到来时,计数器就记一次数,16×16点阵管就显示一个字。

例如当其为0000时,就显示“进”字。

其程序如下library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity jy isport(clk,rst:in std_logic;jout:buffer std_logic_vector(3 downto 0));end jy;architecture b of jy isbeginprocess(clk,rst)beginif rst='1' then jout<="0000";elsif clk'event and clk='1' thenif jout=7 then jout<="0000" ;else jout<=jout+1;end if;end if;end process;end b;其仿真波形2.行列驱动设计此程序是文字显示,即“进德修业,精益求精”通过计数器的计数而循环显示。

16x16点阵-EDA课程设计

应用科学学院SOPC/EDA综合课程设计报告设计题目:设计者:学号:班级:指导老师:完成时间:目录第1章总体设计原理及原理框图 (1)1.1 设计原理 (1)1.2顶层文件设计 (2)1.3总体仿真图 (2)第2章单元电路设计 (4)2.1时序控制模块设计 (4)2.1.1时序控制模块的源程序及其实体图 (4)2.1.2时序控制模块仿真 (5)2.2扫描控制模块设计 (5)2.2.1扫描控制模块源程序及其实体图 (5)2.2.2扫描控制模块仿真 (6)2.3显示控制模块源程序及其实体图 (6)2.3.1显示控制模块 (6)2.3.2显示控制模块仿真 (21)第3章心得体会 (22)参考文献 (23)1第1章 总体设计原理及原理框图1.1 设计原理首先我们设计要正确显示这些字,显示屏上的灯的亮暗情况具体应如何。

如第一个字‘江’:第一种方案 第二种方案如果高电平‘1 时表示灯是亮的,低电平‘0’时灯是暗的,这样上面的灯呈现在我们眼前的就是‘江’字了。

依次类推,我们就可以设计出所有要显示的字了。

使用FPGA 设计一个16×16的点阵显示的控制器,使点阵显示器以两种花样显示“江西理工大学应用科学学院欢迎您”第一种花样是用亮着的灯组合所要显示的字,第二种方案是用暗着的灯组成所需要的字。

这样这些字就好象是被我们当作了固定模型了。

但如何点亮这些灯呢,这就要求有一个脉冲循环扫描的电路,我们采用列扫描,当扫描的和我们先设计好的字模型的高电平相匹配时,灯就相应的点亮。

由于扫描的速度很快,我们人的眼睛并不会感到灯的闪烁,所以每扫描完16列就会显示在我们眼中一个字了。

但要所有的字母就可以依次的显示出来并不停的循环显示,就还要再有一个时序控制电路来控制。

此时序控制电路象一个计数器,有自动清零的功能,这样就可以实现循环的效果了。

其设计原理图框图如下图1.1 总体设计框图1.2顶层文件设计顶层文件来实现循环显示各个字的功能。

vhdl实验报告_16乘16点阵_列选_显示

综合实践总结报告综合实践名称: EDA技术与实践综合实践地点、时间一.题目功能分析和设计实验的要求有如下三点:1.用16*16点阵的发光二极管显示字符;2.可显示字符为0~9的数字字符与A~F英文字母的大写;3.输入为四位二进制矢量;按照要求可知,LED点阵模块,共由16×16=256个LED发光二极管组成,如何在该点阵模块上显示数字和字母是本实验的关键。

先将要显示的每一幅图像画在一个16×16共256个小方格的矩形框中,再在有笔划下落处的小方格里填上“1”,无笔划处填上“0”,这样就形成了与这个汉字所对应的二进制数据在该矩形框上的分布以数字8为例,点阵分布为:0000000000000000000000000000000000011111111110000001111111111000000110000001100000011000000110000001100000011000000111111111100000011111111110000001100000011000000110000001100000011000000110000001111111111000000111111111100000000000000000000000000000000000考虑到实际物理实验平台上点阵发光二极管的原理,以下为16×16点阵LED外观图,只要其对应的X、Y轴顺向偏压,即可使LED 发亮。

例如如果想使左上角LED点亮,则Y0=1,X0=0即可。

所以我采用行列扫描的方法,用四位二进制数做列选信号(总共16列),如选中第一列,则扫描第一列之中哪些行是高电平(1),哪些行是低电平(0);为高电平的则点亮,为低电平的不亮。

(列信号都接地)。

如此,列选信号由“0000”变到“1111”时,16列扫描完毕,一个字也就出来了,列选信号重新由“0000”开始扫描。

注意扫描频率必须要足够快,才能保证显示一个数字或字母时所有灯在肉眼看来是同时在闪烁的。

(完整版)16×16点阵LED电子显示屏的设计_毕业论文

16×16点阵LED电子显示屏的设计摘要LED点阵显示屏作为一种新兴的显示器件,是由多个独立的LED发光二极管封装而成. LED点阵显示屏可以显示数字或符号, 通常用来显示时间、速度、系统状态等。

本设计是1616××16点阵LED电子显示屏的设计。

整机以美国ATMEL公司生产的40脚单片机AT89C51为核心,介绍了以它为控制系统的LED点阵电子显示屏的动态设计和开发过程。

通过该芯片控制一个行驱动器74LS154和两个列驱动器74L373来驱动显示屏显示。

该电子显示屏可以显示各种文字或单色图像,采用4块8 x 8点阵LED显示模块来组成一个16x16点阵显示模式。

显示采用动态显示,使得图形或文字能够实现静止、移入移出等多种显示方式。

文中详细介绍了LED点阵显示的硬件设计思路、硬件电路各个部分的功能及原理、相应软件的程序设计,以及使用说明等。

关键词:AT89C51单片机 LED 点阵显示动态显示AbstractAs a popular display device component, LED dot-matrix display board consists of several independent LED (Light Emitting Diode).The LED dot-matrix display board can display the number or sign,and it is usually used to show time, speed, the state of system etc.This design is 1 16 ×16 lattice LED electron display monitor design.The whole equipment is with the 40-pin AT89C51 MCU (Micro Controller Unit) produced by the American ATMEL company at thecore, introduced take it as the control system LED lattice electron display monitor dynamic design and the development process. Controls good driver 74LS154 an two row driver 74L373 through thischip actuates the display monitor demonstration. The electronic screen can show all kinds of written or monochrome images, one full screen display Chinese characters, four pieces of 8 x 8 dot-matrix LEDdisplay modules to form the 16x16 dot matrix display mode. Show dynamic show that makes static graphic or text can be achieved, shifted out of various formats. This paper describes the of the LEDdot matrix display, and the principle function of the various parts ofthe circuit, the corresponding software program design and the use of some such. Key words: AT89C51 Micro Controller U nitUnit; LED; LatticeDisplay;Dynamic Display目录第1章绪论1.1 选题背景LED显示屏是八十年代后期在全球迅速发展起来的新型信息显示媒体,显示屏由几万……几十万个半导体发光二极管像素点均匀排列组成。

EDA 16x16点阵显示.

课程设计报告课程名称数字系统与逻辑设计课题名称16*16点阵显示专业通信工程班级学号姓名指导教师乔汇东胡瑛2012年7月2日湖南工程学院课程设计任务书课程名称数字系统与逻辑设计课题16*16点阵显示专业班级通信工程1001班学生姓名学号指导老师乔汇东胡瑛审批乔汇东任务书下达日期2012 年6月23日任务完成日期2012 年7月2日《数字系统与逻辑设计》课程设计任务书一、设计目的全面熟悉、掌握VHDL语言基本知识,掌握利用VHDL语言对常用的的组合逻辑电路和时序逻辑电路编程,把编程和实际结合起来,熟悉编制和调试程序的技巧,掌握分析结果的若干有效方法,进一步提高上机动手能力,培养使用设计综合电路的能力,养成提供文档资料的习惯和规范编程的思想。

二、设计要求1、设计正确,方案合理。

2、程序精炼,结构清晰。

3、设计报告5000字以上,含程序设计说明,用户使用说明,源程序清单及程序框图。

4、上机演示。

5、有详细的文档。

文档中包括设计思路、设计仿真程序、仿真结果及相应的分析与结论。

三、进度安排第二十周星期一:课题讲解,查阅资料星期二:总体设计,详细设计星期三:编程,上机调试、修改程序星期四:上机调试、完善程序星期五:答辩星期六-星期天:撰写课程设计报告附:课程设计报告装订顺序:封面、任务书、目录、正文、评分、附件(A4大小的图纸及程序清单)。

正文的格式:一级标题用3号黑体,二级标题用四号宋体加粗,正文用小四号宋体;行距为22。

正文的内容:一、课题的主要功能;二、课题的功能模块的划分(要求画出模块图);三、主要功能的实现;四、系统调试与仿真;五、总结与体会;六、附件(所有程序的原代码,要求对程序写出必要的注释);七、评分表。

目录一. 16*16点阵显示的总体设计 (1)1.116*16点阵显示 (1)1.2基本设计思想 (1)二. 16*16点阵显示的功能实现 (3)2.1系统的总体框图 (3)2.2系统的流程图 (3)2.3系统各功能模块实现 (4)三.系统的调试与仿真 (8)四.总体与体会 (9)五附件 (10)六评分表 (16)一. 16*16点阵显示的总体设计1.1 16*16点阵显示本实验主要完成汉字字符在LED 上的显示,16*16 扫描LED 点阵的工作原理与8 位扫描数码管类似,只是显示的方式与结果不一样而已。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

三、实验效果分析(包过仪器设备等使用效果)

三、实验效果分析:

静态点阵RTL图形:

动态RTL仿真图形:

实验中程序一点阵里显示静态的师字,程序二中点阵显示的师字自右往左移动,说明实验程序正确。

字符显示的内容改变通过将要显示的数据取模,定制在ROM上,便可实验内容的改变,移动方向的改变将Q1<=Q1+1;改成Q1<=Q1-1;也就是将当前对应地址发生器的地址改为前一地址便可右移,改为后一地址便是左移,不变则静止。

教

师

评

语指导教师年月日

江西师范大学物理与通信电子学院

教学实验报告

专业:电子信息工程2011年5月11日

实验名称16×16点阵字符显示设计指导老师

姓名年级学号成绩

一、预习部分

1、实验目的

2、实验基本原理

3、主要仪器设备(包含必要的元器件、工具)

一、实验目的:

1.进一步熟悉QUARTUS‖及其LPM_ROM与FPGA硬件资源的使用方法。

2.学习和掌握16*16点阵字符显示设计方法。

二、实验基本原理:

利用不同的行抄描和列扫描,加上字取模软件对字取模,利用动态扫描便在点阵上看到了字。

二、主要仪器设备

电脑、实验箱

二、实验操作步骤

1.实验数据、表格及数据处理

2.实验操作过程(可以用图表示)

3.结论

1.实验数据、表格及数据处理如下:

library ieee; if rst='1'then

use ieee.std_logic_1164.all; qa<=(others=>'0');

use ieee.std_logic_unsigned.all; elsif clk'event and clk='1' then

entity sy12 is qa<=qa+1;

port(clk,rst:in std_logic; end if;

sel:out std_logic_vector(3 downto 0); end process;

dout:out std_logic_vector(15 downto 0)); process(qa,rst)

end ; begin

architecture one of sy12 is if rst='1' then

component data_rom q1<=(others=>'0');

port (address:in std_logic_vector(4 downto 0); elsif qa(10)'event and qa(10)='1' then inclock:in std_logic; q1<=q1+1; --当前所有地址改为对应的下一q:out std_logic_vector(15 downto 0)); end if; 地址,即整体左移end component; end process;

signal qa:std_logic_vector(10 downto 0); sel<=not(q0-2);

signal q0:std_logic_vector(3 downto 0); qq<=q1+q0;

signal qq:std_logic_vector(4 dow u1: data_rom port map(address=>qq,q=>dout,inclock=>clk); signal q1:std_logic_vector(4 downto 0); end;

begin

process(clk,rst)

begin

if rst='1' then

q0<=(others=>'0');

elsif clk'event and clk='1' then

q0<=q0+1;

end if ;

end process;

process(clk,rst)

begin 2、实验操作过程如下:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity sy11 is

port(clk,rst:in std_logic;

sel:out std_logic_vector(3 downto 0);

dout:out std_logic_vector(15 downto 0));

end ;

architecture one of sy11 is

component data_rom

port (address:in std_logic_vector(4 downto 0);

inclock:in std_logic;

q:out std_logic_vector(15 downto 0));

end component;

signal qq:std_logic_vector(4 downto 0);

signal q1:std_logic_vector(4 downto 0);

begin

process(clk,rst)

begin

if rst='1' then

q1<=(others=>'0');

elsif clk'event and clk='1' then

q1<=q1+1; end if ;

end process;

qq<=q1-1;

sel<=not qq(3 downto 0);

u1:data_rom port map(address=>q1,q=>dout,inclock=>clk); end;。