存储器原理及进展

动态存储器工作原理

动态存储器工作原理

动态存储器(DRAM)是计算机系统中常用的一种主存储器类型,其工作原理如下:

存储单元结构:

DRAM由许多存储单元组成,每个存储单元由一个电容器和一个晶体管组成。

电容器用于存储数据位,晶体管用于控制读取和写入操作。

电荷存储:

当电容器充电时,表示存储的是数据位1;电容器放电时,表示存储的是数据位0。

因此,电容器的充电状态表示了存储的数据。

数据读取:

当需要读取数据时,晶体管被打开,电荷从电容器流入读取线,通过放大和解码的过程,将电荷转换为电压信号,以供其他部件使用。

数据刷新:

由于电容器会逐渐失去电荷,需要定期刷新以保持数据的稳定性。

这是动态RAM(DRAM)与静态RAM(SRAM)的主要区别之一。

在刷新周期中,内存控制器会周期性地读取和重新写入所有存储单元,以更新其中的数据。

行选通和列选通:

DRAM中的存储单元被组织成行和列的结构。

在读取或写入特定单元时,首先需要选通相应的行和列。

行选通时,将特定行的数据放大并传递到输出线路上;列选通时,将输出线路上的数据发送给请求的设备。

预充电:

由于电容器的读取会导致电荷损失,需要在读取之前对其进行预充电操作,以确保准确读取数据。

总体而言,DRAM的工作原理是基于电容器的充放电来存储数据,通过晶体管控制数据的读取和写入操作,并通过周期性的刷新来维持数据的稳定性。

存储器的层次结构及组成原理

存储器的层次结构及组成原理一、引言存储器是计算机中非常重要的组成部分,它用于存储和读取数据。

随着计算机技术的发展,存储器也在不断地升级和改进。

存储器的层次结构是指不同类型的存储器按照速度、容量和成本等方面的差异被组织成一种层次结构。

本文将介绍存储器的层次结构及其组成原理。

二、存储器的层次结构1. 存储器分类根据存取速度不同,可将存储器分为主存(RAM)、高速缓存(Cache)、二级缓存、三级缓存等多级缓存以及辅助存储器(ROM、磁盘等)。

2. 层次结构主要分为三个层次:CPU内部高速缓冲寄存器(L1 Cache)、CPU外部高速缓冲寄存器(L2 Cache)和主内存(RAM)。

3. 层次结构优点层次结构能够充分利用各种类型的硬件设备,使得计算机系统能够更加高效地运行。

在执行指令时,CPU首先从最快的L1 Cache中查找数据,如果没有找到,则会查找L2 Cache,最后才会查找主内存。

这样的层次结构设计可以大大提高CPU访问数据的速度,减少CPU等待的时间。

三、存储器的组成原理1. 静态随机存取存储器(SRAM)SRAM是一种使用静电场来存储数据的存储器。

它由多个存储单元组成,每个单元由一个触发器和两个传输门组成。

SRAM的读写速度非常快,但是它比较昂贵,并且需要更多的电源。

2. 动态随机访问存储器(DRAM)DRAM是一种使用电容来存储数据的存储器。

它由多个存储单元组成,每个单元由一个电容和一个开关组成。

DRAM比SRAM更便宜,但是读写速度相对较慢。

3. 双倍数据率SDRAM(DDR SDRAM)DDR SDRAM是一种高速内存技术,可以在每个时钟周期传输两次数据。

这使得DDR SDRAM比普通SDRAM更快。

4. 图形双倍数据率SDRAM(GDDR SDRAM)GDDR SDRAM是一种专门为图形处理器设计的高速内存技术。

它具有更高的频率和带宽,适用于处理大量图像和视频数据。

5. 闪存闪存是一种非易失性存储器,可以在断电时保存数据。

(整理)铁电存储器工作原理及应用

铁电存储器工作原理及应用摘要:介绍铁电存储器(FRAM)的一般要领和基本原理,详细分析其读写操作过程及时序。

将FRAM与其它存储器进行比较,分析在不同场合中各自的优缺点。

最后以FM1808为例说明并行FPGA与8051系列单片机的实际接口,着重分析与使用一般SRAM的不同之处。

关键词:铁电存储器 FRAM原理 8051 存储技术1 背景铁电存储技术最在1921年提出,直到1993年美国Ramtron国际公司成功开发出第一个4Kb 的铁电存储器FRAM产品,目前所有的FRAM产品均由Ramtron公司制造或授权。

最近几年,FRAM又有新的发展,采用了0.35μm工艺,推出了3V产品,开发出“单管单容”存储单元的FRAM,最大密度可在256Kb。

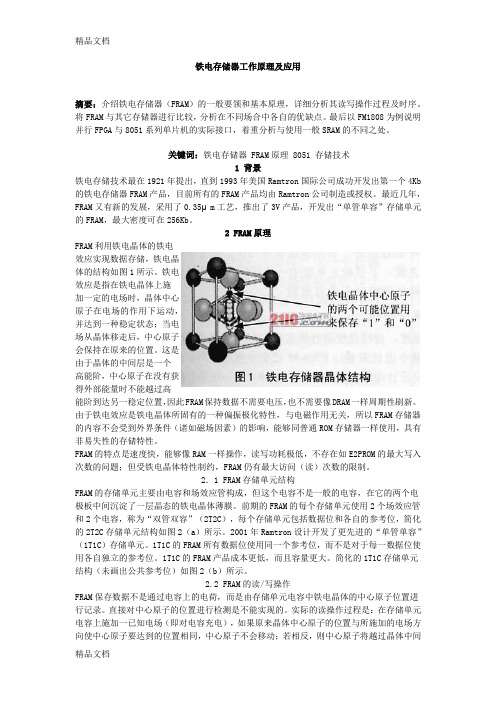

2 FRAM原理FRAM利用铁电晶体的铁电效应实现数据存储,铁电晶体的结构如图1所示。

铁电效应是指在铁电晶体上施加一定的电场时,晶体中心原子在电场的作用下运动,并达到一种稳定状态;当电场从晶体移走后,中心原子会保持在原来的位置。

这是由于晶体的中间层是一个高能阶,中心原子在没有获得外部能量时不能越过高能阶到达另一稳定位置,因此FRAM保持数据不需要电压,也不需要像DRAM一样周期性刷新。

由于铁电效应是铁电晶体所固有的一种偏振极化特性,与电磁作用无关,所以FRAM存储器的内容不会受到外界条件(诸如磁场因素)的影响,能够同普通ROM存储器一样使用,具有非易失性的存储特性。

FRAM的特点是速度快,能够像RAM一样操作,读写功耗极低,不存在如E2PROM的最大写入次数的问题;但受铁电晶体特性制约,FRAM仍有最大访问(读)次数的限制。

2.1 FRAM存储单元结构FRAM的存储单元主要由电容和场效应管构成,但这个电容不是一般的电容,在它的两个电极板中间沉淀了一层晶态的铁电晶体薄膜。

前期的FRAM的每个存储单元使用2个场效应管和2个电容,称为“双管双容”(2T2C),每个存储单元包括数据位和各自的参考位,简化的2T2C存储单元结构如图2(a)所示。

计算机组成原理实验之静态随机存储器实验

图1 存储器实验原理图1静态随机存储器实验一.实验目的掌握静态随机存储器RAM 工作特性及数据的读写方法。

二.实验设备1.TDN-CM+或TDN-CM++教学实验系统一台。

2.PC 微机(或示波器)一台。

三.实验原理实验所用的半导体静态存储器电路原理如图所示,实验中的静态存储器由一片6116 (2K ×8)构成,其数据线接至数据总线,地址线由地址锁存器(74LS273)给出。

地址灯AD0~AD7与地址线相连,显示地址线内容。

数据开关经一个三态门(74LS245)连至数据总线,分时给出地址和数据。

实验四图2 静态随机存储器实验接线图2 因地址寄存器为8位,所以接入6116的地址为A7~A0,而高三位A8~A10接地,所以其实际容量为256字节。

6116有三个控制线:CE (片选线)、OE (读线)、WE (写线)。

当片选有效(CE=0)时,OE=0时进行读操作,WE=0时进行写操作。

本实验中将OE 常接地,在此情况下,当CE=0、WE=0时进行读操作,CE=0、WE=1时进行写操作,其写时间与T3脉冲宽度一致。

实验时将T3脉冲接至实验板上时序电路模块的TS3相应插孔中,其脉冲宽度可调,其它电平控制信号由“SWITCH UNIT ”单元的二进制开关模拟,其中SW-B 为低电平有效,LDAR 为高电平有效。

四.实验步骤(1) 形成时钟脉冲信号T3。

具体接线方法和操作步骤如下:① 接通电源,用示波器接入方波信号源的输出插孔H23,调节电位器W1及W2 ,使H23端输出实验所期望的频率及占空比的方波。

② 将时序电路模块(STATE UNIT )单元中的ф和信号源单元(SIGNAL UNIT )中的H23排针相连。

③在时序电路模块中有两个二进制开关“STOP ”和“STEP ”。

将“STOP ”开关置为“RUN ”状态、“STEP ”开关置为“EXEC ”状态时,按动微动开关START ,则TS3端即输出为连续的方波信号,此时调节电位器W1,用示波器观察,使T3输出实验要 求的脉冲信号。

先进半导体存储器-结构、设计与应用__概述说明

先进半导体存储器-结构、设计与应用概述说明1. 引言1.1 概述随着信息技术的快速发展,存储器设备在计算机和移动设备等领域中扮演着至关重要的角色。

在过去的几十年里,人们开发了各种类型的存储器,其中最为先进和广泛应用的是半导体存储器。

半导体存储器以其快速读写操作、高密度数据存储和较低功耗的优势成为主流技术。

1.2 文章结构本文将对先进半导体存储器的结构、设计与应用进行全面深入地探讨。

首先,我们将介绍先进半导体存储器的基本原理和发展历程,包括其在计算机系统中的主要类别和性能指标。

然后,我们将重点探讨先进半导体存储器在计算机系统中主存和缓存系统中的应用以及其在移动设备和云计算中的应用。

此外,我们还将探讨未来先进半导体存储器发展方向及挑战,并分析微细加工技术对其造成的影响与挑战。

最后,在结论部分对该论题进行总结,并展望先进半导体存储器的未来发展方向和挑战。

1.3 目的本文旨在通过对先进半导体存储器的结构、设计与应用进行全面分析,帮助读者深入了解该领域的最新进展和技术趋势。

文章将从基础原理入手,详细介绍各种先进半导体存储器的类型、特点和性能指标,并探讨其在计算机系统中的广泛应用。

此外,文章还将关注微细加工技术对先进半导体存储器的影响和挑战,并展望该技术领域的未来发展方向。

通过阅读本文,读者将深入了解现代存储器技术的发展趋势,为相关研究和应用提供参考依据。

2. 先进半导体存储器的结构与设计2.1 先进半导体存储器的基本原理先进半导体存储器是一种利用电子场效应管和电容来实现数据存储的半导体器件。

它通常由晶体管和电容构成,其中晶体管用于控制电荷在电容中的流动以实现数据的存取。

基本存储单元包括位线、字线、感应线和电容,通过调整位线、字线和感应线上的电势,并利用晶体管对数据进行读写操作。

2.2 先进半导体存储器的发展历程先进半导体存储器起源于上世纪60年代,经历了多个阶段的技术演进。

最初的静态随机访问存储器(SRAM)采用双稳态触发器作为基本单元,具有快速读写速度和较高可靠性。

单片机存储的原理及应用

单片机存储的原理及应用1. 介绍单片机(Microcontroller Unit,简称MCU)是一种集成了微处理器、内存、输入输出设备和时钟等功能于一体的集成电路芯片。

在单片机中,存储器是其核心组成部分之一,它用于存储程序代码、数据和临时结果。

本文将介绍单片机存储的原理及应用。

2. 单片机存储的原理在单片机中,存储器主要分为两种类型:程序存储器和数据存储器。

2.1 程序存储器程序存储器,也称为只读存储器(Read-Only Memory,简称ROM),用于存储程序代码。

ROM中存储的程序代码是在制造过程中被固化在芯片中的,无法被修改。

常见的ROM类型包括:•ROM:只读存储器,程序代码在制造过程中被固化,无法修改。

•PROM:可编程只读存储器,程序代码在制造过程后,使用特殊设备进行编程,一次性写入。

•EPROM:可擦写可编程只读存储器,通过紫外线照射来擦除存储的数据,然后使用特殊设备进行编程。

•EEPROM:可擦写可编程电可修改只读存储器,擦写和编程可以通过电气方式进行。

2.2 数据存储器数据存储器用于存储程序中使用的变量、常量和临时结果等数据。

数据存储器通常包括随机存储器(Random-Access Memory,简称RAM)和非易失性存储器(Non-Volatile Memory,简称NVM)两种类型。

•RAM:随机存储器,数据可以随机读写,但是断电后会丢失。

RAM 分为静态随机存储器(SRAM)和动态随机存储器(DRAM)两种类型。

•NVM:非易失性存储器,数据断电后不会丢失。

NVM包括闪存(Flash)、磁盘等多种形式。

3. 单片机存储的应用单片机存储器在各个领域都有广泛的应用,下面列举了一些常见的应用场景:3.1 嵌入式系统单片机广泛应用于嵌入式系统中。

嵌入式系统通常需要处理实时任务,如控制器、仪表盘、自动化设备等。

单片机通过程序存储器存储系统的控制程序,通过数据存储器存储实时数据,实现系统的功能。

计算机组成原理实验报告,存储器的原理及应用

初:未知 当前:2016-7-3 主笔:Angel 联系方式:QQ :1219818801 版本:1实 验 报 告课程名称: 计算机组成原理 实验项目: 存储器的原理及应用姓 名: 刘斌专 业: 计算机科学与技术 班 级: 计算机14-6班 学 号:1404010612计算机科学与技术学院实验教学中心2016 年 6 月 20日初:未知当前:2016-7-3 主笔:Angel 联系方式:QQ:1219818801 版本:1实验项目名称:存储器的原理及应用一、实验目的1.了解程序存储器EM 的工作原理及控制方法2.了解存储器读写方法。

二、实验内容利用 COP2000 实验仪上的 K16..K23 开关做为 DBUS 的数据,其它开关做为控制信号,实现程序存储器EM 的读写操作。

三、实验用设备仪器及材料计算机、伟福 COP2000系列计算机组成原理实验系统四、实验原理及接线内存中通常存放指令和数据,当内存存放指令时,将指令送指令总线;当内存存放数据时,将数据送数据总线。

如图所示,它主要由一片RAM 6116 组成,RAM6116是静态2048X8位的RAM,有11 条地址线,在COP2000 模型机中只使用8 条地址线A0-A7 ,而A8-A10接地。

存储器EM通过1片74HC245 与数据总线相连。

存储器EM的地址可由PC或MAR提供。

存储器EM 的数据输出直接接到指令总线IBUS,指令总线IBUS 的数据还可以来自一片74HC245。

当ICOE 为0 时,这片74HC245 输出中断指令B8。

EM原理图初:未知当前:2016-7-3 主笔:Angel 联系方式:QQ:1219818801 版本:12存储器 uM 由三片 6116RAM 构成,共 24 位微指令。

存储器的地址由 uPC 提供, 片选及读信号恒为低, 写信号恒为高. 存储器uM 始终输出uPC 指定地址单元的数据。

连接线表五、实验操作步骤1, 1、控制 k4、k5开关,观察PC\MAR输出地址选择:1、K5、输出地址(PC红色灯亮)2、K5、输出地址(PC红色灯亮)2、K5、没有灯亮2、K5、、PC同时输出地址(MAR、PC红色灯同时亮)2、存储器EM 写、读实验(1)将地址 0写入MAR二进制开关K23-K16 用于DBUS[7:0]的数据输入,置数据00HK3连接MAREN端,当低电平(0)时,MAR写允许按CLOCK键, 将地址 0 写入MAR(2)将数据11H写入地址00H二进制开关K23-K16 用于DBUS[7:0]的数据输入,置数据11HK4连接MAROE,当低电平(0)时,MAR输出地址K2连接EEMEN,当低电平(0)时,存储器与数据总线连接K0连接EMWR,当低电平(0)时,存储器写允许按CLOCK键, 将地址11H写入EM(3)读地址00H 中的数据11HK4连接MAROE,,MAR输出地址K1连接EMRD,当低电平(0)时,存储器读允许学生做:将数据55H写入地址22H,并读出将数据45H写入地址33H,并读出3、将数据打入地址为00的IR 指令寄存器/uPC实验(1)将地址 0写入MAR二进制开关K23-K16 用于DBUS[7:0]的数据输入,置数据00HK3连接MAREN端,当低电平(0)时,MAR写允许按CLOCK键, 将地址 0 写入MAR(2)将数据11H写入地址00H二进制开关K23-K16 用于DBUS[7:0]的数据输入,置数据11HK4连接MAROE,当低电平(0)时,MAR输出地址K2连接EEMEN,当低电平(0)时,存储器与数据总线连接K0连接EMWR,当低电平(0)时,存储器写允许按CLOCK键, 将地址11H写入EM(3)读地址00H 中的数据11HK4连接MAROE,,MAR输出地址K1连接EMRD,当低电平(0)时,存储器读允许(4)写地址00H数据11H入 IR及 uPC学生做:将数据22H、33H打入地址为01H、02H的IR 指令寄存器/uPC实验实验 1:微程序存储器 uM 读出置控制信号为:K0为1uM 输出uM[0]的数据按一次CLOCK脉冲键,CLOCK产生一个上升沿,数据uPC 被加一。

存储器的基本原理及分类

存储器的基本原理及分类存储器是计算机中非常重要的组成部分之一,其功能是用于存储和读取数据。

本文将介绍存储器的基本原理以及常见的分类。

一、基本原理存储器的基本原理是利用电子元件的导电特性实现数据的存储和读取。

具体来说,存储器通过在电子元件中存储和读取电荷来实现数据的储存和检索。

常见的存储器技术包括静态随机存取存储器(SRAM)和动态随机存取存储器(DRAM)。

1. 静态随机存取存储器(SRAM)静态随机存取存储器是一种使用触发器(flip-flop)来存储数据的存储器。

它的特点是不需要刷新操作,读写速度快,但容量较小且功耗较高。

SRAM常用于高速缓存等需要快速读写操作的应用场景。

2. 动态随机存取存储器(DRAM)动态随机存取存储器是一种使用电容来存储数据的存储器。

它的特点是容量大,但需要定期刷新以保持数据的有效性。

DRAM相对SRAM而言读写速度较慢,功耗较低,常用于主存储器等容量要求较高的应用场景。

二、分类根据存储器的功能和使用方式,可以将存储器分为主存储器和辅助存储器两大类。

1. 主存储器主存储器是计算机中与CPU直接交互的存储器,用于存储正在执行和待执行的程序以及相关数据。

主存储器通常使用DRAM实现,是计算机的核心部件之一。

根据存储器的访问方式,主存储器可分为随机存取存储器(RAM)和只读存储器(ROM)两种。

- 随机存取存储器(RAM)随机存取存储器是一种能够任意读写数据的存储器,其中包括SRAM和DRAM。

RAM具有高速读写的特点,在计算机系统中起到临时存储数据的作用。

- 只读存储器(ROM)只读存储器是一种只能读取数据而不能写入数据的存储器。

ROM 内部存储了永久性的程序和数据,不随断电而丢失,常用于存储计算机系统的固件、基本输入输出系统(BIOS)等。

2. 辅助存储器辅助存储器是计算机中用于长期存储数据和程序的设备,如硬盘、固态硬盘等。

与主存储器相比,辅助存储器容量大、价格相对低廉,但读写速度较慢。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

半导体存储器基本原理与最新研究进展微电子学研究所许军2007年9月5日主要内容•半导体存储器概述;•半导体存储器的分类与基本架构;•半导体存储器的主要技术指标;•半导体存储器的基本原理;•半导体存储器的最新进展。

半导体存储器概述Semiconductor Memory MarketMemory In Your Hands Today(~2007)Memory In Your Hands In The Future(~2010)ARB Core Die shot of SoftFone Chip w/ embedded DSP coreBasic Memory Types“FLASH”Attributes of An Ideal Memory1.Non-volatility(不挥发)2.High density (small volume/bit)(高密度)3.Low power consumption(低功耗)4.In-system re-writability(可重写)5.Bit alterability (bit-writable)(按位可写)6.Direct overwrite without prior erase(可直接覆盖重写)7.Fast read/write/erase(快速读写擦)8.Endurance (high write/erase cycles)(耐久性)9.Low cost(低成本)10.Single (low) power supply(单电源、低电压)11.Scalable(可等比例缩小)12.Reliability(可靠性)13.Integrable with other system technologies(可集成)Technology Trend半导体存储器的分类与基本架构半导体存储器的分类:•挥发性存储器(易失性存储器)Volatile Memories (SRAM, DRAM)•不挥发性存储器(非易失性存储器)Non-Volatile Memories (ROMs, EPROMs, EEPROMs, Flash, FeRAM, MRAM)半导体存储器的分类与基本架构半导体存储器的基本架构:•存储单元矩阵(Memory cell array)•外围电路(Peripheral circuits)地址译码电路(行地址译码器、列行地址译码器等)数据读写电路(读出放大器、灵敏/恢复放大器等)时序控制电路(包括各种时钟电路等)衬偏发生器电路(包括其它高压产生电路等)Memory Chip ConfigurationRow and Column DecodersOne dimensional Two dimensional A matrix arrangement reduces the number of drivers from 2N+M to 2N+2MConcept of Feature Size (F)Memory Cell Area•Memory cell size is usually measured in number of F2•The cross-point memory array achieves the theoretical minimum area of 4F2•Typical values:–DRAM: 6 –8 F2–SRAM: 100 –120 F2–NOR FLASH: 8 –10 F2–NAND FLASH: 4 –6 F2•But…F2does not tell the whole story about cell size (and therefore chip size)•Array efficiency needs to be included–Area occupied by address decoders–Sense amplifiers–Array partitioning for speed–Charge pumps for higher voltages on-chipDevice Scaling Works!•Array efficiency ~60%64Mb DRAM300 nm technology2Gb DRAM80 nm technologyExample DRAM Chips•2X increase in area, 4X increase in capacity •Typical trend: feature size shrinkage plus chip size increase per generation半导体存储器的主要技术指标•半导体存储器的容量(与存储单元的结构、芯片面积以及制造工艺密切相关)•半导体存储器的存取时间(与存储器的总体架构、存储单元的电路结构以及芯片的制造工艺等密切相关)•半导体存储器的功耗(同样也与存储器的总体架构、存储单元的电路结构以及芯片的制造工艺等密切相关)1. 只读存储器ROM(Read Only Memory)•这里主要是指各种Mask ROM, 其中所存储的数据已在硅晶园片制作时完全确定。

•在电路的使用过程中,存储的数据只能读出而不能重新写入。

•用途:各种固化的微控制程序(微指令)以及计算器(函数表)芯片,各种固化的语音(音乐)芯片等。

•存储单元与存储矩阵存储矩阵:由字线、位线确定单元位置;数据由位线读出:单元存1,读出高电平单元存0,读出低电平单元由字线经地址译码选取:选定单元的子线W为高电平,其余字线则皆为低电平;未选中单元对位线的读出将不起作用。

列选电路:•存储的数据可能一次只要求读出8位(1 byte)•而存储器的容量往往很大,例如64Kbit(=8位×8K字),由此形成的窄长条形存储矩阵非常不合理•改进办法:将存储矩阵改为256行×256列•这样一来,每根位线要读出32列存储单元所存储的数据•因此必须采用列选线控制的传输门来选择所需要读出的列地址译码器-用于选择字线和列选线:•通常包括行译码器和列译码器•64行选需要6位地址(26=64)•8根列选需要3位地址(23=8)•对于存储容量比较大的存储器,例如256Mbit 16位输出的存储器,则需要24位地址,在这种情况下为了减少芯片封装所需的管腿数目,地址信号也可以采用分时输入的方式,此时则需要相应的地址分时缓冲电路串联式ROM结构:•上述ROM结构,每条位线上的各个MOS晶体管是并联型的,即或非逻辑结构(NOR),其优点是读出速度比较快;•但是此时需要采用专门的引线将各个MOS晶体管的漏端(位线)、源端(地线)分别相连,相应地要开许多接触孔,由此导致每个存储单元的面积比较大;•在读出速度要求不太高的情况下,可以采用将各个存储MOS晶体管相串联的形式,即串联型的与非逻辑结构(NAND)。

•此时最下面MOS晶体管的源端为地线,最上面MOS 晶体管的漏端为位线,因此不需要采用专门的引线来将各MOS晶体管相连接,也不需要开很多接触孔,从而大大减小单元面积。

•在串联型存储阵列中,E型MOS晶体管存储的数据为“1”,而D型MOS晶体管则存储“0”;•字选采用负逻辑,选中的字线才为低电平,其它未选中的字线则皆为高电平;•未选中的单元,不论其存“1”还是存“0”,对应的MOS晶体管皆导通,即不起作用;•列选仍然采用正逻辑,即选中为高电平,因此列选管导通,选中的列接地,其余未选中的列则与地断开悬空,这些列上的各存储单元所存储的数据将不起作用。

对于被选中行、列的单元:•如果单元存“1”(E管),则位线将输出高电平;•如果单元存“0”(D管),则位线将输出低电平。

2. 可编程只读存储器PROM(Programmable ROM)•Mask ROM的芯片面积比较小,生产成本最低,工作速度也比较快;•但是只适合于大批量的生产和应用,否则一次性的投入太大,开发周期也相对比较长;•因此非常需要一种可以由用户自己来进行编程的ROM,即PROM;•最早的PROM实际上就是采用熔断丝编程的ROM,也就是由用户自己寻址将专门设计的熔丝烧断来确定ROM中存储的内容;•早先是双极型的,后来也有MOS型的,通常都是采用较细的多晶硅线条来制作熔断丝;•显然,这种PROM只能进行一次编程,而且不能进行改写。

目前还在使用的可编程ROM,大部分是可以进行擦除重写的,主要有三种常用的类型:•EPROM(Erasable PROM):通常采用紫外线照射来进行擦除操作;•EEPROM(E2PROM,Electrical Erasable PROM):采用电学方法来进行按位的擦除操作;•Flash Memory(快闪存储器):采用电学方法,按块进行快速擦除操作;•而PROM目前则专指那些只能进行编程而不能改写的ROM,这些PROM与Mask ROM共同特点是擦写的速度比较慢(读出的速度通常并不慢)•尽管各种可擦除PROM的擦写速度在不断提高,从EPROM的几十分钟,到E2PROM的几十毫秒(ms),再到Flash Memory的几十微秒(μs),但是仍比DRAM几十纳秒(ns)的写入速度要慢得多,更不用说与SRAM相比了。

•写入前:浮栅管不导通(V T>V DD),相当于单元存储信息为“0”,此时PMOS电路输出为低电平;•写入时:在漏端加高反向电压,使PN结发生雪崩击穿,大量高能电子注入到浮栅中,使得浮栅管VT 变正,浮栅管开始导通,相当于单元存储信息为“1”,此时PMOS电路输出为高电平;•擦除时:采用深紫外光(λ≈250nm, hυ≈4.9eV )来激发浮栅上的电子,使其在浮栅自身负电荷电场作用下,越过SiO2势垒而回到硅衬底中。

•特点:写入时,浮栅电位接近于0,而漏端要加很高的反向击穿电压,此电压为负高压,以利于电子向浮栅中的注入。

半导体存储器的基本原理•写入前:VT正常,单元存“0”,NMOS器件输出为低电平;•写入时:在器件漏端加一高电压,使选通管中产生沟道热载流子,高能电子向浮栅中注入,使叠栅管的VT 提高,直至VT >VDD,从而实现写入“1”操作;•擦除:仍然是采用紫外光照射擦除,SIMOS的特点(与FAMOS的不同之处):•写入前器件的VT正常,否则无法实现选通编程;•写入时电子注入浮栅使叠栅管的VT 变正(升高),因此需要采用NMOS器件(而不能像FAMOS那样采用PMOS器件);•器件漏端加的是正电压,但是不能太高,否则不利于高能电子向浮栅中的注入,不能靠PN结雪崩击穿,而需要利用沟道热载流子的注入;•热载流子注入之所以可能,因为器件沟道尺寸缩短;•单元面积比较小,NMOS器件工作速度快。