大连理工大学计算机系统结构实验-实验四

大连理工大学计算机网络实验报告

大连理工大学本科实验报告课程名称:计算机网络实验学院(系):电信学部专业:自动化班级:学号:学生姓名:2014年11月23日大连理工大学实验预习报告学院(系):专业:班级:姓名:学号:组:___实验时间:实验室:实验台:指导教师签字:成绩:实验一:网络硬件环境准备实验一、实验目的和要求准备计算机网络实验所用到的计算机、网络设备和工具。

二、实验设备1.网络传输介质在网络中,信息是通过传输介质来传送的,常用的网络传输介质有三种:①金属导体,用电流变化传输信息。

如同轴电缆、双绞线等。

②光纤,用光波传输信息。

如透明玻璃为介质。

③不需要物理连接,用电磁波的辐射传输信息。

如无线电、微波、卫星等。

本实验采用超5类非屏蔽双绞线(UTP)做网络传输介质进行网络连接,最高数据传输速率是100Mbps。

双绞线具有抗干扰性能好、布线方便、价格低、全双工的特点。

适用于较短距离的电话系统和局域网系统。

2.网卡网络接口卡(NIC)也被称为网络适配器,是一种连接设备。

它能够使工作站、服务器、打印机或其他节点通过网络传输介质接收并发送数据。

首先要给PC机装上网卡,打开机箱,把网卡插在白色的PCI插槽里;然后开机,装上驱动程序;网络传输介质的连接器(如双绞线的RJ-45连接器)插入网卡的连接器接口。

三、实验内容制作实验用的双绞线制作两端使用EIA/TIA568B同一标准的正线。

大连理工大学实验报告学院(系):专业:班级:姓名:学号:组:___实验时间:实验室:实验台:指导教师签字:成绩:实验一:网络硬件环境准备实验一、实验目的和要求见预习报告二、实验原理和内容见预习报告三、主要仪器设备双绞线,网线头,电缆测试仪子母机,钳子。

四、实验步骤与操作方法1.制作实验用的双绞线;制作两端使用EIA/TIA568B同一标准的正线。

2.按照线色排好理直、剪齐,能清楚的看到8个线头整齐的顶到最前位置,套管推过止口位置;然后压紧。

3.逐根线检测五、实验结果与分析根据电缆测试仪子母机显示情况,制作一根八根线全部正常的网线六、讨论、建议、质疑大连理工大学实验预习报告学院(系):专业:班级:姓名:学号:组:___实验时间:实验室:实验台:指导教师签字:成绩:实验二:对等网络的建立实验一、实验目的和要求对于电脑数量不多、网络的安全性要求不高的局域网来说,拿出一台独立的电脑来做服务器是比较浪费的,可以采用对等式的网络结构。

大连理工大学计算机原理实验综合实验设计报告

4.编写与中断相关的程序。包括中断屏蔽字的设定,开放 IR5 中断,中断向量表的 创建以及开中断的操作。

5.编写中断服务程序 ISR。在 ISR 中读取 D8255A 的 PA 口数据,然后进行数据分析, PA7(与 K7 对应)位的数据为步进电机的转向控制;PA1—PA6(与 D1—D6 对应)为电 位器控制转速,ADC0809 将电位器的模拟量转换为数字量,其结果为步进电机的转速 控制;PA0 接 8253 的 CLK1。

buf db 33h

speed db 0

dir db 0

data ends

ssg segment stack dw 100 dup(0)

ssg ends

code segment

assume cs:code,ds:data,ss:ssg

main proc far

cli

mov ax,cs

mov ds,ax

;支路 5s ;延时 1s ;PA0=1 时,循环

5. 在中断服务程序中实现对步进电机的转速、转向实时控制,同时判断交通灯是 否出现“紧急通行”呼叫信号。分别使用两个单脉冲的输出(正的脉冲数出)与 MIR5 与 SIR0 连接,作为“南北”和“东西”人行横道的“紧急通行”呼叫信号。

2 设计分析及系统方案设计

1.首先参照实验教材第三章 3.1.3 的相关内容,将步进电机运转起来。原有的参考程 序中使用的是“输出立即数”方式来输出步进电机的相序,将其修改为:将初始相序存 放在一个寄存器中(原始相序数据位 33H),然后利用对该寄存器“移位”的方式产生 下一个相序。其中对寄存器中的数据移位方向决定着电机旋转地方向。

计算机系统结构实验报告

计算机系统结构实验报告实验目的:掌握计算机系统的基本结构和工作原理,了解计算机系统的组成部分及其相互关系。

实验仪器和材料:计算机硬件设备(主机、硬盘、内存、显卡等)、操作系统、实验指导书、实验报告模板。

实验原理:实验步骤:1.搭建计算机硬件设备,将主机、硬盘、内存、显卡等组装连接好。

2. 安装操作系统,如Windows、Linux等。

3.启动计算机,进入操作系统界面。

4.打开任务管理器,查看CPU的使用情况。

5.打开任务管理器,查看内存的使用情况。

6.运行一些应用程序,观察CPU和内存的使用情况。

7.尝试使用输入输出设备,如键盘、鼠标等。

实验结果:通过实验,我们可以观察到计算机系统的硬件部分和软件部分的工作情况。

通过任务管理器,我们可以查看到CPU的使用情况和内存的使用情况。

在运行应用程序时,我们可以观察到CPU和内存的使用情况的变化。

通过使用输入输出设备,我们可以与计算机进行交互操作。

实验分析:从实验结果可以看出,计算机系统的硬件部分和软件部分都是相互关联的。

CPU作为计算机的核心部件,负责执行各种指令,通过数据传输和计算来完成各种操作。

而内存则用于存储数据和程序,通过读写操作来完成对数据的处理。

硬盘则用于长期存储数据。

操作系统则是计算机系统的管理者,通过调度CPU和内存的使用来实现对计算机资源的分配。

结论:计算机系统是由硬件和软件部分组成的,其中硬件部分包括CPU、内存、硬盘等,软件部分包括操作系统、应用程序等。

计算机系统通过CPU 的运算和数据传输来实现各种操作。

通过实验,我们可以观察到计算机系统的工作情况,并深入了解计算机系统的组成和工作原理。

实验总结:通过本次实验,我们对计算机系统的基本结构和工作原理有了更深入的了解。

实验中,我们搭建了计算机硬件设备,安装了操作系统,并通过观察和分析实验结果,进一步认识到计算机系统的组成部分和各部分之间的相互关系。

通过操作输入输出设备,我们还实践了与计算机进行交互操作的过程。

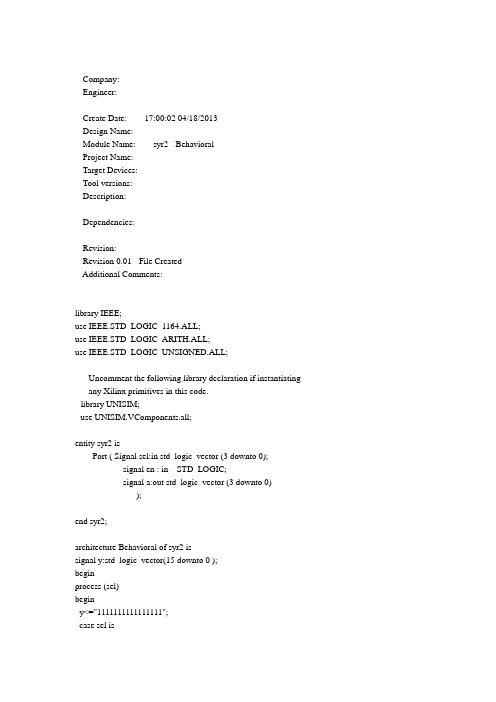

大连理工大学软件学院计算机组成原理实验4-16译码器VHDL语言实现

---------------------------------------------------------------------------------- -- Company:-- Engineer:---- Create Date: 17:00:02 04/18/2013-- Design Name:-- Module Name: syr2 - Behavioral-- Project Name:-- Target Devices:-- Tool versions:-- Description:---- Dependencies:---- Revision:-- Revision 0.01 - File Created-- Additional Comments:------------------------------------------------------------------------------------ library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;---- Uncomment the following library declaration if instantiating---- any Xilinx primitives in this code.--library UNISIM;--use UNISIM.VComponents.all;entity syr2 isPort ( Signal sel:in std_logic_vector (3 downto 0);signal en : in STD_LOGIC;signal a:out std_logic_vector (3 downto 0));end syr2;architecture Behavioral of syr2 issignal y:std_logic_vector(15 downto 0 );beginprocess (sel)beginy<="1111111111111111";case sel iswhen "0000" =>y (0) <='0';when "0001" =>y (1) <='0';when "0010" =>y (2) <='0';when "0011" =>y (3) <='0';when "0100" =>y (4) <='0';when "0101" =>y (5) <='0';when "0110" =>y (6) <='0';when "0111" =>y (7) <='0';when "1000" =>y (8) <='0';when "1001" =>y (9) <='0';when "1010" =>y (10) <='0';when "1011" =>y (11) <='0';when "1100" =>y (12) <='0';when "1101" =>y (13) <='0';when "1110" =>y (14) <='0';when others =>y (15) <='0';end case;end process;a(3) <=not (y(15));a(2) <=not (y(10) and y(11) and y(14));a(1) <=not (y(6) and y(7) and y(9) and y(11) and y(13) and y(14)); a(0) <=not (y(5) and y(7) and y(13) and y(15));end Behavioral;---------------------------------------------------------------------------------- -- Company:-- Engineer:---- Create Date: 18:35:51 04/08/2013-- Design Name:-- Module Name: testss - Behavioral-- Project Name:-- Target Devices:-- Tool versions:-- Description:---- Dependencies:---- Revision:-- Revision 0.01 - File Created-- Additional Comments:------------------------------------------------------------------------------------ library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;---- Uncomment the following library declaration if instantiating ---- any Xilinx primitives in this code.--library UNISIM;--use UNISIM.VComponents.all;entity testss isPort (a,b,c : in STD_LOGIC;s : out STD_LOGIC);end testss;architecture Behavioral of testss issignal x,y:std_logic;beginx <= a nand b;y <= (b nand c) and x;s <= not(x and y);end Behavioral;。

大连理工大学计算机原理实验报告

目录1 实验任务 (1)2 设计方案 (1)3 设计电路 (3)4设计程序 (5)5 遇到的问题 (2)(1)程序语法方面 (2)(2)运行逻辑方面 (2)(3)软件使用方面 (2)6 何解决问题 (2)(1)程序语法方面 (2)1)寄存器使用时,数据类型不匹配: (2)2)程序越来越大的时候,程序结构混乱: (2)3)基本操作的要求: (3)4)对于中断服务程序、堆栈段以及中断STI指令的理解: (3)(2)运行逻辑方面 (3)1)电梯加速减速在一楼到二楼的特殊情况的考虑问题: (3)2)电梯运行方式的确定问题: (4)3)电梯连续运行时,各种参数的转换问题: (5)4)对于电梯实时运行显示的显示逻辑问题: (5)(3)软件使用方面 (5)1)在使用软件的时候,对于软件设置断点,以及使用断点的问题: (5)2)在软件使用中,经常出现的USB端口缺失,以及软件程序不能发送到实验板中的问题: (6)7 实验体会 (6)1 实验任务本次实验通过汇编语言编程,基本实现电梯的功能:通过在实验板的8位开关进行选择需要到的楼层,步进电机进行旋转,250个脉冲为一层,即电机旋转5.2圈为一层,每次启动,电机由速度为0加速启动,加速到最大速度时,正好达到二楼。

到达目的楼层之前,在距离楼层半层时开始减速,准确到达楼层时停止转动。

其中,当运动为一层时,电梯仅仅加速到最大速度的一半,然后减速,到达目的楼层。

在每次到达目的楼层之后,继续修改目的楼层,可以连续工作。

在工作的过程中,通过数码管实时显示当前的楼层,同时通过LED灯也实时显示楼层情况。

2 设计方案(1)电梯电机驱动部分通过地址200H选中8254定时器芯片,使用定时器0和定时器1对实验板上的1MHz脉冲信号进行分频,通过两个定时器进行分频,之后out1给中断控制器8259,触发中断,在中断中进行参数spnum的自加,在通过这个变量的数值大小与主程序speed的比较来决定主程序是否对步进电机发出相序信号,使其开始转动。

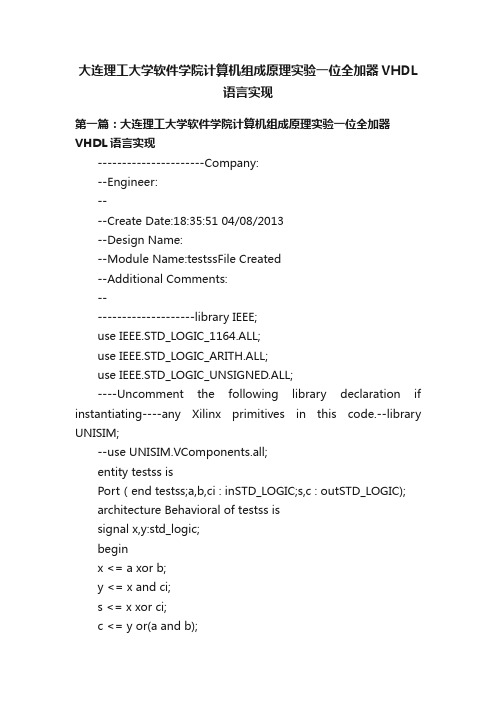

大连理工大学软件学院计算机组成原理实验一位全加器VHDL语言实现

大连理工大学软件学院计算机组成原理实验一位全加器VHDL语言实现第一篇:大连理工大学软件学院计算机组成原理实验一位全加器VHDL语言实现----------------------Company:--Engineer:----Create Date:18:35:51 04/08/2013--Design Name:--Module Name:testssFile Created--Additional Comments:----------------------library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;----Uncomment the following library declaration if instantiating----any Xilinx primitives in this code.--library UNISIM;--use UNISIM.VComponents.all;entity testss isPort(end testss;a,b,ci : inSTD_LOGIC;s,c : outSTD_LOGIC);architecture Behavioral of testss issignal x,y:std_logic;beginx <= a xor b;y <= x and ci;s <= x xor ci;c <= y or(a and b);end Behavioral;第二篇:计算机组成原理实验ALU设计module ALU(ALU_OP,AB_SW,F_LED_SW,LED);input[2:0] ALU_OP,AB_SW,F_LED_SW;output[7:0] LED;reg[7:0] LED;reg[31:0] A,B,F;reg OF,ZF;always@(*)beginendalways@(*)beginZF=0;OF=0;case(ALU_OP)3'b000: begin F=A&B;end 3'b001: begin F=A|B;end 3'b010: begin F=A^B;end 3'b011: begin F=~(A|B);end 3'b100: begin {OF,F}=A+B;OF=OF^F[31];end 3'b101: begin {OF,F}=A-B;OF=OF^F[31];end 3'b110: begin F=A3'b000: begin A=32'h0000_0000;B=32'h0000_0000;end 3'b001: begin A=32'h0000_0003;B=32'h0000_0607;end 3'b010: begin A=32'h8000_0000;B=32'h8000_0000;end 3'b011: begin A=32'h7FFF_FFFF;B=32'h7FFF_FFFF;end 3'b100: begin A=32'h8000_0000;B=32'hFFFF_FFFF;end 3'b101: begin A=32'hFFFF_FFFF;B=32'h8000_0000;end 3'b110: begin A=32'h1234_5678;B=32'h3333_2222;end 3'b111: begin A=32'h9ABC_DEF0;B=32'h1111_2222;end endcase endcase if(F==32'b0)ZF=1;endalways@(*)beginend case(F_LED_SW)3'b000: LED=F[7:0];3'b001: LED=F[15:8];3'b010: LED=F[23:16];3'b011: LED=F[31:24];default:begin LED[7]=ZF;LED[0]=OF;LED[6:1]=6'b0;end endcaseendmodule 管脚配置NET “AB_SW[0]” LOC = T10;NET “AB_SW[1]” LOC = T9;NET “AB_SW[2]” LOC = V9;NET “ALU_OP[0]” LOC = M8;NET “ALU_OP[1]” LOC = N8;NET “ALU_OP[2]” LOC = U8;NET “F_LED_SW[0]” LOC = V8;NET “F_LED_SW[1]” LOC = T5;NET “F_LED_SW[2]” LOC = B8;NET “LED[0]” LOC = U16;NET “LED[1]” LOC = V16;NET “LED[2]” LOC = U15;NET “LED[3]” LOC = V15;NET “LED[4]” LOC = M11;NET “LED[5]” LOC = N11;NET “LED[6]” LOC = R11;NET “LED[7]” LOC = T11;寄存器 module jicunqi(input Clk, input Reset, input [4:0] Reg_Addr, input Write_Reg, input [1:0] Sel, input AB, output reg [7:0] LED);reg [31:0] W_Data;wire [31:0] R_Data_A,R_Data_B,LED_Data;REGRU1(Clk,Reset,Reg_Addr,Reg_Addr,Reg_Addr,W_Data,Write_Reg,R_Data_A,R_Data_B);assign LED_Data=AB?R_Data_A : R_Data_B;always @(*)beginW_Data=32'h0000_0000;LED=8'b0000_0000;if(Write_Reg)begincase(Sel)2'b00: W_Data= 32'h1234_5678;2'b01: W_Data= 32'h89AB_CDEF;2'b10: W_Data= 32'h7FFF_FFFF;2'b11: W_Data= 32'hFFFF_FFFF;endcase end elsebegincase(Sel)2'b00: LED=LED_Data[7:0];2'b01: LED=LED_Data[15:8];2'b10: LED=LED_Data[23:16];2'b11: LED=LED_Data[31:24];endcase end end endmodule `timescale 1ns / 1ps // REG.v module REG(input Clk, input Reset, input [4:0] R_Addr_A, input[4:0] R_Addr_B, input [4:0] W_Addr, input [31:0] W_Data, input Write_Reg, output [31:0] R_Data_A, output [31:0] R_Data_B);reg [31:0] REG_Files[0:31];integer i;assign R_Data_A=REG_Files[R_Addr_A];assign R_Data_B=REG_Files[R_Addr_B];always @(posedge Clk or posedge Reset)beginif(Reset)beginfor(i=0;i<=31;i=i+1)REG_Files[i]<=32'h0000_0000;endelsebeginif(Write_Reg)beginREG_Files[W_Addr]<=W_Data;end end end endmodule管脚配置NET “Clk” LOC=“C9”;NET “Reset” LOC=“D9”;NET “Reg_Addr[4]” LOC=“T5”;NET “Reg_Addr[3]” LOC=“V8”;NET “Reg_Addr[2]” LOC=“U8”;NET “Reg_Addr[1]” LOC=“N8”;NET “Reg_Addr[0]” LOC=“M8”;NET “Write_Reg” LOC=“V9”;NET “Sel[1]” LOC=“T9”;NET “Sel[0]” LOC=“T10”;NET “AB” LOC=“A8”;NET “LED[7]” LOC=“T11”;NET “LED[6]” LOC=“R11”;NET “LED[5]” LOC=“N11”;NET “LED[4]” LOC=“M11”;NET “LED[3]” LOC=“V15”;NET “LED[2]” LOC=“U15”;NET “LED[1]” LOC=“V16”;NET “LED[0]” LOC=“U16”;第三篇:_计算机组成原理实验2计算机组成原理实验日志实验题目:进位、移位控制实验实验目的:(1)了解带进位控制的运算器的组成结构;(2)验证带进位控制的运算器的功能。

大连理工大学《计算机网络实验(一)》实验报告及学习要求

姓名:

报名编号:

学习中间:

层次:(高起专或专升本)

专业:

客观题:谈谈你对本课程学习过程中的心得当会?

试验一:PC的网络衔接及测试

试验意图:

试验疑问评论:

1.T568A 线序和T568B 线序。

2.网线制作过程。

试验二:交流机VLAN的根本装备

试验意图:

试验疑问评论:

1.哪些指令是将Switch B的1-6号端口区分到VLAN2?2. 4台PC机之间可以ping通吗?请写出成果及其缘由。

试验三:路由器静态路由装备

试验意图:

试验疑问评论:

1.路由器静态路由装备试验,为何需求两条装备口电缆,其效果是啥?

2.经过路由器静态路由装备的试验,写出静态路由完成的功用以及静态路由装备的效果。

试验四:生成树协议STP的装备

试验意图:

试验疑问评论:

1.生成树协议界说?

2.写出将4台交流机顺次命名为 SwitchA, SwitchB, SwitchC, 和SwitchD的代码。

试验五:路由器RIP的根本装备

试验意图:

试验疑问评论:

1.怎么发动RIP协议?

2.发动RIP协议之后,路由表详细改变是啥?。

大连理工大学操作系统实验报告(附代码)

//初始化套接字库 //创建 TCP 套接字

//初始化地址结构

while(1){ if(::bind(link, (sockaddr*)&addr1, sizeof(addr1)) == 0){ ::listen(link, 5); cout<<"你已成功启动.\n"; break; }else{ addr1.sin_port = htons(++port); } } HANDLE h1 = ::CreateThread(NULL,0,fx1,NULL,0,NULL);

2.WinSock #include <iostream> #include <stdio.h> #include <windows.h> using namespace std; DWORD WINAPI fx1(LPVOID lp); DWORD WINAPI fx2(LPVOID lp); SOCKET link,sender,s; sockaddr_in addr1,addr2; int port = 75; char* friendIp; bool connected = false; bool connecting = false; bool close = false; int main() { friendIp = new char[20]; WSAData data; WORD wVersion = MAKEWORD(2,0); ::WSAStartup(wVersion, &data); link = ::socket(AF_INET,SOCK_STREAM,0); s = ::socket(AF_INET, SOCK_STREAM, 0); addr1.sin_family = AF_INET; addr1.sin_port = htons(port); addr1.sin_addr.S_un.S_addr = INADDR_ANY;

大连理工大学软件学院计算机组成原理实验报告

大连理工大学本科实验报告课程名称:学院(系):专业:班级:学号:学生姓名:年月日实验项目列表大连理工大学实验预习报告学院(系):专业:班级:姓名:学号:组: ___实验时间:实验室:实验台:指导教师签字:成绩:一、部件实验报告1.实验名称:部件实验——总线数据传输实验2.实验目的:了解总线在计算机中的作用及数据传输原理3.实验要求:把内存作为中间介质,完成寄存器间的数据传输4.实验原理图:(P32)5.实验操作步骤(流程图)开始将开关s0-s7置11110000上拨S13、S11s0-s7置10101010上拨S13、S10,下拨S10将开关全部复位上拨S12、S16、S15S11、S10,下拨S10将开关全部复位实验体会、意见、建议体会:通过这次实验,我对总线的作用和数据的传输原理有了初步的了解。

在实验过程中,开关的上拨顺序(有些开关必须先于某些上拨才能正常进行)和复位顺序很重要,一般遵照先拨后复位的顺序进行。

另外S10比较特殊是下降沿有效,所以需拨两次。

意见及建议:关于部件的实验过于简单和单调,建议增加关于部件的实验内容。

大连理工大学实验预习报告学院(系):专业:班级:姓名:学号:组: ___实验时间:实验室:实验台:指导教师签字:成绩:二、8位微程序控制计算机预习报告1 一位乘法程序的 *. LST 文件(要在重要地方加注释行,尽量使原程序易读)1 0000 ORG 02 0000 STRT:3 0000 3C00 MOV R4,#04 0002 3B00 MOV R3,#05 0004 3D0A MOV R5,#106 0006 600000 JKB STRT7 0009 408001 LDA 8001H8 000C 0F MOV R7,A9 000D L1:10 000D 60000D JKB L111 0010 408001 LDA 8001H12 0013 0E MOV R6,A13 0014 3001 MOV A,#414 0016 488002 STA 8002H15 0019 L2:16 0019 680019 JPB L217 001C 300A MOV A,#0AH18 001E 488002 STA 8002H19 0021 L3:21 0024 3010 MOV A,#10H22 0026 27 ADD A,R723 0027 488002 STA 8002H24 002A L4:25 002A 68002A JPB L426 002D 3009 MOV A,#927 002F 488002 STA 8002H28 0032 L5:29 0032 680032 JPB L530 0035 300A MOV A,#0AH31 0037 488002 STA 8002H32 003A L6:33 003A 68003A JPB L634 003D 3010 MOV A,#10H35 003F 26 ADD A,R636 0040 488002 STA 8002H37 0043 L7:38 0043 680043 JPB L739 0046 300A MOV A,#0AH40 0048 488002 STA 8002H41 004B L8:43 004E 300A MOV A,#0AH44 0050 488002 STA 8002H45 0053 L9:46 0053 680053 JPB L947 0056 06 MOV A,R6 ;把R6当作计数器48 0057 3A01 MOV R2,#149 0059 3B00 MOV R3,#00H50 005B L10: ;循环加被乘数,并把结果存在R3中51 005B 2A SUB A,R252 005C 500067 JC L1153 005F 0E MOV R6,A54 0060 03 MOV A,R355 0061 27 ADD A,R756 0062 0B MOV R3,A57 0063 06 MOV A,R658 0064 58005B JMP L1059 0067 L11:60 0067 03 MOV A,R3 ;分离R361 0068 2D SUB A,R562 0069 500073 JC L1264 006D 04 MOV A,R465 006E 22 ADD A,R2 ;计算十位66 006F 0C MOV R4,A ;把十位存入R4中67 0070 580067 JMP L1168 0073 L12:69 0073 04 MOV A,R470 0074 2A SUB A,R2 ;判断十位R4是否为071 0075 50008B JC L1372 0078 03 MOV A,R373 0079 C1:74 0079 680079 JPB C175 007C 488002 STA 8002H76 007F C2:77 007F 68007F JPB C278 0082 3010 MOV A,#10H79 0084 24 ADD A,R480 0085 488002 STA 8002H81 0088 580094 JMP OVER82 008B L13:83 008B 68008B JPB L1384 008E 3010 MOV A,#10H86 0091 488002 STA 8002H87 0094 OVER:88 0094 580000 JMP STRT 2大连理工大学实验报告学院(系):专业:班级:姓名:学号:组: ___实验时间:实验室:实验台:指导教师签字:成绩:三、8位微程序控制计算机实验报告1.实验名称:8位微程序控制计算机实验2.实验目的:了解微程序控制计算机的工作原理及实现方法、初步学会程序的流程图画法及程序的模块化设计、调试方法。

大连理工大学计算机系统结构实验-实验一

大连理工大学实验报告计算机系统结构实验实验一MIPS指令系统和MIPS体系结构学院(系):电子信息与电气工程学部专业:计算机科学与技术学生姓名:班级:学号:大连理工大学Dalian University of Technology实验一MIPS指令系统和MIPS体系结构一、实验目的和要求1. 了解熟悉MIPSsim模拟器。

2. 熟悉MIPS指令系统及其特点。

3. 熟悉MIPS体系结构。

二、实验步骤1、启动MIPSsim。

2、选择“配置”->“流水方式”选项,使模拟器工作在非流水方式。

3、参照使用说明,熟悉MIPSsim模拟器的操作和使用方法。

4、选择“文件”->“载入程序”选项,加载样例程序alltest.asm,然后查看“代码”窗口,查看程序所在的位置(起始地址为0x00000000)。

5、查看“寄存器”窗口PC寄存器的值:[PC]= 0x00000000 。

6、执行load和store指令,步骤如下:(1)单步执行一条指令(F7)。

(2)下一条指令地址为= 0x00000004 ,是一条有(有,无)符号载入字节(字节,半字,字)指令。

(3)单步执行一条指令(F7)。

(4)查看R1的值,[R1]=0X FFFFFFFFFFFFFF80 。

(5)下一条指令地址为=0X00000008 ,是一条有(有,无)符号载入字(字节,半字,字)指令。

(6)单步执行1条指令。

(7)查看R1的值,[R1]=0X0000000000000080 。

(8)下一条指令地址为=0X0000000C ,是一条无(有,无)符号载入字(字节,半字,字)指令。

(9)单步执行1条指令。

(10)查看R1的值,[R1]= 0X0000000000000080 。

(11)单步执行1条指令。

(12)下一条指令地址为0X00000014 ,是一条保存字(字节,半字,字)指令。

(13)单步执行一条指令。

(14)查看内存BUFFER处字的值,值为0x00000080 。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

地址流文件名:cc1.din

.din

地址流文件名:tex.din

(4)分析Cache块大小对不命中率的影响。

答:对于给定的Cache容量,当块大小开始增加时,不命中率开始下降,但是有些情况到后来反而上升了。说明增加块大小会产生双重作用。

4、替换算法对不命中率的影响

(1)用鼠标单击“复位”按钮,把各参数设置为默认值。

(2)选择地址流文件all. din。

(3)对于不同的替换算法、Cache容量和相联度,分别执行模拟器,然后在下中记录各种情况下的不命中率。

表 LRU和随机替换法的不命中率的比较

(4)分析不同的替换算法对Cache不命中率的影响。

表 不同容量下Cache的不命中率

(5)以容量为横坐标,画出不命中率随Cache容量变化而变化的曲线,并指明地址流文件名。

(6)根据该模拟结果,你能得出什么结论?

答:随着Cache容量的增大,不命中率降低,但是降低的幅度由较大差别,Cache容量足够大以后,不命中率降到一定程度以后,降低效果不再明显。

3、Cache块大小对不命中率的影响

(1)用鼠标单击“复位”按钮,把各参数设置为默认值。

(2)选择一个地址流文件。

(3)选择不同的Cache块大小,包括16B、32B、64B、128B和256B。对于 Cache的各种容量,包括2KB、8KB、32KB、64KB、128KB和512KB。分别执行模拟器,然后在下表中记录各种情况下的不命中率。

(3)选择一个地址流文件。方法:选择“访问地址”—>“地址流文件”选项,然后单击“浏览”按钮,从本模拟器所在文件夹下的“地址流”文件夹中选取。

(4)选择不同的Cache容量,包括2KB、4KB、8KB、16KB、32KB、64KB、128KB和256KB。分别执行模拟器(单击“执行到底”按钮即可执行),然后在下表中记录各种情况下的不命中率。

(2)掌握Cache容量、相联度、块大小对Cache性能的影响。

(3)掌握降低Cache不命中率的各种方法以及这些方法对提高Cache性能的好处。

(4)理解LRU与随机法的基本思想以及它们对Cache性能的影响。

二、实验步骤与操作方法

1、Cache容量对不命中率的影响。

(1)启动MyCache。

(2)用鼠标单击“复位”按钮,把各参数设置为默认值。

2.相联度对不命中率的影响

(1)用鼠标单击“复位”按钮,把各参数设置为默认值。此时的Cache容量为64KB。

(2)选择一个地址流文件。

(3)选择不同的Cache相联度,包括2路、4路、8路、16路和32路。分别执行模拟器,然后在下表中记录各种情况下的不命中率。

表 当容量为64KB时,不同相联度下Cache的不命中率

答:在cache容量较小时用LRU替换算法明显比随机算法的不命中率低,而随着CACHE容量的增大,不同替换算法造成的不命中率差异不明显

三、实验结果与分析

实验结果和分析详见第二部分,实验步骤与操作方法。

四、讨论、建议、质疑

感谢您的支持与配合,我们会努力把内容做得更好!

(4)把Cache的容量设置为256KB,重复(3)的工作,并填写下表。

表 当容量为256KB时,不同相联度下Cache的不命中率

(5)以相联度为横坐标,画出在64KB和256KB的情况下不命中率随Cache相联度变化而变化的曲线,并指明地址流文件名。

(6)根据该模拟结果,你能得出什么结论?

答:增大相联度在一定范围内同样也能降低不命中率,不过对比不同Cache容量的两个图可以发现,当Cache容量足够大时,其改善也变得越发不明显了。

大连理工大学实验报告

计算机系统结构实验

实验四Cache性能分析

学 院(系):电子信息与电气工程学部

专 业:计算机科学与技术

学 生 姓 名:

班 级:

学 号:

大连理工大学

Dalian University of Technology

实验四 Cache性能分析

一、实验目的和要求

(1)加深对Cache的基本概念、基本组织结构以及基本工作原理的理解。