数字钟时钟电路图

1602电子时钟电路_原理图_PCB图

1602电子时钟电路_原理图_PCB图XXXXX学院电子线路课程设计【带LCD显示的电子时钟】班级:XX姓名:XX学号:XX指导老师:XXXX年XX月XX 日摘要在当代繁忙的学习与生活中,数字钟已成为人们日常生活中必不可少的必需品,被广泛用于个人家庭以及办公室等公共场所,给人们的生活、学习、工作、娱乐带来极大的方便。

数字电路采用数字电路,实现对时、分、秒时钟显示的计时装置,具有走时准确、性能稳定、携带方便等优点它还用于计时、自动报时及自动控制等各个领域。

单片机具有体积小、功能强可靠性高、价格低廉等一系列优点基于单片机的定时器功能完成的数字钟电路的设计,结构简单,便于携带。

也利于我们将已学过的比较零散的数字电路的知识有机的、系统的联系起来用于实际,来培养我们的综合分析和设计电路、写程序、调试电路的能力。

研究数字钟以及扩大其应用,具有非常现实的意义。

此设计中的数字钟不仅可以显示普通的年、月、日、时、分、秒外,还可加入蜂鸣器、按键复位等功能。

关键字:LCD1602 单片机电子时钟定时复位一( 任务要求设计一个时钟电路。

以单片机为核心模块,LCD1602为显示模块,通过控制使1602显示时间、字符。

1.1 基本要求1).第一行显示自己的名字2).第二行显示时间1.2 发挥部分1).加入按键,实现调时功能2).加入蜂鸣器,实现闹钟功能二(系统分析2.1 系统总体方框图显示电路复位电路ST89C51外部中断晶振电路2.2 系统总体分析本设计由ST89C51单片机、复位电路、晶振电路、外部中断和显示电路5个模块组成。

其中以单片机模块为核心模块,主导其余四个模块工作,1602显示模块用来显示秒、分、时计数单位中的值。

利用AT89c51单片机内部的定时/计数器进行中断定时,配合软件延时,实现电路的总体功能。

三、硬件设计3.1、晶振电路图3.1 晶振电路一般的晶振振荡电路都是在一个反相放大器的两端接入晶振,再有两个电容分别接到晶振的两端,每个电容的另一端再接到地,这两个电容串联的容量值就应该等于负载电容。

数字电子钟电路图

数字电子钟电路图一、引言数字电子钟是一种广泛应用于现代生活中的电子设备,它能够精确显示时间,并具有一系列实用的功能,如日期显示、闹钟设置等。

数字电子钟的核心部分是电路板,通过电路板上的元件和连接线来实现时间的获取和显示。

本文将详细介绍数字电子钟的电路图设计及其原理。

二、电路图设计数字电子钟的电路图设计通常包括以下几个主要部分:1. 电源电路:数字电子钟需要一个稳定的电源来供电,通常使用直流电源。

在电路图中,电源电路主要由变压器、整流电路、滤波电路和稳压电路组成。

变压器将交流电转换为适当的电压,整流电路将交流电转换为直流电,滤波电路去掉直流电中的杂波,稳压电路稳定电压,以保证电子元件的正常工作。

2. RTC芯片:RTC芯片负责获取并记录时间信息。

它通常包含一个晶振电路、一个时钟计数器、一个时钟芯片以及一些时钟设置和显示控制的接口。

在电路图中,RTC芯片与其他电子元件通过引脚相连接,以实现时间数据的传输和显示。

3. 数码管:数码管是显示时间和日期的主要输出设备。

它具有多个数码管显示单元,每个数码管显示一个数字。

数码管接收来自RTC芯片的时间信息,并将其以数码形式显示出来。

在电路图中,数码管与RTC芯片之间通过引脚相连,以传输和显示时间数据。

4. 控制电路:控制电路负责对数字电子钟的功能进行控制和设置。

它通常包括按键开关、解码电路和逻辑门电路等。

按键开关用于设置闹钟、日期等功能,解码电路将接收到的按键信号转换为相应的控制信号,逻辑门电路用于实现各种功能的逻辑判断。

三、原理解析数字电子钟的原理基于时钟的计算和显示。

具体原理如下:1. 时间计算原理:RTC芯片中的晶振电路产生一个精确的时钟信号,通过时钟计数器进行计数,并根据计数结果得出当前的时间信息。

通过时钟计数器的设置和控制,可以实现时间的增减、精确校准等功能。

2. 时间显示原理:数字电子钟使用数码管将时间信息以数字形式显示出来。

数码管的每个数码显示单元通过不同的电压脉冲控制来显示不同的数字。

纯数字电路数字时钟原理图(免费)

做成时钟,并不难,把十进改成6进就行了如下:1,震荡电路的电容用晶震,记时准确.2, 时:用2块计数器,十位的用1和2(记时脚)两个脚.分:用2块计数器,十位的用1,2,3,4,5,6,(记时脚)6个脚.秒:同分.评论:74系列的集成块不如40系列的,如:用CD4069产生震荡,CD4017记数,译码外加.电压5V.比74LS160 74LS112 74LS00好的.而且CD4069外围元件及少.如有需要我可以做给你.首先需要产生1hz的信号,一般采用CD4060对32768hz进行14分频得到2hz,然后再进行一次分频。

(关于此类内容请参考数字电路书中同步计数器一章)(原文件名:4060.JPG)一种分频电路:(原文件名:秒信号1.JPG)采用cd4518进行第二次分频另一种可以采用cd4040进行第二次分频第三种比较麻烦,是对1mhz进行的分频(原文件名:秒信号2.JPG)介绍一下cd4518:CD4518,该IC是一种同步加计数器,在一个封装中含有两个可互换二/十进制计数器,其功能引脚分别为1~7和9~{15}。

该计数器是单路系列脉冲输入(1脚或2脚;9脚或10脚),4路BCD码信号输出(3脚~6脚;{11}脚~{14}脚)。

此外还必须掌握其控制功能,否则无法工作。

手册中给有控制功能的真值(又称功能表),即集成块的使用条件,如表2所示。

从表2看出,CD4518有两个时钟输入端CP和EN,若用时钟上升沿触发,信号由CP输入,此时EN端应接高电平“1”,若用时钟下降沿触发,信号由EN端输入,此时CP端应接低电平“0”,不仅如此,清零(又称复位)端Cr也应保持低电平“0”,只有满足了这些条件时,电路才会处于计数状态,若不满足则IC不工作。

计数时,其电路的输入输出状态如表3所示。

值得注意,因表3输出是二/十进制的BCD码,所以输入端的记数脉冲到第十个时,电路自动复位0000状态(参看连载五)。

另外,该CD4518无进位功能的引脚,但从表3看出,电路在第十个脉冲作用下,会自动复位,同时,第6脚或第{14}脚将输出下降沿的脉冲,利用该脉冲和EN端功能,就可作为计数的电路进位脉冲和进位功能端供多位数显用。

数字钟时钟电路图设计课设

一、概述现今,酒店已成为生活中不可缺少的一部分,是很多旅行者休息的场所。

该课程设计是关于简易酒店客房控制器的设计,主要包括四个方面,24小时时钟的设计,客房服务控制,客房照明控制以及简易稳压直流电源的设计。

数字钟实际上是两个60,一个24进制的计数电路。

由于计数的起始时间有时不与标准时间(如北京时间)一致,故需要在电路上加一个校时电路。

稳压电源的设计是将220v 的交流电转换5v 的直流电,既可以给多谐振荡器供电,又可以给照明,客房服务进行控制。

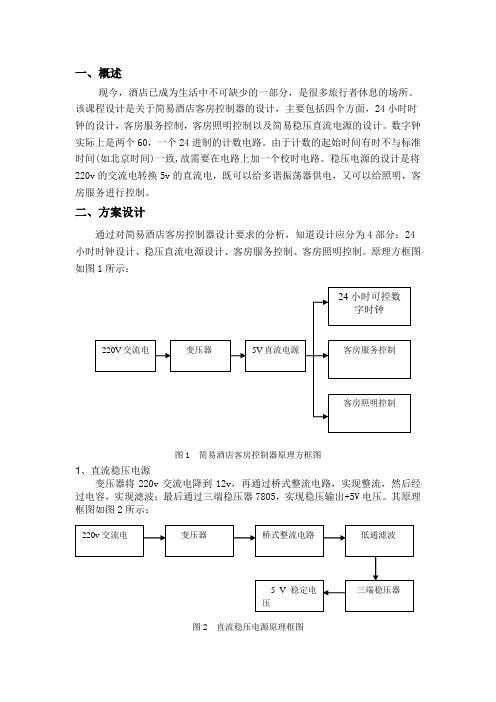

二、方案设计通过对简易酒店客房控制器设计要求的分析,知道设计应分为4部分:24小时时钟设计、稳压直流电源设计、客房服务控制、客房照明控制。

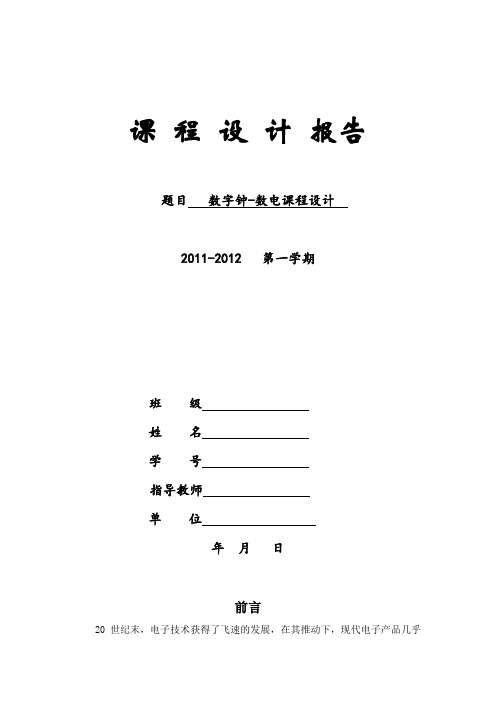

原理方框图如图1所示:图1 简易酒店客房控制器原理方框图1、直流稳压电源变压器将220v 交流电降到12v ,再通过桥式整流电路,实现整流,然后经过电容,实现滤波;最后通过三端稳压器7805,实现稳压输出+5V 电压。

其原理框图如图2所示:图2 直流稳压电源原理框图220v 交流电变压器桥式整流电路低通滤波5 V 稳定电压三端稳压器220V 交流电变压器24小时可控数字时钟客房服务控制客房照明控制5V 直流电源2、24小时可控数字时钟通过分析,可知需要以数字形式显示时、分、秒的时间和校时功能。

要想构成数字钟,首先应选择一个脉冲源——能自动地产生稳定的标准时间脉冲信号。

通过对24小时可控数字时钟仔细分析,可知它由二个60进制计数器,一个24小时计数器,6个显示译码器,6个数码管及3个校正电路组成。

由555多谐振荡器发出1HZ 的秒脉冲信号,传给第一个60进制计数器,然后依次传给第二个60进制计数器,24进制计数器,通过译码显示给数码管,从而读出时间。

值得注意的是:任何计时装置都有误差,因此应考虑校准时间电路。

24小时可控数字时钟原理框图如图3所示:图3 24小时可控数字时钟原理框图3、客房服务控制通过开关输入信号从而控制“请即清理”,“请勿打扰”。

数字钟课程设计(完整原理图)

课程设计报告题目数字钟-数电课程设计2011-2012 第一学期班级姓名学号指导教师单位年月日前言20世纪末,电子技术获得了飞速的发展,在其推动下,现代电子产品几乎渗透了社会的各个领域,有力地推动了社会生产力的发展和社会信息化程度的提高,同时也使现代电子产品性能进一步提高,产品更新换代的节奏也越来越快。

时间对人们来说总是那么宝贵,工作的忙碌性和繁杂性容易使人忘记当前的时间。

忘记了要做的事情,当事情不是很重要的时候,这种遗忘无伤大雅。

但是,一旦重要事情,一时的耽误可能酿成大祸。

例如,许多火灾都是由于人们一时忘记了关闭煤气或是忘记充电时间。

尤其在医院,每次护士都会给病人作皮试,测试病人是否对药物过敏。

注射后,一般等待5分钟,一旦超时,所作的皮试试验就会无效。

手表当然是一个好的选择,但是,随着接受皮试的人数增加,到底是哪个人的皮试到时间却难以判断。

所以,要制作一个定时系统。

随时提醒这些容易忘记时间的人。

钟表的数字化给人们生产生活带来了极大的方便,而且大大地扩展了钟表原先的报时功能。

诸如定时自动报警、按时自动打铃、时间程序自动控制、定时广播、定时启闭电路、定时开关烘箱、通断动力设备,甚至各种定时电气的自动启用等,所有这些,都是以钟表数字化为基础的。

因此,研究数字钟及扩大其应用,有着非常现实的意义。

目录一、设计目的................................................................................................................................... - 2 -二、设计要求 ................................................................................................................................ - 3 -2.1设计指标 (3)2.2设计要求 (3)2.3制作要求 (3)2.4编写设计报告 (3)三、各单元电路设计 .................................................................................................................... - 4 -3.1工作原理 (4)3.2原理框图 (4)3.3振荡器 (5)3.3.1由石英晶体振荡器构成的1HZ秒脉冲信号 .................................................................. - 5 -3.4时间计数器电路 (6)3.4.1秒计数器的设计.............................................................................................................. - 6 -3.4.2分计数器的设计.............................................................................................................. - 7 -3.4.3时计数器电路.................................................................................................................. - 8 -3.5译码驱动及显示单元的设计 (9)3.6校时电路 (9)3.7整点报时电路 (10)3.7.1 论证............................................................................................................................. - 10 -3.7.2 实现............................................................................................................................. - 10 -四、总电路设计 .......................................................................................................................... - 12 -五、元件清单 .............................................................................................................................. - 12 -六、课程设计体会 ...................................................................................................................... - 13 -七、参考文献 .............................................................................................................................. - 14 -一、设计目的1、熟悉集成电路的引脚安排;2、掌握各芯片的逻辑功能及使用方法;3、了解数字钟的组成及工作原理;4、熟悉数字钟的设计与制作;5、熟悉Protel99 SE软件的操作;二、设计要求2.1设计指标时间以24小时为一个周期;能显示时,分,秒;有校时功能,可以分别对时及分进行单独校时,使其校正到标准时间;计时过程具有报时功能,当时间到达整点前10秒进行蜂鸣报时;为了保证计时的稳定及准确须由晶体振荡器提供表针时间基准信号。

数字时钟电路图

多功能数字计时器设计姓名:杨会章学号: 1004220242专业:通信工程学院:电光学院指导教师:2021-9-15目录一、设计内容简介 (3)二、电路功能设计要求 (3)三、电路原理简介 (3)四、各单元电路原理1、脉冲发生电路 (3)2、计时电路 (4)3、译码显示电路 (4)5、校分电路 (5)4、清零电路 (6)6、报时电路 (7)7、基本电路原理图 (8)8、动态显示原理 (9)9、动态显示原理图 (10)10、波形图 (11)五、实验中问题及解决办法 (11)六、附录 (12)1、元件清单 (12)2、芯片引脚图和功能表 (12)3、参考文献 (15)一、设计内容简介实验采用中小规模集成电路设计一个数字计时器。

数字计时器是由脉冲发生电路,计时电路,译码显示电路,和附加电路控制电路几部分组成。

其中控制电路由清零电路,校分电路和报时电路组成。

附加电路采用动态显示。

二、电路功能设计要求1、设计制作一个0分00秒~9分59秒的多功能计时器,设计要求如下:1)设计一个脉冲发生电路,为计时器提供秒脉冲(1HZ),为报时电路提供驱动蜂鸣器的高低脉冲信号(1KHZ、2KHZ);2)设计计时电路:完成0分00秒~9分59秒的计时、译码、显示功能;3)设计清零电路:具有开机自动清零功能,并且在任何时候,按动清零开关,可以对计时器进行手动清零。

4)设计校分电路:在任何时候,拨动校分开关,可进行快速校分。

(校分隔秒)5)设计报时电路:使数字计时器从9分53秒开始报时,每隔一秒发一声,共发三声低音,一声高音;即9分53秒、9分55秒、9分57秒发低音(频率1kHz),9分59秒发高音(频率2kHz);6)系统级联。

将以上电路进行级联完成计时器的所有功能。

7)可以增加数字计时器附加功能:定时、动态显示等。

三、电路原理简介32678Hz石英晶体振荡器产生的稳定的高频脉冲信号,作为数字钟的时间基准,再经分频器、D触发器输出标准秒脉冲。

数字时钟兼钟控电路

1 引言现代科技的不断发展,电子产品越来越向集成化和多功能方面发展。

人们对电子产品的要求也越来越高。

不论是学生还是工作者都离不开电子产品。

电子时钟在人们的生活中应用很广泛,由于其使用方便、价格低廉、性能稳定,非常受人们的欢迎.2 原理框图图2.1原理框图数字钟电路系统由主电路和扩展电路两大部分组成,其中主体电路完成数字钟的基本功能,扩展电路完成控制电路。

系统工作原理:由振荡器输出稳定的高频脉冲信号作为时间基准,经分频振荡器输出标准的秒脉冲,秒计数器满60向分计数器进位,分计数器满60向小时进位,小时计数器按“12翻1”规律计数,计数器经译码器送到显示器;计数出现误差可用校时电路进行校时、校分、校秒。

并具有可整点报时与定时闹钟的功能。

3 主体电路的设计3.1 振荡器晶体振荡器电路给数字钟提供一个频率稳定准确的32768Hz的方波信号,可保证数字钟的走时准确及稳定。

数字显示的电子钟常使用晶体振荡器电路。

如图3.1所示为电子手表集成电路中的晶体振荡器,其内部有15级2分频集成电路所以输出端正好可得到1HZ的标准脉冲。

晶体具有较高的频率稳定性及准确性,从而保证了输出频率的稳定和准确。

图3.1晶体振荡器电路3.2 分频器图3.2分频器电路分频器的功能主要有两个:一是产生标准脉冲信号,二是提供功能扩展电路所需要的信号。

选用中规模集成电路计数器74LS90可以完成上述功能。

如图3.2将三片74LS90进行级联因每片为1/15分频器,三片级联正好获得1HZ的标准脉冲。

有表1得,当74LS90接成BCD十进制计数器时,Q1的输出是输入脉冲CP的2分频,所以第一片74LS90的Q1输出脉冲频率为500HZ3.3 时分秒计数器分和秒计数器都是M=60的计数器,采用中规模集成电路十进制计数器至少需要两片,因为10〈M〈100。

他们的个位都是十进制器,而十位则是六进制计数器,其计数规律为00—01—02—…..—58—59—00。

数字钟时钟电路图

目录前言: (4)1.设计目的 (6)2.设计功能要求 (6)3.电路设计1111111111 (6)3.1设计方案 (6)3.2单元电路的设计 (7)3.2.1 主体电路部分 (7)3.2.1.1 振荡电路 (8)3.2.1.2 计数电路 (12)3.2.1.3 校时电路 (17)3.2.1.4 译码与显示电路 (19)3.2.2扩展功功能电路的设计 (21)3.2.2.1定时控制电路 (21)3.2.2.2 仿广播电台正点报时电路 (23)3.2.2.3 自动报整点时数电路 (24)3.2.2.4 触摸报整点时数电路 (26)4.调试 (27)4.1主体电路部分 (27)4.2 扩展电路部分 (29)5.总结 (31)致 (32)参考文献 (33)附录 (34)1.设计目的设计一种多功能数字钟,该数字钟具有基本功能和扩展功能两部分。

其中,基本功能部分的有准确计时,以数字形式显示时、分、秒的时间和校时功能。

扩展功能部分则具有:定时控制、仿广播电台正点报时、自动报整点时数和触摸报正点的功能。

数字钟的电路也是由主体电路和扩展电路两部分构成,在电路中,基本功能部分由主体电路实现,而扩展功能部电路实现。

这两部分都有一个共同特点就是它们都要用到振荡电路提供的1Hz脉冲信号。

在计时出现误差时电路还可以进行校时和校分,为了使电路简单所设计的电路不具备校秒的功能。

并且要用数码管显示时、分、秒,各位均为两位显示,扩展部分要有相应的响应电路。

分则由扩展2.设计功能要求基本功能:(1)时的计时要求为“12翻1”,分和秒的计时要求为60进制(2)准确计时,以数字形式显示时,分,秒的时间(3)校正时间扩展功能:(1)定时控制;(2)仿广播电台报时功能;(3)自动报整点时数;(4)触摸报整点时数;3.电路设计3.1设计方案根据设计要求首先建立了一个多功能数字钟电路系统的组成框图,框图如图1所示。

主体电路扩展电路图1由图1可知,电路的工作原理是:多功能数字钟电路由主体电路和扩展电路两大部分组成。

数字电子钟的设计电路图pcb图

数字电子钟的设计与制作一、设计概述1.设计任务➢时钟脉冲电路设计➢60进制计数器设计➢24进制计数器设计➢“秒”,“分”,“小时”脉冲逻辑电路设计➢“秒”,“分”,“小时”显示电路设计➢“分”,“小时”校时电路➢整点报时电路2.功能特性➢设计的数字钟能直接显示“时”,“分”,“秒”,并以24小时为一计时周期。

➢当电路发生走时误差时,要求电路具有校时功能。

➢要求电路具有整点报时功能,报时声响为四低一高,最后一响正好为整点。

3.原理框图图 1 原理框图二、设计原理数字钟是一个将“时”,“分”,“秒”显示于人的视觉器官的计时装置。

它的计时周期为24小时,显示满刻度为23时59分59秒,另外应有校时功能和报时功能。

因此,一个基本的数字钟电路主要由译码显示器、“时”,“分”,“秒”计数器、校时电路、报时电路和振荡器组成。

干电路系统由秒信号发生器、“时、分、秒”计数器、译码器及显示器、校时电路、整点报时电路组成。

秒信号产生器是整个系统的时基信号,它直接决定计时系统的精度,一般用石英晶体振荡器加分频器来实现。

将标准秒信号送入“秒计数器”,“秒计数器”采用60进制计数器,每累计60秒发现胡一个“分脉冲”信号,该信号将作为“分计数器”的时钟脉冲。

“分计数器”也采用60进制计数器,每累计60分钟,发出一个“时脉冲”信号,该信号将被送到“时计数器”。

“时计数器”采用24进制计时器,可实现对一天24小时的累计。

译码显示电路将“时”、“分”、“秒”计数器的输出状态菁七段显示译码器译码,通过六位LED七段显示器显示出来。

整点报时电路时根据计时系统的输出状态产生一脉冲信号,然后去触发一音频发生器实现报时。

校时电路时用来对“时”、“分”、“秒”显示数字进行校对调整的。

三、设计步骤1.计数器电路根据计数周期分别组成两个60进制(秒、分)和一个24进制(时)的计数器。

把它们适当连接就可以构成秒、分、时的计数,实现计时功能。

CC4518的符号如图,一个芯片集成了两个完全相同的十进制计数器,其异步清零信号CR是高电平有效。

多功能数字钟电路设计指导书及仿真图

课题一数字电子钟逻辑电路设计一、简述数字电子钟就是一种用数字显示秒、分、时、日得计时装置,与传统得机械钟相比,它具有走时准确,显示直观、无机械传动装置等优点,因而得到了广泛得应用。

小到人们日常生活中得电子手表,大到车站、码头、机场等公共场所得大型数显电子钟。

数字电子钟得电路组成方框图如图1、1所示.图1、1数字电子钟框图由图1、1可见,数字电子钟由以下几部分组成:石英晶体振荡器与分频器组成得秒脉冲发生器;校时电路;六十进制秒、分计数器,二十四进制(或十二进制)计时计数器;秒、分、时得译码显示部分等。

二、设计任务与要求用中、小规模集成电路设计一台能显示日、时、分、秒得数字电子钟,要求如下:1.由晶振电路产生1Hz标准秒信号。

2.秒、分为00~59六十进制计数器。

3、时为00~23二十四进制计数器。

4、周显示从1~日为七进制计数器。

5、可手动校时:能分别进行秒、分、时、日得校时。

只要将开关置于手动位置,可分别对秒、分、时、日进行手动脉冲输入调整或连续脉冲输入得校正.6、 整点报时。

整点报时电路要求在每个整点前呜叫五次低音(500Hz ),整点时再呜叫一次高音(1000Hz)。

三、可选用器材1、 通用实验底板2、 直流稳压电源3、 集成电路:C D4060、74LS74、74LS 161、74L S248及门电路4、 晶振:32768 Hz5、 电容:100μF/16V 、22pF 、3~22pF 之间6、 电阻:200Ω、10K Ω、22MΩ7、 电位器:2、2K Ω或4、7K Ω8、 数显:共阴显示器L C5011—119、 开关:单次按键 10、 三极管:8050 11、 喇叭:1 W /4,8Ω四、设计方案提示根据设计任务与要求,对照数字电子钟得框图,可以分以下几部分进行模块化设计。

1. 秒脉冲发生器脉冲发生器就是数字钟得核心部分,它得精度与稳定度决定了数字钟得质量,通常用晶体振荡器发出得脉冲经过整形、分频获得1Hz 得秒脉冲.如晶振为32768 Hz ,通过15次二分频后可获得1H z得脉冲输出,电路图如图1、2所示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

图9

表1 BCD码十进制计数时序表2二—五混合进制计数时序

CK

0

0

0

0

0

1

0

0

0

1

2

0

0

1

0

3

0

0

1

1

4

0

1

0

0

5

0

1

0

1

6

0

1

1

0

7

0

1

1

1

8

1

0

0

0

9

1

0

0

1

CK

0

0

0

0

0

1

0

0

0

1

2

0

0

1

0

3

0

0

1

1

4

0

1

0

0

5

1

0

0

0

6

1

0

0

1

7

1

0

1

0

8

1

0

1

1

9

1

1

0

0

②异步计数器74LS92

所谓异步计数器是指计数器内各触发器的时钟信号不是来自于同一外接输入时钟信号,因而触发器不是同时翻转。这种计数器的计数速度慢。一异步计数器74LS92是二—六—十二进制计数器,即CKA和 组成二进制计数器,CKB和 在74LS92中为六进制计数器。当CKB和 相连,时钟脉冲从CKA输入,74LS92构成十六进制计数器。74LS92的管脚图如图10。

CK

Q10

Q03 Q02 Q01 Q00

0

1

2

3

4

5

6

7

0

0

0

0

0

0

0

0

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

8

9

10

11

12

13

0

0

0

1

1

1

0

1 0 0 0

1 0 0 1

1 0 1 0

0 0 0 0

0 0 0 1

0 0 1 0

3.2单元电路的设计

数字电子钟的设计方法很多种,例如,可用中小规模集成电路组成电子钟;也可以利用专用的电子钟芯片配以显示电路及其所需要的外围电路组成电子钟;还可以利用单片机来实现电子钟等。

在本次设计,电路是由许多单元电路组成的,因此首先必须对各个单元电路进行设计。

3.2.1主体电路部分

主体电路部分的电路主要由振荡电路、计数电路、显示电路以及校时电路四大部分组成。下面将对各部分电路进行设计。

1.设计目的

设计一种多功能数字钟,该数字钟具有基本功能和扩展功能两部分。其中,基本功能部分的有准确计时,以数字形式显示时、分、秒的时间和校时功能。扩展功能部分则具有:定时控制、仿广播电台正点报时、自动报整点时数和触摸报正点的功能。数字钟的电路也是由主体电路和扩展电路两部分构成,在电路中,基本功能部分由主体电路实现,而扩展功能部电路实现。这两部分都有一个共同特点就是它们都要用到振荡电路提供的1Hz脉冲信号。在计时出现误差时电路还可以进行校时和校分,为了使电路简单所设计的电路不具备校秒的功能。并且要用数码管显示时、分、秒,各位均为两位显示,扩展部分要有相应的响应电路。分则由扩展

下面将分别介绍60进制计数器和“12翻1”小时计数器。

(一)60进制计数器

电路如图8所示

图8

电路中,74LS92作为十位计数器,在电路中采用六进制计数;74LS90作为个位计数器在电路中采用十进制计数。当74LS90的14脚接振荡电路的输出脉冲1Hz时74LS90开始工作,它计时到10时向十位计数器74LS92进位。下面对电路中所用的主要元件及功能介绍。

②计数器74LS191

74LS191的管脚图如图13

图13

3.2.1.3校时电路

(一)电路如图14所示

图14

(二)电路的工作原理

校时电路的作用是:当数字钟接通电源或者出现误差时,校正时间。校时是数字钟应具有的基本功能。一般电子表都具有时、分、秒等校时功能。为了使电路简单,在此设计中只进行分和小时的校时。校时有“快校时”和“慢校时”两种,“快校时”是通过开关控制,使计数器对1Hz校时脉冲计数。“慢校时”是用手动产生单脉冲作校时脉冲。图中S1校分用的控制开关,S2(总图)为校时用的控制开关,它们的控制功能如表4所示,校时脉冲采用分频器输出的1Hz脉冲,当S1或S2分别为“0”时可以进行“快校时”。如果校时脉冲由单次脉冲产生器提供,则可以进行“慢校时”。表4校时开关的功能

输入输出

输入输入输出

清零

图4图5

图6

输入

输出

CK

CR

EN

上升沿

L

H

加计数

L

L

上升沿

加计数

下降沿

L

X

保持

X

L

上升沿

上升沿

L

L

H

L

下降沿

X

L

X

全为L

上表:CD4518的功能表

振荡器和分频器两部分构成振荡电路,它的电路图如图7所示。

根据图7可知电路的工作原理是:石英晶体振荡器提供的频率为1MHz,CD4518组成十分频电路。并且一个CD4518可以组成两个十分频电路即:CD4518的引脚2与引脚6组成一个十分频电路而引脚10与引脚14组成另一个十分频电路。晶振的输出接入第一块CD4518的输入引脚2,经过一次十分频,频率变为100KHz。输出引脚6接入同一块CD4518的引脚10经第二次分频,频率变为10KHz。输出引脚接人第二块CD4518的输入引脚2再经一次分频,频率变为1KHz。这样经过六次分频最后可以得到1Hz的频率。

0 0 0 1

(二)电路的工作原理

由表可知:个位计数器由4位二进制同步可逆计数器74LS191构成,十位计数器由双D触发器74LS74构成,将它们组成“12翻1”小时计数器。

由表可知:计数器的状态要发生两次跳跃:一是:计数器计到9,即个位计数器的状态为 =1001后,在下一计数脉冲的作用下计数器进入暂态1010,利用暂态的两个1即 使个位异步置0,同时向十位计数器进位使 =1;二是计数到12后,在第13个计数脉冲作用下个位计数器的状态应为 =0001,十位计数器的 =0。第二次跳跃的十位清“0”和个位置“1”的输出端 、 、 来产生。对电路中所用的主要元件及功能介绍。

S1

S2

功能

1

1

ห้องสมุดไป่ตู้计数

1

0

校分

0

0

校时

表4

(三)对电路中所用的主要元件及功能介绍

在此电路中,用到的元器件有两块四2输入与非门74LS00、一块六反相器74 LS04、两个电容、两个电阻以及两个开关。

(1)四-2输入与非门74LS00

集成逻辑门是数字电路中应用十分广泛最基本的一种器件,为了合理的使用和充分利用其性能,必须对它的主要参数和逻辑功能进行测试。74LS00与非门的主要参数为:

主体电路扩展电路

图1

由图1可知,电路的工作原理是:多功能数字钟电路由主体电路和扩展电路两大部分组成。其中主体电路完成数字钟的基本功能,扩展电路完成数字钟的扩展功能。

振荡器产生的高脉冲信号作为数字钟的振源,再经分频器输出标准秒脉冲。秒计数器计满60后向分计数器个位进位,分计数器计满60后向小时计数器个位进位并且小时计数器按照“12翻1”的规律计数。计数器的输出经译码器送显示器。计时出现误差时电路进行校时、校分、校秒。扩展电路必须在主体电路正常运行的情况下才能进行扩展功能。

弛豫振荡器对许多低成本而精度要求又不高的场所非常适合,但是并不推荐在任何有精度要求的实际应用电路采用它。

如果想要获得高的精度,就应该在振荡电路中使用石英晶体作振源。在数字钟的设计与制作中应采用石英晶体振荡器,因为石英晶体具有压电效应,是一个压电器件。当交流电压加在晶体两端,晶体先随电压变化产生对应的变化,然后机械振动又使晶体表面产生交变电荷。当晶体几何尺寸和结构一定时,它本生有一个固定的机械频率。当外加交流电压的频率等于晶体的固有频率时,晶体片的机械振动最大,晶体表面电荷量最多,外电路的交流电流最强,于是产生振荡,因此将石英晶体按一定方位切割成片,两边傅以电极,焊上引线,再用金属或玻璃外壳封装即构成石英晶体。石英晶体的固有频率十分稳定。另外石英晶体的振动具有多谐性,除了基频振动外,还有奇次谐次泛音振动,对于石英晶体,既可利用基频振动,也可利用泛音振动。前者称为基频晶体,后者称为泛音晶体,晶片厚度与振动频率成反比,工作频率越高,要求晶片厚度越薄。将石英晶体作为高Q值谐振回路元件接入反馈电路中,就组成了晶体振荡器。在设计中所用的振荡器的电路图如图3所示。该电路能产生1MHz的方波脉冲振荡信号。

图3

(2)分频器

分频器的作用是将由石英晶体产生的高频信号分频成基时钟脉冲信号和扩展部分所需的频率。在此电路中,分频器的功能主要有两个:一是产生标准脉冲信号;二是功能扩展电路所需的信号,如仿电台用的1KHz的高频信号和500Hz的低频信号等.在此电路中作为分频器的元件是:CD4518。

CD4518可以组成二分频电路和十分频电路。用CD4518组成二分频的电路如图4;用CD4518组成十分频的电路如图5;在本次设计中所用的分频器的电路图如图6。电路经过十分频后将晶振来的1MHz的振荡脉冲变为1Hz的脉冲信号,该信号作为计数器的计数脉冲使用。