【CN110061738A】一种全数字锁相环电路【专利】

一种锁相环电路及其工作方法[发明专利]

![一种锁相环电路及其工作方法[发明专利]](https://img.taocdn.com/s3/m/13fa0a85caaedd3382c4d361.png)

专利名称:一种锁相环电路及其工作方法专利类型:发明专利

发明人:唐佳捷,史爱焕

申请号:CN201110441754.7

申请日:20111226

公开号:CN103178840A

公开日:

20130626

专利内容由知识产权出版社提供

摘要:本发明公开一种锁相环电路,其包括锁相环核心单元和锁相环控制单元,当所述锁相环电路处于发射状态时,所述锁相环核心单元在所述锁相环控制单元的控制下通过整数分频开环模式输出信号;当所述锁相环电路处于接收状态时,所述锁相环核心单元在所述锁相环控制单元的控制下通过小数分频闭环模式输出信号。

本发明通过以上技术方案,提供一种更加完善的锁相环电路。

申请人:国民技术股份有限公司

地址:518057 广东省深圳市南山区高新技术产业园区深圳软件园3栋301、302

国籍:CN

代理机构:深圳鼎合诚知识产权代理有限公司

代理人:薛祥辉

更多信息请下载全文后查看。

一种新型PID控制的全数字锁相环的设计与实现.

一种新型PID控制的全数字锁相环的设计与实现锁相环是一种能够跟踪输入信号相位的闭环自动控制系统,广泛应用于信号处理、时钟同步、倍频、频率综合等领域。

它根据输入信号和反馈信号的相位差来调整压控振荡器的输出频率,最终达到输入信号频率和输出信号频率相等,输入信号和输出信号保持恒定的相位差。

传统的PI控制器可以消除稳态误差,保证锁定精度,但是对阻尼有不利影响。

在PI控制器中引入微分项可以改善响应速度和阻尼,保证了锁定时间,但不能减少稳态误差,因此本文提出积分分离PID控制,能够大大改善响应时间和阻尼并减少稳态误差,从而保证了锁相精度和锁相时间。

1 电路结构与工作原理1.1 全数字锁相环电路结构快速全数字锁相环的系统框图如图1所示。

鉴相器采用JK触发器,该鉴相器结构简单,鉴相范围为±π,能够满足一般工程的需要。

由于鉴相器输出的是二值高低脉冲,后需接数字滤波器来平滑其中的起伏,消除噪声和干扰脉冲的影响。

一般数字序列滤波器有两种:N 先于M序列滤波器和随机徘徊滤波器,数字滤波器不是环路滤波器,它是无惰性的,加在环路中不影响环路的阶数,仅起到滤噪抗干扰的作用。

本文采用随机徘徊滤波器。

环路滤波器采用PID控制器,能够很好地控制环路相位校正的速度和精度,相对于文献[1]的PI控制器具有更好的特性。

数字压控振荡器采用可变模的分频器。

M分频器对输出信号进行分频,以使环路得到相应的倍频信号。

1.2 电路工作原理鉴相器比较输入信号和输出信号的相位差,产生一误差高低电平脉冲序列pha。

该脉冲的宽度和输入、输出信号的相位误差是成比例的。

K序列滤波器对相位误差信号进行量化,又可以消除输入信号噪声和干扰脉冲的影响。

当pha为高电平时,K序列滤波器对fO进行加计数,当计数器溢出时,一方面向环路滤波器产生一加脉冲i,同时对计数器进行复位,重新计数。

相反,当pha 为低电平时,K序列滤波器对fO进行减计数,当计数器减为零时,一方面向环路滤波器产生一减脉冲d,同时对计数器进行复位,重新计数。

一种新型的全数字锁相环

一种新型的全数字锁相环[ 来源:机电论文 | 类别:技术 | 时间:2006-3-11 16:33:27 ][字体:大 中 小]原作者:庞 浩,俎云霄,王赞基 原作者出处:(清华大学电机工程与应用电子技术系,北京,100084) 出处【论文摘要】该文提出了一种实现全数字锁相环的新方法。

在基于该方法实现的全数字锁相环中,一种 论文摘要 论文摘 数字比例积分控制的设计结构取代了传统的一些数字环路滤波控制方法。

通过线性近似,该文推导出该 锁相环系统的数学模型,并进一步对该系统的局部动态特性进行了讨论。

理论分析表明这种新型的全数 字锁相环具有很宽的锁相范围,并且在不同被锁频点的局部范围内都具有相同的稳定形式,锁相跟踪达 到稳定的时间与被锁信号的周期成正比。

由于充分利用了鉴相脉冲宽度所包含的相位误差信息,同时又 引入了积分控制,使锁相环的跟踪响应速度得到提高。

仿真实验进一步验证了理论分析的结论。

该文锁 相环采用数字电路方式实现,其性能可以通过比例和积分控制参数进行调节,因而简化了设计过程,便 于应用在电机调速系统、有源滤波器和静止无功补偿器等领域。

1 引言 信号锁相技术广泛应用于自动化控制等领域。

利用该技术可以产生同步于被锁输入信号的整数倍频或 者分数倍频的输出控制信号。

锁相环的基本结构是由鉴相、环路滤波、可控振荡器和 M 倍分频等模块组 成的一个反馈环路,如图 1 所示。

输入的被锁信号首先与同步倍频信号经过 M 倍分频后产生的锁相信号 进行鉴相处理,输出相位误差信号。

环路滤波模块通常具有低通特性,它将相位误差信号转化为稳定的 控制信号,从而控制可控振荡器模块,产生稳定的频率信号输出。

这个频率信号就是所需的同步倍频信 号。

如果整个反馈环路锁相稳定, 锁相环输出的同步倍频信号的频率就是其输入的被锁信号频率的 M 倍。

假如被锁信号在输入鉴相模块之前又先被分频了 L 倍,则锁相获得的同步倍频信号的频率就是被锁信号频率的 M/L 倍。

一种高性能的全数字锁相环设计方案

一种高性能的全数字锁相环设计方案屈八一;程腾;俞东松;李智奇;周渭;李珊珊;刘立东【摘要】针对实现参考频率和输出的频率近似相等或者近似成整数倍关系时遇到的锁相环设计方案复杂以及高性能的模拟锁相环不适宜于集成化问题,设计了主要由模数转换器、全数字式鉴相器、数字式低通滤波器和数控振荡器等构成的全数字式锁相环.主要利用模数转换器在动态量采集时具有的边沿效应从其采集的大量数据中选择出精度更高的数据用于后级的全数字式鉴相,实现了一种全数字式锁相环.实验结果表明了该方案的正确性及其具有锁定精度高和环路的本底噪声低等特性.%Aiming at the fact that a complex scheme is needed when the two frequencies in the phase locked loop are close to each other or have an approximate integer multiple relationship and the traditional analog phase locked loop is unsuitable for integration and on chip implementation,an all-digital phase locked loop is proposed,which is mainly composed of analog to digital converters,an all-digital phase detector,a digital low pass filter and a digitally controlled oscillator.The analog to digital converters'quantization errors have been greatly suppressed by using the clock cursor effect and digital edge effect and an all-digital phase locked loop with a high performance is achieved.Experiment indicates the correctness of the design scheme and shows that the proposed loop has characteristics of high precision and low noise.【期刊名称】《西安电子科技大学学报(自然科学版)》【年(卷),期】2019(046)001【总页数】5页(P112-116)【关键词】数字锁相环;边沿效应;全数字式鉴相器;数控振荡器【作者】屈八一;程腾;俞东松;李智奇;周渭;李珊珊;刘立东【作者单位】长安大学信息工程学院,陕西西安 710064;长安大学信息工程学院,陕西西安 710064;长安大学信息工程学院,陕西西安 710064;西安电子科技大学机电工程学院,陕西西安 710071;西安电子科技大学机电工程学院,陕西西安 710071;长安大学信息工程学院,陕西西安 710064;长安大学信息工程学院,陕西西安710064【正文语种】中文【中图分类】TN911.8锁相技术在频率合成、信号的调制和解调、载波同步、位同步、微弱信号检测以及对宇宙飞行目标的跟踪、遥测和遥控等方面都有重要的应用[1-4]。

一种可编程的全数字锁相环路的实现

一种可编程的全数字锁相环路的实现[日期:2005-3-29] 来源:电子技术应用作者:南京邮电学院信息工程系徐跃王奇何秋阳[字体:大中小]摘要:介绍了一种基于FPGA可编程技术实现的用于无线通信实验系统的全数字锁相环路。

详细叙述了其工作原理、工作性能、电路实现和仿真结果。

关键词:FPGA 全数字锁相环路 VHDL语言锁相环路已在模拟和数字通信及无线电电子学等各个领域中得到了极为广泛的应用,特别是在数字通信的调制解调和位同步中常常要用到各种各样的锁相环。

锁相就是利用输入信号与输出信号之间的相位误差自动调节输出相位使之与输入相位一致,或保持一个很小的相位差。

最初的锁相环全部由模拟电路组成,随着大规模、超高速数字集成电路的发展及计算机的普遍应用,出现了全数字锁相环路。

所谓全数字锁相环路,就是环路部件全部数字化,采用数字鉴相器(DPD)、数字环路滤波器(DLF)、数控振荡器(DCO)构成锁相环路。

在用Altera公司的EPFl0K10TCl44-3芯片设计一种无线通信实验系统的FSK、DPSK、QAM调制解调器时,利用剩余的10%FPGA资源设计出了一种可编程全数字锁相环路,它成功地为该通信实验系统的调制解调器提供了64kHz、56kHz和16kHz三种精确、稳定的时钟信号。

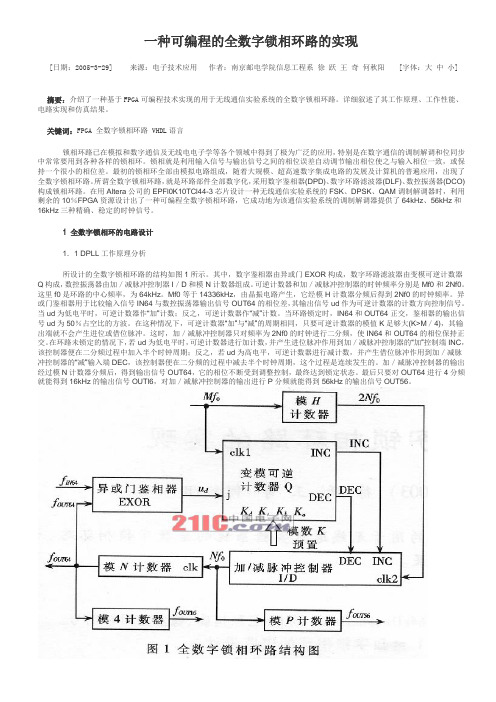

1 全数字锁相环的电路设计1.1 DPLL工作原理分析所设计的全数字锁相环路的结构如图1所示。

其中,数字鉴相器由异或门EXOR构成,数字环路滤波器由变模可逆计数器Q构成,数控振荡器由加/减脉冲控制器I/D和模N计数器组成。

可逆计数器和加/减脉冲控制器的时钟频率分别是Mf0和2Nf0。

这里f0是环路的中心频率,为64kHz。

Mf0等于14336kHz,由晶振电路产生,它经模H计数器分频后得到2Nf0的时钟频率。

异或门鉴相器用于比较输入信号IN64与数控振荡器输出信号OUT64的相位差,其输出信号ud作为可逆计数器的计数方向控制信号。

当ud为低电平时,可逆计数器作“加”计数;反之,可逆计数器作“减”计数。

一种锁相环电路[发明专利]

![一种锁相环电路[发明专利]](https://img.taocdn.com/s3/m/19ca7bc52af90242a995e5a8.png)

专利名称:一种锁相环电路

专利类型:发明专利

发明人:张占锋,刘辉,傅璟军,胡文阁申请号:CN201110143471.4

申请日:20110531

公开号:CN102811052A

公开日:

20121205

专利内容由知识产权出版社提供

摘要:一种锁相环电路,包括:鉴频鉴相器;电荷泵;低通滤波器,连接所述电荷泵,将电荷泵输出的电流脉冲转化为电压信号,并滤除高频信号;压控振荡器,连接所述低通滤波器,根据低通滤波器输出的电压信号产生不同的频率信号;第一二分频器,连接所述压控振荡器,并对压控振荡器输出的频率信号进行二分频;N分频器,连接所述第一二分频器,并对第一二分频器输出的二分频信号进行N分频,N分频后的频率信号作为内部反馈频率信号输出至鉴频鉴相器,其中N≥1;第二二分频器,连接所述压控振荡器,对压控振荡器输出的稳定环路频率进行二分频。

通过第二二分频器对压控振荡器输出的稳定环路频率进行二分频,从而得到既是高频又是占空比50%频率。

申请人:比亚迪股份有限公司

地址:518118 广东省深圳市坪山新区比亚迪路3009号

国籍:CN

更多信息请下载全文后查看。

全数字锁相环[发明专利]

![全数字锁相环[发明专利]](https://img.taocdn.com/s3/m/b63657d9b90d6c85ed3ac60a.png)

专利名称:全数字锁相环

专利类型:发明专利

发明人:张湘辉

申请号:CN200810169985.5申请日:20081016

公开号:CN101414824A

公开日:

20090422

专利内容由知识产权出版社提供

摘要:本发明提供一种全数字锁相环,包含数字环路滤波器及跨越数字环路滤波器的调制器。

调制器包含第一累加器、累加器放大器及调制放大器。

第一累加器包含输入端,第一累加器的输入端接收调制信号。

累加器放大器包含输入端与输出端,累加器放大器的输入端耦接于第一累加器的输出端,且累加器放大器的输出端耦接于数字环路滤波器的输入端。

调制放大器包含输入端与输出端,调制放大器的输入端接收调制信号,且调制放大器的输出端耦接于数字环路滤波器的输出端。

全数字锁相环用于直接频率调制。

上述全数字锁相环能够大幅减少切换噪声,并且有助于芯片面积降低与进程迁移。

申请人:联发科技股份有限公司

地址:台湾省新竹科学工业园区

国籍:CN

代理机构:北京三友知识产权代理有限公司

代理人:任默闻

更多信息请下载全文后查看。

数字时间转换器(DTC)辅助的全数字锁相环(ADPLL)电路[发明专利]

![数字时间转换器(DTC)辅助的全数字锁相环(ADPLL)电路[发明专利]](https://img.taocdn.com/s3/m/13e2bb2ea9114431b90d6c85ec3a87c241288a73.png)

(19)中华人民共和国国家知识产权局(12)发明专利申请(10)申请公布号 (43)申请公布日 (21)申请号 201780096907.4(22)申请日 2017.12.19(85)PCT国际申请进入国家阶段日2020.05.19(86)PCT国际申请的申请数据PCT/SG2017/050627 2017.12.19(87)PCT国际申请的公布数据WO2019/125300 EN 2019.06.27(71)申请人 华为国际有限公司地址 新加坡新加坡市签名大厦樟宜商务园中央2#07-08 51号(72)发明人 杨腾智 陈雪松 于锐 刘苏鹏 袁超 (74)专利代理机构 北京龙双利达知识产权代理有限公司 11329代理人 周乔 王君(51)Int.Cl.H03L 7/085(2006.01)H03L 7/093(2006.01)H03L 7/08(2006.01)(54)发明名称数字时间转换器(DTC)辅助的全数字锁相环(ADPLL)电路(57)摘要本发明公开了一种数字时间转换器(digital -to -time converter,DTC)辅助的全数字锁相环(all digital phase locked loop,ADPLL)电路(200),包括:DTC误差补偿器(202),用于接收相位偏移信号,所述相位偏移信号是对时间数字转换器(time -to -digital converter,TDC)电路(204)的输出进行处理之后得到的,所述相位偏移信号包括DTC误差,所述DTC误差对应于经过DTC电路(206)处理的参考时钟信号与取自所述ADPLL电路的输出信号的反馈时钟信号之间的相位差。

所述补偿器用于处理所述相位偏移信号,以生成表示所述DTC误差的数字信号,所述数字信号作为输出信号。

另外,将所述输出信号从所述相位偏移信号中减去,得到所述相位偏移信号的相位纠正信号。

权利要求书2页 说明书6页 附图3页CN 111386657 A 2020.07.07C N 111386657A1.一种数字时间转换器(digital-to-time converter,DTC)辅助的全数字锁相环(all digital phase locked loop,ADPLL)电路,其特征在于,包括:DTC误差补偿器,用于接收相位偏移信号,所述相位偏移信号是对时间数字转换器(time-to-digital Converter,TDC)电路的输出进行处理之后得到的,所述相位偏移信号包括DTC误差,所述DTC误差对应于经过DTC电路处理的参考时钟信号与取自所述ADPLL电路的输出信号的反馈时钟信号之间的相位差,所述补偿器包括:第一电路,设置有用于接收所述相位偏移信号的解复用器,复用器和电耦合到所述解复用器和所述复用器的多个低通滤波电路,所述低通滤波电路分别用于根据所述参考时钟信号进行操作,所述解复用器用于根据输出到所述DTC电路的DTC输入控制字将所述相位偏移信号输出到选定的低通滤波电路,所述选定的低通滤波电路用于对所述相位偏移信号进行滤波以生成表示所述DTC误差的数字信号,所述复用器用于根据所述DTC输入控制字输出所述数字信号,作为所述补偿器的输出信号,其中,将所述补偿器的输出信号从所述相位偏移信号中减去,得到所述相位偏移信号的相位纠正信号。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

(19)中华人民共和国国家知识产权局

(12)发明专利申请

(10)申请公布号 (43)申请公布日 (21)申请号 201910345593.8

(22)申请日 2019.04.26

(71)申请人 海光信息技术有限公司

地址 300384 天津市滨海新区天津华苑产

业区海泰西路18号北2-204工业孵化-

3-8

(72)发明人 高玲

(74)专利代理机构 上海知锦知识产权代理事务

所(特殊普通合伙) 31327

代理人 段洁汝 李丽

(51)Int.Cl.

H03L 7/085(2006.01)

H03L 7/099(2006.01)

H03L 7/197(2006.01)

(54)发明名称

一种全数字锁相环电路

(57)摘要

本发明实施例公开了一种全数字锁相环电

路,所述全数字锁相环电路包括:数字控制振荡

电路,以及与所述数字控制振荡电路耦接的锁定

电路;所述数字控制振荡电路适于生成振荡信

号;所述锁定电路适于基于所述振荡信号的生成

频率确定所述数字控制振荡电路的频率锁定完

成后,响应于参考信号的边沿的到来,输出锁定

反馈信号。

本发明实施例中的技术方案可以减少

全数字锁相环电路的相位锁定时间。

权利要求书2页 说明书7页 附图3页CN 110061738 A 2019.07.26

C N 110061738

A

权 利 要 求 书1/2页CN 110061738 A

1.一种全数字锁相环电路,其特征在于,包括:数字控制振荡电路,以及与所述数字控制振荡电路耦接的锁定电路;

所述数字控制振荡电路适于生成振荡信号;

所述锁定电路适于基于所述振荡信号的生成频率确定所述全数字锁相环电路的频率锁定完成后,响应于参考信号的边沿的到来,输出锁定反馈信号。

2.根据权利要求1所述的全数字锁相环电路,其特征在于,所述锁定电路包括:锁定控制信号生成电路,以及与所述锁定控制信号生成电路偶接的锁定反馈电路;

所述锁定控制信号生成电路适于响应于所述参考信号的边沿的到来,输出对应的锁定控制信号;

所述锁定反馈电路适于在所述锁定控制信号的控制下,选择对应的并行数据为输入,并输出对应的锁定反馈信号。

3.根据权利要求2所述的全数字锁相环电路,其特征在于,所述锁定反馈电路包括:数据选择电路,以及与所述数据选择电路耦接的串行电路;

所述数据选择电路与所述锁定控制信号生成电路耦接,适于基于所述锁定控制信号,选择并输出对应的并行数据;

所述串行电路适于读取所述并行数据,并输出对应所述并行数据的所述锁定反馈信号。

4.根据权利要求2所述的全数字锁相环电路,其特征在于,所述并行数据包括多位高电平并行数据以及多位低电平并行数据,所述锁定控制信号包括高电平的锁定控制信号以及低电平的锁定控制信号;

若所述锁定控制信号生成电路输出低电平的锁定控制信号,则控制所述锁定反馈电路选择低电平的并行数据输入;

若所述锁定控制信号生成电路输出高电平的锁定控制信号,则控制所述锁定反馈电路选择高电平的并行数据输入。

5.根据权利要求4所述的全数字锁相环电路,其特征在于,所述并行数据的位数与所述全数字锁相环电路的整数分频值相等。

6.根据权利要求1所述的全数字锁相环电路,其特征在于,所述锁定电路适于响应于所述参考信号的上升沿的到来,输出高电平的锁定反馈信号。

7.根据权利要求1所述的全数字锁相环电路,其特征在于,所述锁定电路包括:计数电路,以及与所述计数电路耦接的比较电路;

所述计数电路适于在所述参考信号的每一信号周期内,对所述数字控制振荡电路生成的振荡信号的数量进行计数,以根据计数数量确定所述数控振荡电路生成所述振荡信号的生成频率;

所述比较电路适于比较所述振荡信号的计数数量与所述全数字锁相环的整数分频值确定所述全数字锁相环电路的频率锁定是否完成。

8.根据权利要求7所述的全数字锁相环电路,其特征在于,若所述计数数量小于所述全数字锁相环的整数分频值,则确定所述全数字锁相环电路的频率锁定未完成,否则,确定所述全数字锁相环电路的频率锁定完成。

9.根据权利要求1所述的全数字锁相环电路,其特征在于,所述全数字锁相环电路还包

2。