基于FPGA的高速图像处理系统的设计

基于FPGA的图像处理算法设计与实现

基于FPGA的图像处理算法设计与实现随着计算机科学技术的不断发展,图像处理技术也日益成熟。

基于FPGA的图像处理算法是目前较为常见的一种方式,它具有比较高的实时性和灵活性,能够满足不同场景的要求。

本文将介绍基于FPGA的图像处理算法设计与实现。

一、FPGA概述FPGA全称为“现场可编程门阵列”,是一种由大量可编程门电路组成的芯片,可按照设计人员的需求进行编程,从而实现不同的功能。

FPGA具有高度的可重构性和可编程性,能够适应多种复杂系统的要求,因此被广泛应用于图像处理、信号处理、视频处理等领域。

二、图像处理算法简介图像处理算法是基于数字图像进行的数学分析和计算,目的是对图像进行多种操作和变换,使得其更加适合特定的应用场景。

常见的图像处理算法包括锐化、模糊、边缘检测、傅里叶变换等。

三、基于FPGA的图像处理算法设计与实现基于FPGA的图像处理算法主要包括以下几个步骤:1. 图像输入与预处理在FPGA芯片中输入图像数据之前,需要对其进行预处理。

常见的预处理方式包括:色彩空间转换、图像压缩、图像大小调整等。

这些预处理步骤能够使输入的图像更加适合后续的处理流程。

2. 图像处理算法设计每个图像处理算法都需要一个符合其要求的算法设计文档,其中需要包括处理算法描述、输入输出格式、核心代码等。

这些文档应该由专业的图像处理算法设计师完成,并经过验证和测试,以确保其可靠性和正确性。

3. FPGA硬件编程在上述文档完成之后,需要将其转化为FPGA上的硬件描述语言,以便在FPGA芯片中进行硬件编程。

常见的硬件编程语言包括:Verilog、VHDL、SystemVerilog等。

设计师需要根据硬件语言的特性,编写相应的代码和模块,以实现图像处理算法功能。

4. 设计模拟与验证在硬件编程完成之后,需要对其进行模拟和验证,以确保其符合设计的要求。

设计师可以使用仿真器或模拟器进行模拟和验证,并对其进行修正和调整,以达到最佳的效果。

基于FPGA的图像处理加速技术研究

基于FPGA的图像处理加速技术研究随着科技的发展,图像处理技术逐渐成为人们生活中不可或缺的一部分。

同时,图像处理技术也逐渐面临着越来越广泛的应用需求。

在这样的背景下,基于FPGA的图像处理加速技术应运而生。

本文将探讨基于FPGA的图像处理加速技术研究的现状和未来发展方向。

一、FPGA技术概述FPGA(Field-Programmable Gate Array)中文名叫现场可编程门阵列,是一种可编程逻辑芯片,可以在上面设计出各种数字逻辑电路,并对其进行编程实现。

与ASIC(Application-Specific Integrated Circuit)芯片相比,FPGA芯片实现的功能更加灵活,兼容性更好。

二、FPGA在图像处理中的应用FPGA在图像处理中的应用十分广泛,可以实现数字图像处理、数字信号处理、图像滤波、边缘检测、图像分割、图像增强、运动估计和运动补偿等。

对于图像处理中的复杂计算问题,FPGA可以通过并行计算进行高速处理,从而大大提高了图像处理效率。

此外,FPGA的高灵活性和强大的可编程性也为图像处理领域带来了更多的技术创新。

三、基于FPGA的图像处理加速技术研究现状当前,基于FPGA的图像处理加速技术已经被广泛应用于多个领域,例如医疗图像处理、视频图像处理和视觉传感器等。

其中,医疗图像处理是最为广泛应用的领域之一。

在医疗图像处理中,FPGA可以处理放射性图像、磁共振图像和计算机断层扫描图像等医疗图像,可以实现图像去噪、图像增强和图像分割等功能。

此外,基于FPGA的图像处理加速技术还被广泛应用于军事图像处理和安防图像处理领域。

在军事领域,FPGA可以实现高速图像传输和实时图像分析。

在安防领域,FPGA可以实现人脸识别、车牌识别和动态目标检测等功能。

四、基于FPGA的图像处理加速技术研究未来发展方向随着科技的不断发展,基于FPGA的图像处理加速技术也面临着更广阔的发展空间。

未来,基于FPGA的图像处理加速技术将继续向多媒体领域、虚拟现实领域逐步拓展。

基于FPGA和USB3.0的高速视频图像采集处理系统设计

摘要随着机器视觉的广泛应用,以及工业4.0和“中国制造2025”的提出,在数字图像的采集、传输、处理等领域也提出了越来越高的要求。

传统的基于ISA接口、PCI接口、串行和并行等接口的图像采集卡已经不能满足人们对于高分辨率、实时性的图像采集的需求了。

一种基于FPGA和USB3.0高速接口,进行实时高速图像采集传输的研究越来越成为国内外在高速图像采集研究领域的一个新的热点。

针对高速传输和实时传输这两点要求,通过采用FPGA作为核心控制芯片与USB3.0高速接口协调工作的架构,实现高帧率、高分辨率、实时性的高速图像的采集和传输,并由上位机进行可视化操作和数据的保存。

整体系统采用先硬件后软件的设计方式进行设计,并对系统各模块进行了测试和仿真验证。

通过在FPGA 内部实现滤波和边缘检测等图像预处理操作,验证了FPGA独特的并行数据处理方式在信号及图像处理方面的巨大优势。

在系统硬件设计部分,采用OV5640传感器作为采集前端,选用Altera的Cyclone IV E系列FPGA作为系统控制芯片,由DDR2存储芯片进行数据缓存,采用Cypress公司的USB3.0集成型USB3.0芯片作为数据高速接口,完成了各模块的电路设计和采集卡PCB实物制作。

系统软件设计,主要分为FPGA逻辑程序部分、USB3.0固件程序部分和上位机应用软件部分。

通过在FPGA上搭建“软核”的方式,由Qsys系统完成OV5640的配置和初始化工作。

由GPIF II接口完成FPGA和FX3之间的数据通路。

通过编写状态机完成Slave FIFO的时序控制,在Eclipse中完成USB3.0固件程序的设计和开发。

上位机采用VS2013软件通过MFC方式设计,从而完成整体图像采集数据通路,并在上位机中显示和保存。

整体设计实现预期要求,各模块功能正常,USB3.0传输速度稳定在320MB/s,通过上位机保存至PC机硬盘的图像分辨率大小为1920*1080,与传感器寄存器设置一致,采集卡图像采集帧率为30fps,滤波及边缘检测预处理符合要求,采集系统具有实际应用价值和研究意义。

基于FPGA和DSP的高速图像处理系统设计

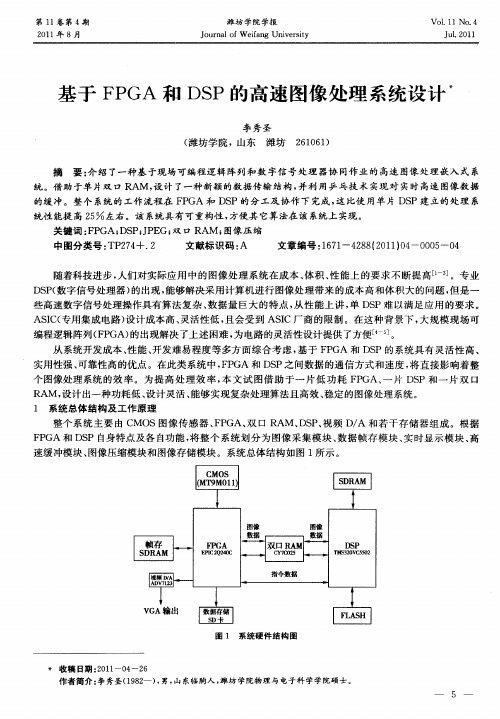

的缓 冲 。整 个 系统的 工作 流 程 在 F GA 和 D P的分 工 及协 作 下 完成 , 比使 用单 片 DS P S 这 P建 立 的处 理 系

统性 能提 高 2 左右 。该 系统 具 有可重 构性 , 5 方便 其 它算 法在该 系统上 实现 。

关键 词 : P F GA; S J E 双 口 RAM ; D P;P G; 图像 压 缩

第 1 卷 第 4期 1

21 0 1年 8月

潍 坊 学 院 学报

J u n l fW efn ie st o r a ia g Unv r i o y

V0 . 1N0 4 11 .

J 12 1 u. 0 1

基 于 F GA 和 DS P P的 高 速 图 像 处 理 系 统设 计

确 的配置之后 , 就可 以输 出 1 的图像数据 和一些 同步信 号 。在本系统 中采用 I O位 z C实现 传感 器配 置 ,P F— G 管脚通 过模拟 IC时序 , A 。 完成 对 C MOS 感器 的初始 化配置 , 中要 配置 的寄存 器如表 1 传 其 所示 。

表 1 MT M0 9 1寄存 器 设 置

编程逻 辑 阵列 ( P F GA) 出现解 决 了上 述 困难 , 电路 的灵活 性设 计提 供 了方便 [ 。 的 为 4 ]

从 系 统开发 成本 、 能 、 性 开发难 易程 度等 多方 面综 合考 虑 , 基于 F G 和 D P的系 统具 有 灵 活性 高 、 P A S 实用性 强 、 可靠性 高 的优 点 。在此类 系 统 中 ,P F GA和 DS P之 间 数据 的通 信 方式 和速 度 , 直 接影 响着 整 将 个 图像 处理 系统 的效 率 。为 提 高 处 理 效 率 , 文 试 图 借 助 于 一 片 低 功耗 F GA、 片 D P和 一 片 双 口 本 P 一 S

基于FPGA的图像处理硬件设计与实现

基于FPGA的图像处理硬件设计与实现概述:图像处理是数字信号处理领域的重要应用领域之一,它在计算机视觉、医学影像、图像识别等方面有着广泛的应用。

FPGA(Field Programmable Gate Array)作为一种可编程逻辑器件,具有并行计算能力和高速数据处理能力,特别适合用于图像处理的硬件设计与实现。

本文将介绍基于FPGA的图像处理硬件设计的基本流程和关键技术,以及实现一个基于FPGA的图像滤波系统的案例。

第一部分:图像处理硬件设计的基本流程1. 系统需求分析:在进行图像处理硬件设计之前,首先需要明确系统的需求和目标。

包括图像处理的功能要求、延迟要求、资源利用率要求等。

2. 硬件平台选择:选择适合图像处理的FPGA开发板或芯片。

根据系统需求,考虑各种性能指标,如时钟频率、资源量、功耗等。

3. 硬件架构设计:设计图像处理系统的硬件架构,包括模块划分、数据通路设计、控制器设计等。

4. 算法实现:根据图像处理的算法和功能需求,将算法转化为硬件设计的形式。

对于复杂的算法,可以采用高层次综合工具进行优化。

5. RTL设计与验证:使用硬件描述语言如VHDL或Verilog来进行RTL (Register Transfer Level)级别的设计和验证。

通过仿真验证电路设计的正确性和功能实现。

6. 综合与布局布线:对RTL设计进行综合优化,将其映射到目标FPGA平台的可用资源上,再进行布局布线。

7. 系统集成与调试:将各个模块进行集成并进行整体调试,确保系统的稳定性和性能。

第二部分:基于FPGA的图像滤波系统设计与实现案例在本部分,我们以图像滤波为例,展示一个基于FPGA的图像处理系统的设计与实现。

1. 系统需求分析:我们的目标是实现一个基于FPGA的图像平滑滤波器。

我们需要处理彩色图像,具体要求为:支持不同尺寸的图像输入,实现高质量的平滑滤波效果,并且具备实时处理的能力。

2. 硬件平台选择:我们选择了一款高性能的FPGA开发板,该板上搭载了一颗高性能的FPGA芯片,具有丰富的资源和高时钟频率。

基于fpga的数字图像处理原理及应用

基于FPGA的数字图像处理原理及应用1. 引言数字图像处理作为一项重要的技术,已经被广泛应用于多个领域,例如医疗影像、机器视觉和图像识别等。

而基于FPGA(Field-Programmable Gate Array)的图像处理系统已经成为研究的热点。

本文将介绍基于FPGA的数字图像处理原理及其应用。

2. FPGA的基本原理和特点FPGA是一种可重构的硬件设备,具有可在现场编程的特点,使其适用于不同应用的实时高性能图像处理。

FPGA拥有可配置的逻辑单元和内部存储器,可用于实现各种数字图像处理算法。

3. FPGA在数字图像处理中的应用3.1 图像滤波•FPGA可以实现图像滤波算法,例如均值滤波、中值滤波和高斯滤波等。

•FPGA的并行计算能力使得图像滤波可以以实时高性能的方式进行。

3.2 图像边缘检测•基于FPGA的图像边缘检测算法可以有效地提取图像的边缘信息,用于目标识别和图像分割等应用。

•FPGA的并行处理能力和灵活的逻辑结构使得边缘检测算法可以以高效的方式实现。

3.3 图像增强•FPGA可以用于实现图像增强算法,例如直方图均衡化和灰度级调整等。

•FPGA的硬件并行性使得图像增强算法可以在实时性要求较高的应用中得到广泛应用。

3.4 图像压缩•FPGA可以实现图像压缩算法,例如JPEG压缩算法。

•FPGA的高速并行处理能力使得图像压缩可以以实时高效的方式进行。

4. FPGA在数字图像处理中的优势•FPGA具有硬件并行处理能力,可以实现高效的图像处理算法。

•FPGA具有灵活性,可以根据不同的应用需求进行编程和配置。

•FPGA具有低功耗和低延迟的特点,适用于实时性要求较高的图像处理应用。

•FPGA具有较高的计算性能和吞吐量,可以满足高帧率的图像处理需求。

5. FPGA在数字图像处理中的应用案例5.1 医疗影像处理•基于FPGA的医疗影像处理系统可以用于实时的医学图像分析和诊断。

•FPGA的硬件并行处理能力可以提高医疗图像处理系统的性能和效率。

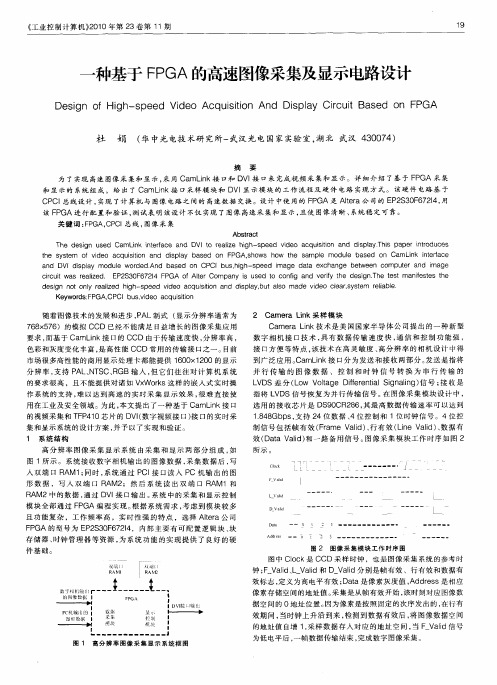

一种基于FPGA的高速图像采集及显示电路设计

1 9

一

种基于 F G P A的高速图像采集及显示电路设计

De i f Hi —s e d Vi o Ac ust n An Dip a r utBa e o P sgn o gh— p e de q iio d i s ly Ci i c s d n F GA

选 用 的 接 收 芯 片是 DS 0 R 8 , 最 高 数 据 传输 速 率 可 以达 到 9 C 2 6其

该 F G 进 行 配 置和 验 证 , 试 表 明该 设 计 不仅 实现 了 图像 高 速 采 集和 显 示 , 使 图像 清 晰 、 PA 测 且 系统 稳 定 可 靠 。

关 键 词 :P F GA, Cl CP 总线 , 图像 采 集

Ab ta t s rc

Th si u e Ca Ln nera e nd e de gn s d m ik it f c a DVI o r al e i -s ed i a qust d t e i hgh pe vdeo c iion an diply.hi z i s a T s pap itodu es er nr c t e y tm of i a quiion nd h s se vdeo c st a diply a d i s a b se on PGA,h ws o F s o h w t s m pl m o e he a e dul ba ed s on Cam Lnk n e ce i it da an DVI s a o e d diply m dul wor d. d de An ba ed n s o CP bu ,i Cl shgh- ee i a da a ex h ge et e c sp d m ge t c an b we n ompu e an i tr d mag e ci ui wa r aied. EP 30 7 4 FP r t c s el z 2S F6 21 GA o t m p y i u e t n i d ery h de i . e es manfses h fAl Co an s s d o co fg an v i te er f sgnTh t t i t te e de i n tonl eaied i sgn o y r l z hgh—s ee vdeo a p d i cqust a d iion n diply, talo m a de ea ,y tm r i l i s a bu s de vi o cl rs se el e ab Ke wo d : P y r s F GA. Cl s, de a quiion CP bu vi o c st i

基于FPGA的图像处理系统设计与实现

基于FPGA的图像处理系统设计与实现图像处理是计算机视觉领域中的重要技术之一,可以对图像进行增强、滤波、分割、识别等操作,广泛应用于医学图像处理、工业检测、安防监控等领域。

而FPGA(Field Programmable Gate Array)可编程门阵列,则是一种自由可编程的数字电路,具有并行处理能力和灵活性。

本文将介绍基于FPGA的图像处理系统的设计与实现。

一、系统设计流程1. 系统需求分析:首先需要明确图像处理系统的具体需求,例如实时性、处理的图像类型、处理的算法等。

根据需求,选择合适的FPGA芯片和外设。

2. 图像采集与预处理:使用图像传感器或摄像头采集图像数据,然后对图像进行预处理,如去噪、增强、颜色空间转换等,从而提高后续处理的准确性和效果。

3. 图像处理算法设计与优化:根据具体的图像处理需求,选择适合的图像处理算法,并对算法进行优化,以提高处理速度和效率。

常用的图像处理算法包括滤波、边缘检测、图像分割等。

4. FPGA硬件设计:基于选定的FPGA芯片,设计硬件电路,包括图像存储、图像处理模块、通信接口等。

通过使用硬件描述语言(如Verilog、VHDL)进行功能模块设计,并进行仿真和验证。

5. 系统集成与编程:将设计好的硬件电路与软件进行集成,包括FPGA程序编写、软件驱动开发、系统调试等。

确保系统的稳定运行和功能实现。

6. 系统测试与优化:对整个系统进行完整的测试和验证,包括功能性测试、性能测试、稳定性测试等。

根据测试结果,对系统进行优化,提高系统的性能和可靠性。

二、关键技术及挑战1. FPGA芯片选择:不同的FPGA芯片具有不同的资源和性能特点,需要根据系统需求选择合适的芯片。

一方面需要考虑芯片的处理能力和资源利用率,以满足图像处理算法的实时性和效果。

另一方面,还需要考虑芯片的功耗和成本,以便在实际应用中具有可行性。

2. 图像处理算法优化:在FPGA上实现图像处理算法需要考虑到算法的计算复杂度和存储开销。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于FPGA的高速图像处理系统的设计摘要: 在本文中,设计了一个高速图像处理系统,是为了解决这样的问题,如出现在车载计算机图像处理中的低系统集成,低速的处理过程。

通过配置Nios II软核CPU和一些基于主要硬件FPGA的图像预处理,处理和显示的功能模块和设计的系统软件,使得该系统实现了图像的采集,记忆和重叠功能。

由于采用可编程芯片和并行处理技术,该系统集成度高,好维修,图像处理速度快、实时性强。

关键词:图像处理,FPGA,Nios II CPU。

I.介绍近年来,车载计算机中存在的主要问题集中在两个方面。

首先,在使用低功率损耗的PowerPC CPU的状态下,对于图像的采集和显示,一个集成板是必需的。

其次,随着视频图像和红外热像仪的广泛使用,还有电子一体化的发展,应该设计出一个高速的图像处理系统。

为了解决这两个主要的问题,作者设计了一个基于FPGA的高速图像处理系统用来识别重叠的多通道图像信息。

功能模块,比如图像采集,处理和显示,都可以在一个单一的FPGA芯片上实现,它减少了外围电路,提高整个系统的性能。

因为并行处理技术,处理速度和实时性都大大的提高。

II.图像处理算法分析A.基于双线性插值的图像放大基于像素的放大倍率的方法原理简单、快速,但它只是复制原始像素的邻域。

随着放大系数增大,图像会出现明显的块锯齿,不能保留原始图像的边缘信息。

这个问题是可以通过双线性插值来解决。

双线性插值可以消除锯齿,保留原始图像的边缘信息和获得更好的视觉效果。

图1.原始图像(略)图2.放大图像(略)图1是原始图像,其中f ij,f i,j+1,f i+1,j,f i+1,j+1是相邻的像素块。

图2是在水平方向上放大K倍,在垂直方向放大L倍的图像。

f ij,f i,j+1,f i+1,j,f i+1,j+1在放大图像中只改变位置但像素值保持不变。

因此,我们可以得到以下方程:在放大的图像中,我们定义保留原始图像信息的数据作为初始数据,它的坐标值是原始图像的整数,还从原始图像的数据中定义需要插值运算的数据,这些插值数据的坐标值不是原始图像的整数倍数。

在进行插值,在初始位置的像素值数据保持不变,其他像素值通过插值算法计算。

具体算法如下。

设置放大图像中的像素位置为(x,y),在放大的图像和原始图像中坐标有以下关系:其中,x,y是放大的图像坐标;i,j是原始图像的坐标;K是横向放大倍数和L是垂直的放大倍数;0<u<1 ,0<V<1。

通过双线性插值我们可以计算出放大图像中的像素值公式(3)表明当像素点位于初始数据的位置时,像素值仅通过一次插值就可以计算出来,例如F(ki,l(j+v)),F(k(i+1),l(j+v)),当像素点位于插值数据的位置就需要三次插值。

公式(3)也表明,这些算式符合乘加模式而且很容易在FPGA芯片上实现。

结果是,该方法不仅保证了图像的放大效应也保证实时性的要求。

B.多通道图像重叠[4]1.Alpha通道α-通道是Alpha通道的缩写形式,除了基本的颜色通道,它决定了每个像素的透明度。

用每个通道的色值乘以它的α值用来确定它对像素的贡献。

Alpha通道使用不同的灰度级表示其透明的大小。

α值的变化从0到1,当α-通道有8位二进制数据的宽度时,它有256个层次的透明度。

白色的(α= 1,对应于255)是不透明的,黑色的(α= 0,对应于0)是完全透明的,黑与白之间的灰度值表示部分透明。

2.多通道图像重叠结合性:图像叠加处理符合结合性:根据结合公式演绎多通道图像重叠的。

设置为α1为前景I1的α值,而i1为I1的前景颜色。

设置α2作为前景I2的α值和i2为前景I2的颜色。

b表明背景的颜色,它的α值是1 。

对于(重叠的I1,B),色值由颜色i1在某像素点的采样值覆盖。

因为α1是I1的透明度,背景B中的像素的透明度为1~α1和色值(1 ~α1)b.全彩色的i1,b值是两个部分的总和:然后计算一个重叠的值(I1重叠B),我们得到i2,1,b的色值:对于重叠的I1 ,I2,设置α为重叠的图像的α值,而i作为其色值,那么重叠的B(I1 重叠I2)的色值将是αi+(1–α),立足于结合性我们有以下的公式:由于背景是随机的,两层图像的重叠公式可以由公式(7)得到。

该集成α-通道值是:在公式(8)里,把每个通道的色值乘以它的α值的结果称为预乘颜色。

I= αi,I2 =α2i2,I1 =α1i1,公式(8)的缩写形式是:用重叠公式与预乘颜色表示不仅使表达更加简单而且使颜色的集成和综合的α-通道值具有相同的表达形式。

当第三层I3和I2,I1重叠,其重叠公式可以从两层重叠公式推导出来。

设置I3 为第三层图像的预乘颜色而α3为其α-通道值,然后第三层图像的重叠的预乘颜色是:该集成α-通道值是:同样,n层图像的重叠的综合预乘颜色和集成α-通道值是:III.系统的总体设计该系统由Nios II软核CPU,图像预处理模块,图像显示模块,图像处理模块和通用外围接口组成。

图3显示的是系统的总体结构。

图3.系统总体结构(略)该系统集成了Altera开发的软核CPU,和作者自界定的SDRAM 控制器,通用输入/输出接口和图像的预处理,处理和显示模块。

每个模块靠Avalon总线连接和由Nios II CPU协调运行。

除了视频解码芯片,视频DAC芯片,存储器和键盘,该系统的其它部分都集成在FPGA芯片。

系统的工作过程如下。

来自摄像机的模拟视频信号通过解配置在I2C总线上的视频解码芯片解码,然后传输给图像预处理模块。

图像预处理模块对视频数据进行格式和去交错,然后将它存储到SDRAM。

有几个DMA通道这是在图像处理模块中定义的。

每个通道的图像在图像重叠模块中重叠。

显示控制器生成的扫描时间信号并通过DAC芯片将其由数字图像转换成模拟信号。

所有的功能模块系统工作在一个统一的时钟,并由Nios II CPU控制。

此外,用户可以通过键盘操作实现相应的图像处理功能。

IV.系统的硬件设计A:图像预处理模块的设计图像预处理模块包含itu-r656解码器,FIFO和输入DMA。

视频信号通过视频解码芯片解码后是交错的,应该分别分成奇数场和偶数场。

每一行数字视频信号的视频数据格式如图4所示。

“FF0000SAV”是标志有效的视频数据开始的时间参考代码。

“CB0 Y0 Cr0 Y1 cb2 Y2 CR2 Y3……cr718 y719”是符合itu-r656标准的有效视频数据。

“FF0000EAV”是标志有效的视频数据结束的时间参考代码。

图4.数字视频信号的数据格式(略)itu-r656解码器检测时间是根据代码“FF0000 SAV”,产生一个有效的线路信号,和开始解码后面的视频数据。

它将8的itu-r656数据转换为16位的YCrCb数据。

它也产生输入DMA的控制信号。

输入DMA 定义DMA的主端口。

一方面,它提供了写时显示的内存地址,数据而且写要求信号到Avalon总线,开始总线传输和存储YCrCb数据到SDRAM显示内层里;另一方面,它也为数据源去隔行,也就是说隔行信号转换成线线信号。

B.图像处理模块的设计图像处理模块包含两个DMA的主端口,数据缓冲区和图像重叠的子模块。

它如图5所示。

图5.图像处理模块(略)1.多通道DMA多通道DMA是Avalon总线的主端口设备。

它的职责是提供有效的地址,数据和读取时请求的信号到Avalon总线,并在时钟的上升沿时开始总线传输以读取存储的数据;同时,DMA模块产生的缓冲区的写入数据地址,正确的将数据从内存传到数据缓冲区。

当多通道DMA从不同的内存中读取数据时,每个DMA主端口可以工作在并行而不干扰。

然而,它读取的数据从相同的内存中时,DMA 在地址总线和数据总线之间将发生冲突。

要解决这个的问题,模块采用流水线设计。

每个DMA主端口在不同的时间占用地址总线和数据总线。

当第一DMA主端口使用总线,其他主端口等。

特定的时间延迟后,第一DMA主端口释放总线而其它的主端口争夺总线的使用权,然后重复。

延迟时间与存储器的读频率和显示频率的差值呈反比例。

2.重叠的子模块重叠的子模块能识别重叠的多通道图像信息。

各种渠道像素的透明度的alpha值和重叠区域的起始和结束地址在这个子模块里定义了。

以重叠的3通道图像比如说。

引用公式(11),图像重叠的算法可以很容易地在FPGA芯片实现因为它的乘加操作C.显示控制器这个模块是用来产生的扫描信号以驱动显示器,以及读取数据的缓存及读请求信号的地址信号。

同时也传达了当前过程地址到图像处理模块和控制有关的模块。

V.系统的软件设计系统软件运行在Nios II CPU。

自整个系统的功能模块都由硬件来设计,CPU只是配置了每个模块的寄存器和寄存器的从端口。

结果是,CPU的负担比较小;从而有效地提高系统的运行速度。

软件流程如图6所示。

VI.实验验证软件和硬件验证运行Altera的DE2板。

结果显示在图7。

图7(a)显示的图像在两个通道的图像重叠的。

图7(b)显示在视频图像重叠特征。

图6.软件流程(略)与传统的基于软件的图像处理系统相比,图像处理模块设计的主要优点如下:1.每个DMA通道可以并行工作,处理多通道图像信息的同时,高速图像数据处理。

2,硬件乘法器在FPGA的嵌入式应用取得了高速和实时计算的结果;3,利用嵌入式RAM资源作为图像数据的缓存存储部分(或几行)可以增加数据处理量;4,在该模块中,CPU只负责改变配置动态参数而不是参与到具体的加工操作中,因此,提高系统的速度。

图7(a)后两个通道的图像重叠图像(略)图7.(b)在视频图像叠加字符图像(略)图7.验证图像VII.结论这种基于FPGA的高速图像处理系统能够并行的获取和处理图像。

同一般的基于PC的图像处理系统相比,它具有集成度高,图像处理快和处理实时。

该系统在可编程芯片上实现了各种图像处理功能模块。

它不需要重新配置技术来改变硬件的结构。

现有的系统可以在线或者通过网络更新,这使得它广泛应用于很多领域。

参考文献略。