Xilinx ISE软件使用过程新(含PROM下载)

ISE开发环境使用指南[FPGA开发教程

ISE开发环境使用指南简介ISE(Integrated Software Environment)是Xilinx公司开发的一套FPGA设计软件工具。

本文档将为您介绍如何使用ISE开发环境进行FPGA开发,包括环境的安装、基本操作和常见问题解决方法。

环境安装1.在Xilinx官网上下载最新版本的ISE软件。

2.双击安装文件,按照向导指示完成安装过程。

3.完成安装后,打开ISE软件,进行必要的设置和配置。

基本操作创建工程1.打开ISE软件,选择“File” -> “New Project”。

2.在弹出的对话框中输入工程名称和路径,选择FPGA型号等相关参数,点击“Next”。

3.添加源文件和约束文件,点击“Next”。

4.点击“Finish”完成工程创建。

编译工程1.在ISE软件中选择“Project” -> “Run Implementation”进行工程编译。

2.检查编译过程中是否有错误,根据提示进行修正。

下载到FPGA1.将FPGA与电脑连接,选择“Tools” -> “iMPACT”打开下载工具。

2.配置下载参数,选择对应的FPGA型号和文件路径。

3.点击“Program”开始下载程序到FPGA。

常见问题解决方法编译错误•检查代码中是否有语法错误或逻辑问题。

•检查约束文件是否设置正确。

下载失败•检查FPGA与电脑的连接是否正常。

•检查下载工具配置是否正确。

总结通过本文档的介绍,您应该对如何使用ISE开发环境进行FPGA开发有了一定了解。

希望您在实际操作中能够顺利完成项目的开发和调试。

如果遇到任何问题,可以参考本文档中提供的常见问题解决方法或参考Xilinx官方文档进行进一步学习和搜索。

ISE使用指导

-3-

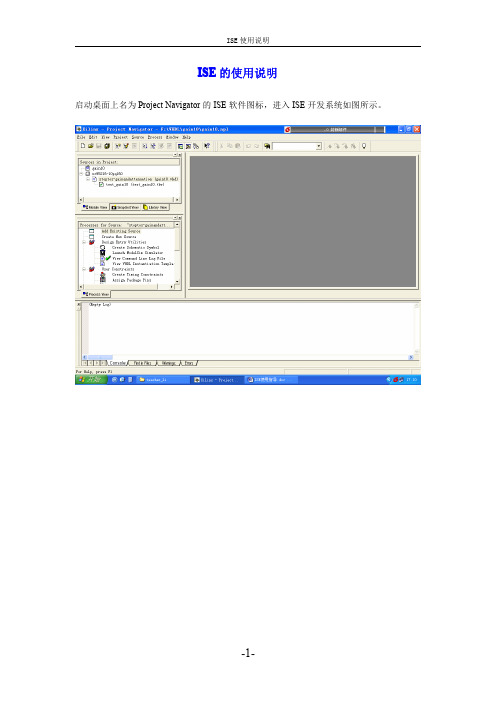

ISE 使用说明

下一步,进行可编程器件型号的选择以及设计流程的设置。在器件型号栏有 Device family , Device (型号) ,封装,speed grade,可以根据实验平台所用的可编程逻辑器件分别设置相 应选项。对话框下半部分是对设计语言和综合仿真工具的选择。

然后下一步,采用默认设置,完成了 New Project Information 的设置。如图所示:

-9-

ISE 使用说明

count<="000000"; end if; elsif flag='1' and flag1='1' then if count<59 then count<=count+1; elsif count>=59 then count<="000000"; end if; end if; end if; end process; end Behavioral; -- flag='1' , 则进行 60 进制计数

然后单击工程 counter 下的子目录 count-Behavioral(count.vhd) , 接着在界面的 Processes for Source 一栏选择 Implement Design,进行布局布线的综合:

-15-

ISE 使用说明

然后工程名 counter 上单击右键,弹出对话框,选择新建 Test Bench Waveform,在 file 命名 为 test_counter。

在界面的 Processes for Source 一栏,是一系列综合工具。 Synthesize XST 工具一般可以分析 代码的语法错误,查看错误报告和 RTL 级的电路设计图。 单击 View Synthesis,出现如图所示对话框:

ISE软件使用说明(两篇)

引言:概述:ISE软件是由Xilinx公司开发的一款集成电路设计工具,使用该软件可以进行数字电路设计、仿真、验证以及实现等多个阶段的工作。

在设计阶段,ISE软件提供了丰富的组件库和设计工具,方便用户进行电路原理图的绘制和逻辑设计。

在验证阶段,ISE软件可以进行功能仿真和时序仿真,以确保设计的正确性和稳定性。

在实现阶段,ISE软件提供了先进的布局与布线工具,能够将设计转化为实际的电路板。

正文内容:1.安装与启动1.1ISE软件安装包1.2安装ISE软件1.3启动ISE软件2.项目管理2.1创建新项目2.2导入已有项目2.3添加设计文件2.4设定项目属性2.5保存和备份项目3.设计流程3.1电路原理图设计3.1.1组件选择3.1.2连接元件3.1.3设置元件属性3.2逻辑设计3.2.1设计约束3.2.2逻辑优化3.2.3时序约束3.3约束文件编辑3.3.1约束规则3.3.2约束语法3.3.3约束检查3.4时序仿真3.4.1创建仿真波形3.4.2设定初始状态3.4.3运行仿真3.5功能仿真3.5.1设置输入信号3.5.2运行仿真3.5.3分析仿真结果4.仿真与验证4.1时序分析4.1.1设定时钟4.1.2时序路径分析4.1.3时序优化4.2时序约束验证4.2.1满足约束4.2.2修复时序错误4.3灵敏度分析4.3.1设定输入敏感性4.3.2分析敏感性4.4逻辑分析4.4.1切换敏感性4.4.2分析逻辑状态5.布局与布线5.1物理约束5.1.1面积约束5.1.2信号完整性约束5.1.3电源与接地约束5.2布局5.2.1网表导入5.2.2管理物理资源5.2.3进行布局布线5.3时序优化5.3.1满足时序约束5.3.2缩短信号传输路径5.3.3优化时钟分配5.4布线5.4.1管理布线资源5.4.2进行布线5.4.3路由与优化5.5设计规约检查5.5.1检查布局布线规约5.5.2修复设计规约错误总结:引言概述:ISE软件是一款功能强大的集成开发环境工具,广泛应用于数字电路设计和实现。

Xilinx ISE使用流程1

Xilinx ISE使用流程(从新建项目到仿真执行)最近在忙着做毕业设计(计算机专业,非电子专业),从小就喜欢电子技术,但由于之前没有接触过FPGA,所以特意跑书店买了一本《Xilinx FPGA数字设计》一书,这本书同时用VHDL和Verilog HDL两种语言讲解,使用的示例非常简洁明了,是一本非常适合入门的图。

我在学习VHDL的时候,发现网上资料很少,所有决定把自己所学的知识和心得分享给广大网友,以便初学FPGA的同学们可以快速掌握Xilinx ISE工具的应用。

注意:阅读本篇文章需要数字电路和C语言等语言基础,本篇文章的代码示例出自《Xilinx FPGA数字设计》,请大家尊重版权。

我使用的Xilinx版本为ISE 14.2。

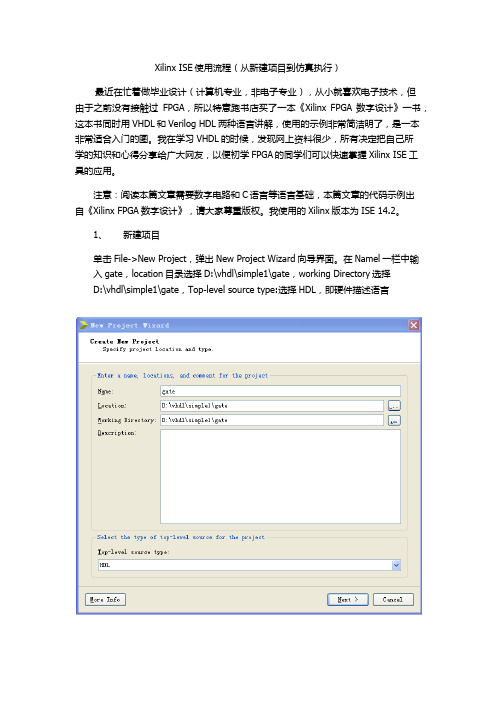

1、新建项目单击File->New Project,弹出New Project Wizard向导界面。

在Namel一栏中输入gate,location目录选择D:\vhdl\simple1\gate,working Directory选择D:\vhdl\simple1\gate,Top-level source type:选择HDL,即硬件描述语言单击Next,选择芯片型号和封装等,其中,芯片大家可以选择自己喜欢的,Synthesis Tool(综合工具)选择XST (VHDL/Verilog),Simluator(仿真工具)选择ISim (VHDL/Verilog),当然你也可以选择Modesim工具,Preferred Language(偏好语言)选择VHDL,VHDL Source Analysis Standard(VHDL语言分析标准)选择VHDL-200X单击Next,进入Project Summary页面,单击Finish,这一节我就不截图了。

进入程序主界面,我们可以看到一个空视图(Empty View),如下图:接下来我们要添加源代码了,在Hierarchy(层级)面板中选中XC6SLX16-3CSG324节点,右键单击New Source菜单,弹出New Source wizard向导界面,选中VHDL Module树节点,在右侧的File name输入gate。

Xilinx ISE Design Suite 13.4 软件使用流程(EDK和SDK部分)

Xilinx ISE Design Suite 13.4 软件使用流程(EDK与SDK部分)ISE的全称为Integrated Software Environment,即“集成软件环境”,是Xilinx公司的硬件设计工具。

相对容易使用的、首屈一指的PLD设计环境!ISE将先进的技术与灵活性、易使用性的图形界面结合在一起,不管您的经验如何,都让您在最短的时间,以最少的努力,达到最佳的硬件设计。

EDK=Embedded Development Kit,嵌入式开发套件。

EDK是xilinx公司开发嵌入式系统的工具。

比起xilinx的ISE,二者不同在于,如果仅仅是使用xilinx的fpga做逻辑设计,只需要ISE开发环境。

但是如果要使用powerpc或者microblaze处理器,从硬件到软件设计的整个嵌入式系统设计,就需要EDK。

SDK(Software Development Kit, 即软件开发工具包)一般是一些被软件工程师用于为特定的软件包、软件框架、硬件平台、操作系统等建立应用软件的开发工具的集合。

我是一个刚刚接触Xinlinx公司开发的fpga。

在对软件使用中遇到很多问题,在网上很难找到完全匹配的教程。

特别是在EDK的使用过程中,网上流传的教程都是基于老版本的。

步骤上有一些差异,对初学者来说往往不知所云,官网上的英文资料也存在一定的理解问题。

因此在此介绍一些EDK的使用步骤。

在老版本的EDK中。

硬件逻辑和软件工程是在一个EDK软件中的。

而版本比较新一点的,需要EDK硬件工程部分和SDK软件工程部分结合使用。

以下为具体的使用步骤,在解说的过程中不免出现错误。

还希望朋友们给以宝贵的意见。

1.首先点击电脑中的Xilinx Platform Studio 快捷方式,打开EDK软件。

如果桌面上没有快捷方式,也可以在开始——所有程序----Xilinx ISE Design Suite 13.4——EDK——Xilinx Platform Studio。

ISE软件使用说明

说明这个说明主要介绍了使用开发板可能使用到的3个工具,主要以串口功能的实现作为例子,讲述了ISE, Plantform和EDK的使用方法以及操作的基本流程。

ISE的使用一.启动Xilinx ISE:开始Æ所有程序ÆXilinx ISE 7.1iÆProject Navigator二.新建/打开一个工程:如果已经有了工程,则在FileÆOpen Project弹出的对话框里面选择你的工程。

如果没有合适的工程就需要通过FileÆNew Project来新建一个工程。

具体操作步骤如下:分别在Project Name和Project Location里面填写您想要创建的工程的名称和路径。

在Top-Level Module Type的下拉菜单里面选择您的工程的顶层模块的类型。

本次串口通信的实验的顶层为原理图,所以选择Schematic。

然后点击下一步:在这个对话框的上半部分选择您使用的芯片的族(Spartan3),型号(xc3s400),封装(pq208)和速度(-4)。

下面选择您要使用编译和综合的软件,建议使用ISE自带的软件,一是使用简便,二是Xilinx公司对自己的FPGA了解程度比第三方要高很多,所以使用Xilinx公司自己的软件有的时候会获得意想不到的收获。

具体参数选择如图,然后单击下一步:在这个对话框里面新建工程里面的文件,这步也可以放到后面来实现,这里我们先选择下一步:这一步用来添加已经存在的文件,同样,我们在后面实现这步。

点击下一步:在最后这个对话框里面显示了我们即将建立的工程的详细信息,确认无误以后点击完成,ISE将为您创建一个名字为uart_test的工程:三.为刚创建的工程添加源文件:1.添加已经存在的源文件:选中屏幕右上的xc3s400-4pq208,单击ProjectÆAdd Source,在弹出的对话框里面选择您已经存在的程序文件(.v .vhd)。

【精品博文】图文详解XilinxISE14.7安装教程

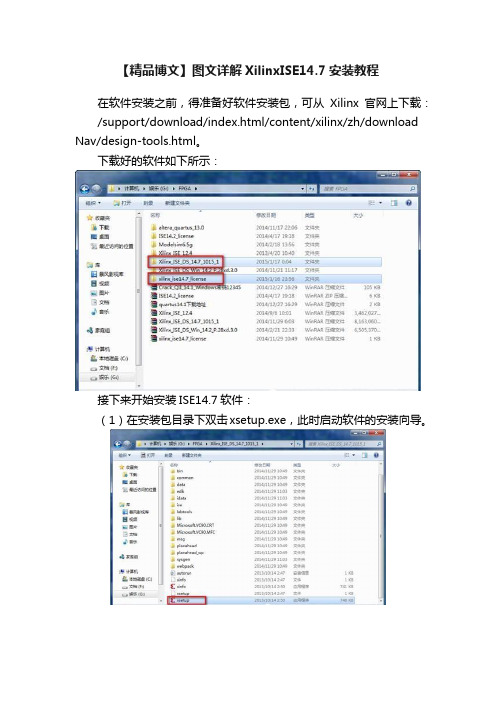

【精品博文】图文详解XilinxISE14.7安装教程在软件安装之前,得准备好软件安装包,可从Xilinx官网上下载:/support/download/index.html/content/xilinx/zh/download Nav/design-tools.html。

下载好的软件如下所示:接下来开始安装ISE14.7软件:(1)在安装包目录下双击xsetup.exe,此时启动软件的安装向导。

这是安装欢迎界面,直接Next~~(2)选中复选框,表示接受条目(必选,否则无法进行下一步),Next~~(3)同样必须接受条目,Next~~(4)选择要安装的软件类型,根据大家需求进行选择,这里选“ISE Design Suite System Edition”,Next~~(5)什么都不做,直接Next~~(6)选择安装路径,根据大家磁盘情况进行设置,这里为C盘,Next~~(7)这是对前面的设置进行的总结页面,点“Install”进行安装。

这个安装过程是一个漫长的过程,你得耐心等待,也可以找点事情做(我就去饭堂吃饭了,呵呵)(8)当安装进程到达86%时会弹出一个对话框,叫你安装跟网络通信有关的软件,如下所示:这里我们对它进行安装,直接Next,I Agree,Install,Finish~~(9)此时出现了一个安装设备的对话框,选择“安装”。

(10)同样选择“安装”。

(11)弹出为System Generator关联MATLAB软件的对话框,大家电脑有装过合适版本的MATLAB,可以对它进行关联,或者以后再关联,这里选择“Ok”跳过。

(12)接下来配置license。

由于我的电脑里已有license,故选择“Locate Existing License”,Next~~(13)点击“Load license”。

选择“打开”后,弹出以下对话框,选择“Yes”、“OK”~~(14)加载license后,直接“Close”、“Finish”完成安装~~(15)此时桌面出现了两个快捷方式,双击“ISE Design Suite 14.7”开始启动软件~(16)现在就可以开始使用ISE了,呵呵~~。

ISE8.2开发使用步骤

打开ISE8.2i软件:双击桌面快捷方式或者按步骤Start →All Programs →Xilinx ISE 8.2i →Project Navigator打开ISE软件。

建立新工程:1.点击File,选择New Project,打开新工程创建向导。

2.在工程名字中输入led_test。

并将工程保存在自己想保存的位置:F:\FPGA_study\ISE_project。

3.在Top-Level Source Type选择项中选择HDL,然后点next进行下一步。

4.在对话框“New Project Wizard – Device Properties”中,按下图选择工程的器件配置。

然后点击next进行下一步5.点next。

6.点next。

7.点Finish。

创建Verilog资源1.在sources窗口中右击,选择new source。

如下图。

2.选择Verilog Module,并在File name中输入led_test。

点击next。

3.在对话框中Port Name栏中分别输入CLOCK和led,其中CLOCK为输入;led为输出,且led的Bus一栏打上勾,并在MSB一栏输入数字7。

然后点next。

4.选择Finish。

生成的文件窗口如下图。

5.编辑文件“led_test.v”module led_test(CLOCK, led);input CLOCK;output [7:0] led;reg [7:0] led;reg [22:0] count = 0;parameter bit1 = 8'b0000_0001,bit2 = 8'b0000_0010,bit3 = 8'b0000_0100,bit4 = 8'b0000_1000,bit5 = 8'b0001_0000,bit6 = 8'b0010_0000,bit7 = 8'b0100_0000,bit8 = 8'b1000_0000;always @(posedge CLOCK)begincount <= count + 1;if(count == 4000000)count <= 0; //每100ms变一次0 endalways @(posedge CLOCK)beginif(count == 1)begincase(led)bit1: led <= bit2;bit2: led <= bit3;bit3: led <= bit4;bit4: led <= bit5;bit5: led <= bit6;bit6: led <= bit7;bit7: led <= bit8;bit8: led <= bit1;default: led <= bit1;endcaseendendendmodule检查所写的程序代码是否有误1.在Sources窗口的下拉项中选择Synthesis/Implementation。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Xilinx ISE 13.4软件使用方法

本章将以实现一个如图所示的4为加法器为例,来介绍Xilinx ISE13.4开发流程,并且最终下载到实验板BASYS2中运行。

1

A 1

1.建立工程

运行Xilinx ISE Design Suite 13.4,初始界面如图F2所示

F1 软件初始状态表

选择File->New Project ,该对话框显示用向导新建工程所需的步骤。

在Name 栏中输入工程名称(注意:以下所有不能含有中文字符或空格),如“test”。

在Location 栏中选择想要存放的工程位置,如“E:\code\Xilinx\test”。

顶层语言选项栏中选择“HDL”语言。

设置向导最终设置效果如图F2所示

F2 路径信息设置表

点击“Next”,进入芯片型号选择界面。

在本界面中,根据BASYS2实验板上的芯片型号进行相关设置,设置效果如图F3所示。

F3 芯片信息选择表

点击“Next”,出现如图F4所示工程信息汇总表格。

F4 工程信息汇总表

点击“Finish”完成设置。

2新建Verilog文件

在F5所示界面中,如图所示的区域内右击鼠标,选择“New Source”,出现F6对话框。

F5

在File name栏中键入verilog文件的名称,如“test”。

F6

点击“Next”,在本界面中将设置加法器的输入输出引脚数量,如图F1所示的加法器共有A、B、C0、S和C1,5组引脚,其中A、B和S为4位总线形式,因此设置结果如图F7所示。

F7

点击“Next”,出现Verilog新建信息汇总表。

F8

点击“Finish”,完成Verilog新建工作。

3逻辑设计

输入代码

在输入完成后,双击“Check Syntax”对代码进行语法检测。

F9

4.仿真验证

在完成语法检测模块后,可以根据需要对系统进行仿真测试,下面将详细介绍具体的实验步骤。

首先,点击如图F10所示的“Simulation”选项,将当前工程切换至仿真模式下。

F10

然后,在如图F11所示区域右击鼠标,选择“New Source”选项

F11

选择“Verilog Test Fixture”选项,添加测试文件,在“File Name”栏中为测试文件命名,如“test_Fixture”。

一直点击“Next”,直至点击“Finish”完成设置。

F11

在新建仿真文件后,将文本中Initial Begin 和end 之间的内容修改为如下内容。

完成文本输入后,在F12所示的界面中,首先在左上区域内选中“test_Fixture”,然后双击左下区域内的“Simulate Behavioral Model”进入仿真界面。

仿真界面效果

图如图F13所示。

F12

F13

5.锁定引脚

关闭仿真界面,显示如图F14所示界面,首先将工程切换至“Implementation”状态,然后在左上区域内右击鼠标,为工程添加“Implementation Constraints Files”选项。

F14

在“Files Name”选项中命名引脚文件,如“Test_ICF”。

F15

在引脚锁定文件中,输入引脚映射关系。

效果如图F16所示。

F16

6.综合文件

选择如图F17所示的test.v文件,然后双击“Synthesize - XST”进行综合。

F17

双击“Implement Design”。

F18

7.生成.bit文件并下载

双击“Generate Programming Files”文件,生成.bit文件。

F19

双击“Configuration Target Device”->“Management Configuration Project”进入下载界面。

F20

进入下载界面后,双击“Boundary Scan”,在右侧区域内右击鼠标,在下拉菜单中选择“Initialize Chain”。

F21

(首先,取消所有弹出的对话框)这时将出现如图F22所示的界面,然后然后双击如图F22中所框选的芯片,然后选择已经生成的.bit文件,如图F23所示。

F22

F23在弹出的对话框中,选择“No”

F24

然后,鼠标右键选择图F22中的芯片,选择下拉菜单中的“Program”选项。

在确认弹出的对话框中的芯片信息后,点击“OK”进行下载。

F25

8.生成.mcs文件并下载到PROM中

之前6步如前面所述,然后跳过第7步,双击“Generate Programming Files”文件,生成.bit文件。

双击“Configuration Target Device”,弹出对话框,点击“OK”确定。

F26

进入下载界面后,在弹出图F27对话框中,双击“Create PROM File”,弹出F28对话框。

Step1存储类型选择Xilinx Flash/PROM,点击中间绿色箭头,进入Step2,如图F28选择PROM Family与Device,再点击“Add Storage Device”或者如图F29直接勾选“Auto Select PROM” 进入Step3,填写输出文件名字与位置,生成文件格式为.MCS。

F27

F28

F29

点击“OK”,弹出对话框选择“Yes”,弹出Add Device,提示开始添加设备文件,点击“OK”,添加之前生成的test.bit文件。

F30

之后弹出Add Device,提示是否添加其他文件,点击“NO”,之后点击“OK”确定。

F31

F32

双击“Generate File”,右侧提示“Generate Succeeded”,即生成.MCS文件完毕。

F33

选择“Boundary Scan”,右侧空白右击,在下拉菜单中选择“Initialize Chain”。

F34

(首先,取消所有弹出的对话框)这时将出现如图F35所示的界面,然后双击如图F35中所框选的芯片,然后选择已经生成的.mcs文件,如图F36所示。

F35

F36

然后,鼠标右键选择图F35中的芯片,选择下拉菜单中的“Program”选项。

在确认弹出的对话框中的芯片信息后,点击“OK”进行下载。

F37

等待下载完成后,设备断电后重新上电即可。

附录

BASYS2 开发板引脚分配表。