实验课7 全差分运放的仿真方法

【最新精选】差分放大电路仿真

差分放大电路仿真一、实验目的1.掌握差动放大电路对放大器性能的影响。

2.学习差动放大器静态工作点、电压放大倍数、输入电阻、输出电阻的仿真方法。

3.学习掌握Multisim交流分析4.学会开关元件的使用二、实验原理图3.2-1是差动放大器的基本结构。

它由两个元件参数相同的基本共发射放大电路组成。

当开关K 拨向左边时,构成典型的差动放大器。

调零电位器RP用来调节VT1、VT2管的静态工作点,使得输入信号Ui=0时,双端输出电压Uo=0。

R E为两管共用的发射极电阻,它对差模信号无负反馈作用,因而不影响差模电压放大倍数,但对共模信号有较强的负反馈作用,故可以有效地抑制零漂,稳定静态工作点。

图3.2-1 差动放大器原理电路在设计时,选择VT1、VT2特性完全相同,相应的电阻也完全一致,调节电位器RP的位置置50%处,则当输入电压等于零时,UCQ1= UCQ2,即Uo=0。

双击图中万用表XMM1、XMM2、XMM3分别显示出UCQ1、、UCQ2、Uo电压,其显示结果如图3.2-2所示。

(a)UCQ1显示结果(b)Uo显示结果(c)UCQ2显示结果图3.2-2 UCQ1、、UCQ2、Uo显示结果三、虚礼实验仪器及器材双踪示波器信号发生器交流毫伏表数字万用表四、实验内容与步骤1. 差动放大器的静态工作点分析 典型差动放大器电路静态工作点EBEEE E R U U I -≈(认为UB1=UB2≈0),E C2C1I 21I I ==恒流源差动放大器电路静态工作点E1BEEE CC 212E3C3R U )U (U R R R I I -++≈≈,C3C1C1I 21I I == (1)按下图3.2-3输入电路图3.2-3(2)调节放大器零点把开关S1和S2闭合,S3打在最左端,启动仿真,调节滑动变阻器的阻值,使得万用表的数据为0(尽量接近0,如果不好调节,可以减小滑动变阻器的Increment 值)。

(3)直流分析启动直流分析,将测量结果填入下表:2. 差模电压放大倍数和共模电压放大倍数 (1)测量差模电压放大倍数当差动放大器的发射极电阻R E 足够大,或采用恒流源电路时,差模电压放大倍数Ad 由输出端方式决定,而与输入方式无关。

差分放大电路的分析与仿真

差分放大电路的分析与仿真摘要:差分放大电路是模拟电路学习中常用到的放大电路,其抑制零点飘移的良好电气特性,使它经常被用作多级放大电路的输入级。

本文通过对差分电路的静态及动态分析及仿真,让学生能够对差分放大电路有深入的了解。

关键词:零点漂移;差分放大;仿真分析中图分类号:TP311 文献标识码:A 文章编号:1009-3044(2018)09-0246-011 引言当今世界之所以能称之为智能化的时代,是由于各种智能化的设备得到了普及,而这些智能化设备之所以能够智能化,离不开功能各异的各种传感器,而这些传感器所采集到的电信号一般都很微弱,同时这些微弱的电信号往往不是周期性的,所以对这些信号进行放大处理时,需要采用直接耦合放大电路进行放大,所谓直接耦合即输入信号引入放大电路及放大电路与其负载的连接都是靠导线直接连接,因此直接耦合连接方式有很好的低频特性同时又很容易做成集成电路。

直接耦合放大电路虽然有以上几大优势,但普通的直接耦合放大电路存在零点漂移现象,所谓“零点漂移”,就是当输入信号为零时面输入信号不为零。

差分放大电路是一种直接耦合放大电路,差分电路本身具有良好的电气对称性,使其对模性号有很强的抑制作用,所以能有效地抑制零点漂移现象的发生。

2 差分放大电路抑制温漂的原理分析零点漂移现象的产生,其原因有很多,但最为主要的原因还是晶体管受到外部温度变化所引起的静态工作点的波动,所以零点漂移也常被称为温度漂移,简称温漂。

那差分放大电路是如何做到抑制温漂的呢?图1所示电路为长尾差分放大电路,当两端的输入信号电压uI1=uI2=0时,也就是电路处于完全的直流分量控制静态状态,因为T1与T2管的电气特性完全相同,其外接电阻参数也都相同,那么就有集电极对地电位UCQ1=UCQ2的结果,所以静态时的输出电压UO=0。

如果外界温度升高了,ICQ1和ICQ2也会同时增大,而且其增大幅度完全相同,从而导致两个集电极电阻上的压降出现等值幅度的增大,进而使UCQ1和UCQ2同时等值幅度变小,所以输出UO=UCQ1CUCQ2=0保持不变。

运放的仿真与分析报告

运放的仿真与分析1.基本仿真流程(1)电路仿真界面:进入UNIX系统,按键“Ctrl+t”出现下图窗口:图1输入“icfb&”回车后出现下图窗口。

图2注:有关镜像的操作:图2中选择“Library Path Editor”出现下图窗口:图3左栏为文件名,右栏为路径;或者打开文件cds.lib 按下图编写文件图4图5File→New→Library(opam)→(New)Cell View进入电路图编辑界面,画相应的放大器电路,如下图图6(2)调用相关器件器件的调用操作:按快捷键“i”,选择library,以及相应的器件(nmos,pmos,res,cap等)注:模型名要与模型库中的相应名称相同。

打开模型库的.scs文件,查看模型名和器件的基本参数(,,t V ):ox th// Models included in this release ://// Model Name Description// ----------- ----------------------------------------------------------------------// nmos_1p8 BSIM3v3 model for thin-gate (1.8V) NMOS transistor// pmos_1p8 BSIM3v3 model for thin-gate (1.8V) PMOS transistor// nmos_3p3 BSIM3v3 model for thick-gate (3.3V) NMOS transistor// pmos_3p3 BSIM3v3 model for thick-gate (3.3V) PMOS transistor// nmos_1p8_nat BSIM3v3 model for thin-gate (1.8V) Native NMOS transistor// nmos_3p3_nat BSIM3v3 model for thick-gate (3.3V) Native NMOS transistorsection nmos_1p8_tmodel nmos_1p8 bsim3v3 {0: type=n+ lmin=1.8e-007 lmax=3.5e-007 wmin=2.2e-007………………………………………………………….+ xw=0 tox=3.5e-009 toxm=3.5e-009…………………………………………………+ xpart=0 vth0=0.39851301 lvth0=1.1573677e-008…………………………………………………..+ cdscd=0 cit=0.0017786 u0=0.035597185………………………………….//***************************************************************************** section pmos_1p8_tmodel pmos_1p8 bsim3v3 { 0: type=p+ lmin=1.8e-007 lmax=3.5e-007 wmin=2.2e-007………………………………………………….+ xl=0 xw=0 tox=3.5554e-009…………………………………………….+ cgdo=3.051e-010 xpart=0 vth0=-0.39889023…………………………………………..+ u0=0.0078211697 lu0=1.2538533e-010 wu0=5.1065658e-010…………..…………………………….注:在sim.scs 文件中没有表示沟道调制效应的参数λ,因而需要测量计算: 修正后的漏电流为 2()(1)D n GS T DS i K v V v λ=-+图7如图可求出λ。

差分放大电路仿真分析

差分放大电路仿真分析差分放大电路是集成运算放大器的主要单元电路之一,它具有很强的抑制零点漂移的能力。

作为集成运算放大器的输入级,差分放大电路几乎完全决定着集成运算放大器的差模输入特性、共模抑制特性、输入失调特性和噪声特性。

差分放大电路经由两个参数完全相同的晶体管组成,电路结构对称。

电路具有两个输入端和两个输出端,因此差分放大电路具有四种形式:单端输入单端输出、单端输入双端输出、双端输入单端输出以及双端输入双端输出。

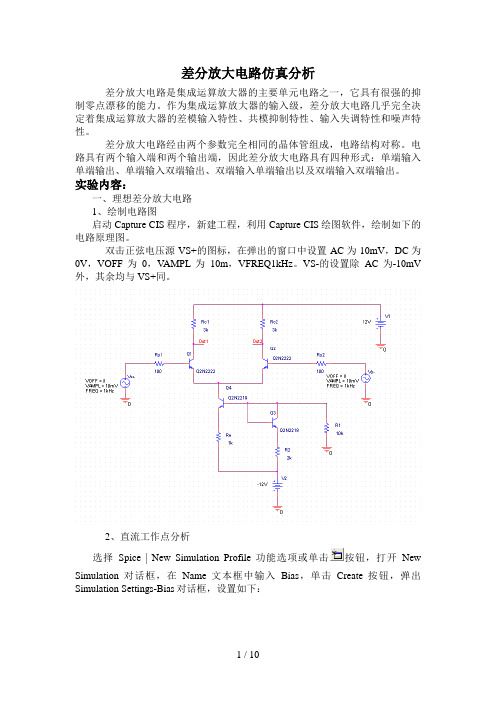

实验内容:一、理想差分放大电路1、绘制电路图启动Capture CIS程序,新建工程,利用Capture CIS绘图软件,绘制如下的电路原理图。

双击正弦电压源VS+的图标,在弹出的窗口中设置AC为10mV,DC为0V,VOFF为0,V AMPL为10m,VFREQ1kHz。

VS-的设置除AC为-10mV 外,其余均与VS+同。

2、直流工作点分析选择Spice | New Simulation Profile功能选项或单击按钮,打开New Simulation对话框,在Name文本框中输入Bias,单击Create按钮,弹出Simulation Settings-Bias对话框,设置如下:保存设置,启动PSpice A/D仿真程序,调出PSpice A/D窗口,可以在PSpice A/D窗口中选择View | OutPut Filse功能菜单选项,查看输出文件。

在Capture CIS窗口中,单击I 、V按钮,此时电路图中显示电路的静态工作电压与电流值,如下图:3、双端输入是的基本特性上面的电路是双端输入的形式,可以利用上面的电路来分析双端输入时的电路特性。

将分析类型设为交流扫描分析AC Sweep。

选择PSpice | New SimulationProfile功能选项或单击按钮,打开New Simulation对话框,在Name文本框中输入AC,单击Create按钮,弹出Simulation Settings-AC对话框,设置如下:启动PSpice A/D仿真程序,显示空的PSpice A/D窗口,选择Trace | Add Trace命令,在Add Trace窗口中设置如下图,即观察单端输出时的电压增益:V(OUT1)/ (V(VS+:+)-V(Vs-:+))。

差分放大电路仿真实验

图 8 修改信号线的颜色

五、实验记录

序号 1 2 3 4 5 RG(Ω )

VIN+

VIN-

VRef

计算的 Vo

示波器测得的 Vo

4

差分放大电路仿真实验

一、实验目的: 了解传感器输出一般微弱信号差分放大方法。 二、实验原理: 传感器将被测非电量转换为电信号,一般情况传感器输出的信号是微弱信 号,表现为幅值较小(一般是 mV 量级,甚至更小) ,需要放大。 应变片构建惠斯通电桥输出差分信号(图 1(a) ) ,热电偶传感器输出差分 信号(图 1(b) ) ,等等。

图 7 仪表放大器 AD623 管脚连接示意图 3

4.电路接入示波器, 用以观察信号发生器输出的微弱信号 A 和经过调理电路 后的输出信号 B,验证仪表放大器 Vo (1+

100KΩ ) ( VIN + -VIN -) VRef 正确性。 RG

双击导线,弹出对话框可以修改信号线颜色,如图 8 所。

图 2 仪表放大器电路图

Vo (1+

100KΩ ) ( VIN + -VIN -) VRef RG

(式 1)

三、实验所需条件: 利用 Multisim10 软件进行仿真实验。计算机上安装 Multisim10 软件。 信号发生器、仪表放大器 AD623、二阶压控低通滤波器、示波器

1

四、实验步骤: 1. 函数发生器输出信号认为是 VIN+, 设置频率 100~500Hz, 峰值 1~10mv, “+ ” 端接入 AD623 的 VIN+,中间端点接地,信号可以选择正弦波、三角波、方波。函 数发生器如图 4 所示。也可以选择使用 Agilent 函数发生器,如图 5 所示。

全差分运放实验

两级CMOS全差分运算放大器的设计和仿真 (2)1、软件的安装 (2)1.1 Cadence orcad的安装 (2)1.2 Hspice的安装 (2)1.3Cosmos Scope的安装 (2)2、实验要求 (2)3、电路图手工计算 (3)3.1 运放主结构计算 (3)3.2 偏置电路 (5)3.3 共模反馈电路 (7)4、使用Orcad绘制电路图 (7)5、电路仿真 (11)6、仿真结果查看 (13)7、其他性能参数的仿真 (15)两级CMOS全差分运算放大器的设计和仿真1、软件的安装在该试验中要用到三个软件,分别为Cadence orcad(绘制电路图与网表提取工具),Hspice (电路仿真工具)和Cosmos Scope(仿真结果查看工具)。

所有用到的软件安装程序均放在D盘EDA文件夹中。

1.1 Cadence orcad的安装打开D盘中的\eda\OrCad9.23,点击Setup.exe,点击下一步,到输入Install Code步骤,打开Crack文件夹中的Install.tex文件,将Orcad Capture后面的码复制到Install Code里,然后点击下一步。

直至安装完毕。

1.2 Hspice的安装打开D盘eda\hspice_vA-2008.03,点击Hspice的安装程序进行安装,均点击下一步,直至安装结束。

然后将该文件夹中的hspice2008.lic文件拷贝到C:\synopsys\Hspice_A-2008.03下。

右键点击电脑桌面我的电脑/属性/高级/环境变量/系统变量(如果只想让管理员用,则是administrator的用户变量)/新建/变量名lm_license_file 变量值就是license文件的路径,/hspice2008.lic,也就是变量值为C:\synopsys\Hspice_A-2008.03\hspice2008.lic 然后确定。

1.3Cosmos Scope的安装打开D盘eda\cosmos2007\HSpice_CosmosScope_Z-2007.03-SP1_win,点击安装程序进行安装。

差分运放电流串联负反馈的理论计算与仿真分析

差分一运放电流串联负反馈的理论计算与仿真分析摘要构建了直接耦合方式下的差分一运放电流串联负反馈放大电路,根据多级放大器增益的计算方法,计算了基本放大器的电压增益,进而得互导增益。

另外采用微变等效电路方法,求解电路方程得到了反馈放大器的互导增益,两者满足负反馈放大电路中的基本关系。

同时,启用仿真软件EWB,基本放大器和反馈放大器的仿真结果与理论计算一致。

关键词负反馈;差分一运放放大电路;EWB1 引言伴随计算仿真技术迅速发展,可将实际电子元器件采用理想模型替代,这极大方便了电路分析和设计。

采用方框图分析法,可以解决不满足深度负反馈条件下的负反馈放大电路,但有些文献在讨论时疏忽了反馈网络的负载效应,易造成误解。

近年来经常出现一些使用仿真软件对负反馈放大器讨论,收到很好效果的报道,引起了人们普遍关注。

本文设计了直接耦合差分一运放电流串联负反馈放大电路,理论计算下的基本放大器的互导增益与微变等效电路计算下的反馈放大器的互导增益满足反馈放大器中的基本关系式,与EWB5.0开、闭环环境下的仿真结果一致。

2理论计算与仿真 2.1电路由差分电路和运算放大电路组合而成的直接耦合多级放大电路如图1所示,键S 位于N 处,构成电流串联负反馈放大器。

位于M 处,是考虑反馈网络负载效应后的基本放大器。

2.2理论计算 (1)基本放大器互导增益对于基本放大器,将单端输入差分放大器输入 端对地短路,考虑到差分电路的对称性,略去1b R(令12bb b RRR ==)电阻压降,可得1T、2T两管静态电流1E I、2E I1210.712·0.471212E E V Vm A k II-+===Ω根据软件中所设置100β=,有'1'21(1)/5.575b e b e E Tk V r rIβ==+=Ω,其远大于一般为几十欧的[5]'b b r,略去'b br 有'beb err≈。

运放仿真方法整理

运放仿真方法整理运算放大器的仿真包括直流工作点仿真(OP)、直流扫描仿真(DC)、交流小信号仿真(AC)、瞬态仿真(TRAN)等等。

DC仿真又包括共模输入和输出范围、输入失调电压仿真;AC仿真包括开环增益、带宽、相位裕度、共模抑制比、电源抑制比等等;TRAN仿真包括大、小信号摆率、过冲、建立时间等等。

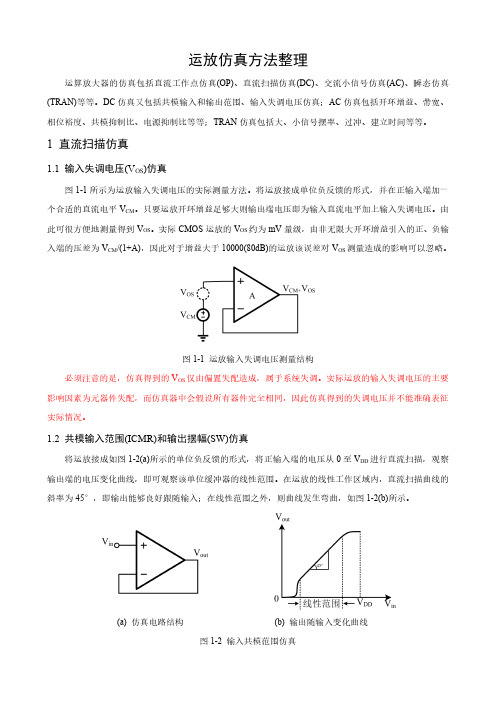

1直流扫描仿真1.1输入失调电压(V OS)仿真图1-1所示为运放输入失调电压的实际测量方法。

将运放接成单位负反馈的形式,并在正输入端加一个合适的直流电平V CM。

只要运放开环增益足够大则输出端电压即为输入直流电平加上输入失调电压。

由此可很方便地测量得到V OS。

实际CMOS运放的V OS约为mV量级,由非无限大开环增益引入的正、负输入端的压差为V CM/(1+A),因此对于增益大于10000(80dB)的运放该误差对V OS测量造成的影响可以忽略。

图1-1运放输入失调电压测量结构必须注意的是,仿真得到的V OS仅由偏置失配造成,属于系统失调。

实际运放的输入失调电压的主要影响因素为元器件失配,而仿真器中会假设所有器件完全相同,因此仿真得到的失调电压并不能准确表征实际情况。

1.2共模输入范围(ICMR)和输出摆幅(SW)仿真将运放接成如图1-2(a)所示的单位负反馈的形式,将正输入端的电压从0至V DD进行直流扫描,观察输出端的电压变化曲线,即可观察该单位缓冲器的线性范围。

在运放的线性工作区域内,直流扫描曲线的斜率为45°,即输出能够良好跟随输入;在线性范围之外,则曲线发生弯曲,如图1-2(b)所示。

(a)仿真电路结构(b)输出随输入变化曲线图1-2输入共模范围仿真用该结构仿真得到的线性范围同时受到输入共模范围和输出摆幅的限制,因此无法用该结构精确测得ICMR。

对于一般的运放,输出摆幅范围通常大于输入共模范围,故该方法能够大致预估输入共模范围。

图1-3(a)所示的反相电压放大器增益为-10。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

CMOS模拟集成电路实验报告实验课7 全差分运放的仿真方法目标:1、了解全差分运放的各项指标2、掌握全差分运放各项指标的仿真方法,对全差分运放的各指标进行仿真,给出各指标的仿真结果。

本次实验课使用的全差分运放首先分析此电路图,全差分运算放大器是一种具有差分输入,差分输出结构的运算放大器。

其相对于单端输出的放大器具有一些优势:因为当前的工艺尺寸在减少,所以供电的电源电压越来越小,所以在供电电压很小的情况下,单端输出很难理想工作,为了电路有很大的信号摆幅,采用类似上图的全差分运算放大器,其主要由主放大器和共模反馈环路组成。

1、开环增益的仿真得到的仿真图为1.开环增益:首先开环增益计算方法是低频工作时(<200Hz) ,运放开环放大倍数;通过仿真图截点可知增益为73.3db。

2.增益带宽积:随着频率的增大,A0会开始下降,A0下降至0dB 时的频率即为GBW,所以截取其对应增益为0的点即可得到其增益带宽积为1.03GB。

3.相位裕度:其计算方法为增益为0的时候对应的VP的纵坐标,如图即为-118,则其相位裕度为-118+180=62,而为保证运放工作的稳定性,当增益下降到0dB 时,相位的移动应小于180 度,一般取余量应大于60度,即相位的移动应小于120 度;所以得到的符合要求。

在做以上仿真的时候,关键步骤在于设定VCMFB,为了得到大的增益,并且使相位裕度符合要求,一直在不停地改变VCMFB,最初只是0.93,0.94,0.95的变化,后来发现增益还是远远不能满足要求,只有精确到小数点后4为到5位才能得到大增益。

2.CMRR 的仿真分析此题可得共模抑制比定义为差分增益和共模增益的比值,它反映了一个放大器对于共模信号和共模噪声的抑制能力。

因此需要仿真共模增益和差分增益。

可以利用两个放大器,一个连成共模放大,一个连成差模放大,用图1仿真差分增益图1用图2仿真共模增益图2将两个仿真写在一个sp文件中可以得到如下结果:相角仿真因为CMRR 的相角为=Vp(V op,Von)-Vp(V o p)黄色的为Vp(Vo p),红色的为Vp(V op,Von),两者相减,得到CMRR 的相角的仿真图为,其中蓝线为CMRR的相角仿真图,其它两条为上面的线,将它们放在一起对比:CMRR的幅度仿真其CMRR 的幅值为=Vdb(V op,V on)-Vdb(V op),蓝线为Vdb(V op,V on),粉线为Vdb(V op),两者相减得到绿线,即为CMRR的幅值特性曲线截取其在100HZ之前的增益值可得低频时增益为49.1db。

3.PSRR 的仿真分析可得,共模抑制比定义为放大器的差分增益和电源到输出的增益的比值,它放映了放大器对电源和地噪声的抑制能力。

此时,同样使用两个放大器电路,一个仿真电源到输出的增益,一个测试放大器的差分增益。

电路的信号激励和CMRR中设置的一样,所不同的是在仿真共模信号的图中的直流信号实质上就是VDD,交流信号最为输入小信号加在输入端,即为如下图:按照上述步骤进行仿真可得幅度仿真图为PSRR的幅值=Vdb(V op,V on)-Vdb(V op),其中蓝线为Vdb(V op,Von),粉线为Vdb(Vop),两者相减即可得PSRR的幅值的曲线,即为绿线。

则由上面的仿真图截点可得其PSRR的幅值低频增益为43.6。

可得相角仿真图为PSRR的相角为=Vp(V op,V on)-Vp(V op),其中最上面的线为Vp(Vop),中间紫色的线为Vp(V op,Von),最下面的黄线即为PSRR的相角的变化曲线4. 输出阻抗的分析得到仿真图为首先,输出阻抗是指运放闭环应用时的输出阻抗,如果把闭环系统作为一个电压源来看,则输出阻抗即为该电压源的源电阻。

由图像可得点,将此点转为电压并与设定的电流相除即可得到电阻,由此得到输出阻抗为794K。

5转换速率仿真首先,转换速率表示大信号工作时运放性能的一个重要参数,是运放输出电压对时间的变化率。

然后观察图像,其中红色的线为V(outm),黄色的为V(outp),则通过截点可计算V (outp)SR为0.109 V/N S , V(outm)SR为0.063 V/N S。

源代码:------------------------------------------------------------------------------ .TITLE7-1.MODEL NMOS NMOS (+LEVEL=1 VT0=0.7 GAMMA=0.45 PHI=0.9+NSUB=9e+14 LD=0.08e-6 U0=350 LAMBDA=0.1+TOX=9e-9 PB=0.9 CJ=0.56e-3 CJSW=0.35e-11+MJ=0.45 MJSW=0.2 CGDO=0.4e-9 JS=1.0e-8)**************model PMOS************************.MODEL PMOS PMOS (+LEVEL=1 VT0=-0.8 GAMMA=0.4 PHI=0.8+NSUB=5e+14 LD=0.09e-6 U0=100 LAMBDA=0.2+TOX=9e-9 PB=0.9 CJ=0.94e-3 CJSW=0.32e-11+MJ=0.5 MJSW=0.3 CGDO=0.3e-9 JS=0.5e-8)************************************************M1 4 7 8 8 PMOS W=180U L=500NM2 10 9 4 8 PMOS W=195U L=500NM3 10 12 13 0 NMOS W=55U L=500NM4 13 15 0 0 NMOS W=50U L=500NM5 11 9 6 8 PMOS W=195U L=500NM6 6 5 2 0 NMOS W=224U L=500NM7 4 3 2 0 NMOS W=224U L=500NM8 11 12 14 0 NMOS W=56U L=500NM9 14 15 0 0 NMOS W=50U L=500NM10 2 1 0 0 NMOS W=50U L=500NM11 18 18 0 0 NMOS W=5U L=500NM12 7 7 8 8 PMOS W=15U L=500NM13 16 7 8 8 PMOS W=8U L=500NM14 9 9 8 8 PMOS W=1.9U L=500NM15 16 16 12 0 NMOS W=5U L=500NM16 6 7 8 8 PMOS W=180U L=500NM17 9 15 0 0 NMOS W=5U L=500NM18 15 12 17 0 NMOS W=5.6U L=500NM19 17 15 0 0 NMOS W=5U L=500NM20 12 16 15 0 NMOS W=1.2U L=500NM21 19 18 0 0 NMOS W=5U L=500NM22 20 20 18 0 NMOS W=5U L=500NM23 7 20 19 0 NMOS W=5U L=500N************************************************ VDD 8 0 3.3IDC 8 20 60UVCMFB 1 0 0.93581V1 21 22 AC 1E0 5 30 VCVS 21 22 0.5E1 3 30 VCVS 21 22 -0.5************************************************ VDC 30 0 2.2C1 10 0 1PCO 11 0 1P.AC DEC 100 1k 10G.OPTION ACOUT=0.OPTIONS POST ACCT PROBE.PROBE VDB(10 11) VP (10 11).END.TITLE2.MODEL NMOS NMOS (+LEVEL=1 VT0=0.7 GAMMA=0.45 PHI=0.9+NSUB=9e+14 LD=0.08e-6 U0=350 LAMBDA=0.1+TOX=9e-9 PB=0.9 CJ=0.56e-3 CJSW=0.35e-11 +MJ=0.45 MJSW=0.2 CGDO=0.4e-9 JS=1.0e-8)**************model PMOS************************ .MODEL PMOS PMOS (+LEVEL=1 VT0=-0.8 GAMMA=0.4 PHI=0.8+NSUB=5e+14 LD=0.09e-6 U0=100 LAMBDA=0.2+TOX=9e-9 PB=0.9 CJ=0.94e-3 CJSW=0.32e-11 +MJ=0.5 MJSW=0.3 CGDO=0.3e-9 JS=0.5e-8)************************************************ M1 4 7 8 8 PMOS W=180U L=500NM2 10 9 4 8 PMOS W=195U L=500NM3 10 12 13 0 NMOS W=55U L=500NM4 13 15 0 0 NMOS W=50U L=500NM5 11 9 6 8 PMOS W=195U L=500NM6 6 5 2 0 NMOS W=224U L=500NM7 4 3 2 0 NMOS W=224U L=500NM8 11 12 14 0 NMOS W=56U L=500NM9 14 15 0 0 NMOS W=50U L=500NM10 2 1 0 0 NMOS W=50U L=500NM11 18 18 0 0 NMOS W=5U L=500NM12 7 7 8 8 PMOS W=15U L=500NM13 16 7 8 8 PMOS W=8U L=500NM14 9 9 8 8 PMOS W=1.9U L=500NM15 16 16 12 0 NMOS W=5U L=500NM16 6 7 8 8 PMOS W=180U L=500NM17 9 15 0 0 NMOS W=5U L=500NM18 15 12 17 0 NMOS W=5.6U L=500NM19 17 15 0 0 NMOS W=5U L=500NM20 12 16 15 0 NMOS W=1.2U L=500NM21 19 18 0 0 NMOS W=5U L=500NM22 20 20 18 0 NMOS W=5U L=500NM23 7 20 19 0 NMOS W=5U L=500N************************************************ VDD 8 0 3.3IDC 8 20 60UVCMFB 1 0 0.93581V1 3 30 AC 1VDC 30 0 2.2C1 10 0 1PSCO 11 0 1P.AC DEC 100 1K 10G.OPTION ACOUT=0.OPTIONS POST ACCT PROBE.PROBE VDB(10 ) VP (11).END.TITLE3.MODEL NMOS NMOS (+LEVEL=1 VT0=0.7 GAMMA=0.45 PHI=0.9+NSUB=9e+14 LD=0.08e-6 U0=350 LAMBDA=0.1+TOX=9e-9 PB=0.9 CJ=0.56e-3 CJSW=0.35e-11 +MJ=0.45 MJSW=0.2 CGDO=0.4e-9 JS=1.0e-8)**************model PMOS************************ .MODEL PMOS PMOS (+LEVEL=1 VT0=-0.8 GAMMA=0.4 PHI=0.8+NSUB=5e+14 LD=0.09e-6 U0=100 LAMBDA=0.2+TOX=9e-9 PB=0.9 CJ=0.94e-3 CJSW=0.32e-11 +MJ=0.5 MJSW=0.3 CGDO=0.3e-9 JS=0.5e-8)************************************************ M1 4 7 8 8 PMOS W=180U L=500NM2 10 9 4 8 PMOS W=195U L=500NM3 10 12 13 0 NMOS W=55U L=500NM4 13 15 0 0 NMOS W=50U L=500NM5 11 9 6 8 PMOS W=195U L=500NM6 6 5 2 0 NMOS W=224U L=500NM7 4 3 2 0 NMOS W=224U L=500NM8 11 12 14 0 NMOS W=56U L=500NM9 14 15 0 0 NMOS W=50U L=500NM10 2 1 0 0 NMOS W=50U L=500NM11 18 18 0 0 NMOS W=5U L=500NM12 7 7 8 8 PMOS W=15U L=500NM13 16 7 8 8 PMOS W=8U L=500NM14 9 9 8 8 PMOS W=1.9U L=500NM15 16 16 12 0 NMOS W=5U L=500NM16 6 7 8 8 PMOS W=180U L=500NM17 9 15 0 0 NMOS W=5U L=500NM18 15 12 17 0 NMOS W=5.6U L=500NM19 17 15 0 0 NMOS W=5U L=500NM20 12 16 15 0 NMOS W=1.2U L=500NM21 19 18 0 0 NMOS W=5U L=500NM22 20 20 18 0 NMOS W=5U L=500NM23 7 20 19 0 NMOS W=5U L=500N************************************************ VDD 8 0 3.3IDC 8 20 60UVCMFB 1 0 0.93581V1 31 32 AC 1E0 5 30 VCVS 31 32 0.5E1 3 30 VCVS 31 32 -0.5VDC 30 0 2.2C1 10 0 1PCO 11 0 1P.AC DEC 100 1k 10G.OPTION ACOUT=0.OPTIONS POST ACCT PROBE.PROBE VDB(10 11) VP (10 11) .END。