飞思卡尔s12单片机—PIT和时钟产生器模块

飞思卡尔MC9S12XS128单片机各模块使用方法及寄存器配置

飞思卡尔MC9S12XS128单片机各模块使用方法及寄存器配置手把手教你写S12XS128程序--PWM模块介绍该教程以MC9S12XS128单片机为核心进行讲解,全面阐释该16位单片机资源。

本文为第一讲,开始介绍该MCU的PWM模块。

PWM 调制波有8个输出通道,每一个输出通道都可以独立的进行输出。

每一个输出通道都有一个精确的计数器(计算脉冲的个数),一个周期控制寄存器和两个可供选择的时钟源。

每一个P WM 输出通道都能调制出占空比从0—100% 变化的波形。

PWM 的主要特点有:1、它有8个独立的输出通道,并且通过编程可控制其输出波形的周期。

2、每一个输出通道都有一个精确的计数器。

3、每一个通道的P WM 输出使能都可以由编程来控制。

4、PWM 输出波形的翻转控制可以通过编程来实现。

5、周期和脉宽可以被双缓冲。

当通道关闭或PWM 计数器为0时,改变周期和脉宽才起作用。

6、8 字节或16 字节的通道协议。

7、有4个时钟源可供选择(A、SA、B、SB),他们提供了一个宽范围的时钟频率。

8、通过编程可以实现希望的时钟周期。

9、具有遇到紧急情况关闭程序的功能。

10、每一个通道都可以通过编程实现左对齐输出还是居中对齐输出。

1、PWM启动寄存器PWMEPWME 寄存器每一位如图1所示:复位默认值:0000 0000B图1 PWME 寄存器每一个PWM 的输出通道都有一个使能位P WMEx 。

它相当于一个开关,用来启动和关闭相应通道的PWM 波形输出。

当任意的P WMEx 位置1,则相关的P WM 输出通道就立刻可用。

用法:PWME7=1 --- 通道7 可对外输出波形PWME7=0 --- 通道7 不能对外输出波形注意:在通道使能后所输出的第一个波形可能是不规则的。

当输出通道工作在串联模式时(PWMCTL 寄存器中的CONxx置1),那么)使能相应的16位PWM 输出通道是由PWMEx 的高位控制的,例如:设置PWMCTL_CON01 = 1,通道0、1级联,形成一个16位PWM 通道,由通道 1 的使能位控制PWM 的输出。

MC9S12XS128 PIT模块

言归正传,开始讲PIT,讲PIT,我准备先简单讲讲寄存器,之前不讲主要是基本上买的到的书都是DG128的,里面关于IO口的寄存器和PWM的寄存器都是完全可以照搬的,而这一章的东西照搬是要出问题的。

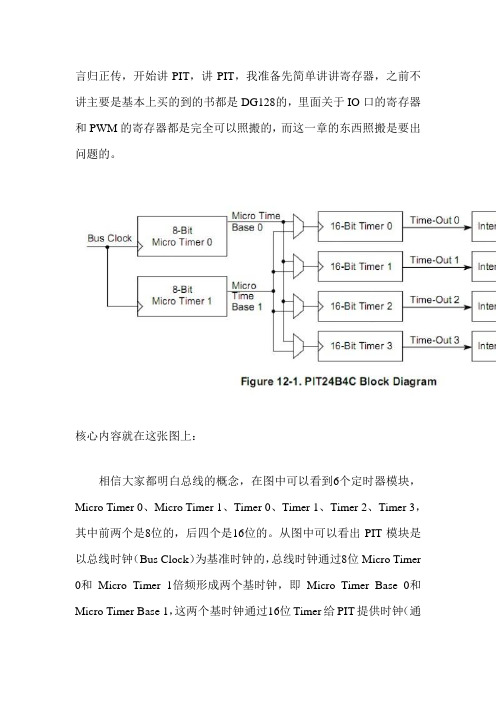

核心内容就在这张图上:相信大家都明白总线的概念,在图中可以看到6个定时器模块,Micro Timer 0、Micro Timer 1、Timer 0、Timer 1、Timer 2、Timer 3,其中前两个是8位的,后四个是16位的。

从图中可以看出PIT模块是以总线时钟(Bus Clock)为基准时钟的,总线时钟通过8位Micro Timer 0和Micro Timer 1倍频形成两个基时钟,即Micro Timer Base 0和Micro Timer Base 1,这两个基时钟通过16位Timer给PIT提供时钟(通过寄存器PITMUX设置)。

原理讲完了,其实相对于PIT模块是一个24位的定时器(51单片机最多也就16位),这个计数范围还是蛮大的。

下面是一些寄存器的解释,解释完还是看代码吧。

S12PIT24B4CV1是一个模数递减计数器。

首先给计数寄存器设定一个初值,每经过一个总线周期,计数器进行一次减一操作,当计数器自减溢出时,触发中断。

因为总线周期是已知的,即可以通过计数器自减实现定时。

在XS128PIT模块中,需要用到得是如下几个寄存器。

1)、PIT Contorl and force Lad Micro Timer Register(PITCFLMT)该寄存器用于PIT模块的使能设置和工作方式设置。

通常设置该寄存器中的PITE为即可,即PITCFLMT_PITE=1,使PIT使能。

2)、PIT Channel Enable Register(PITCE)该寄存器用于对PIT模块中的4个通道使能进行设置。

如果使用某个通道时,对对应位进行置一即可,即PITCE_PCEx=1,其中x代表通道序号,为0~3。

飞思卡尔单片机S12使用方法及程序

飞思卡尔单片机S12使用方法及程序单片机简介:9S12XS128MAA单片机是16位的单片机80个引脚,CPU是CPU12X,内部RAM 8KB,EEPROM:2KB,FLASH:128KB,外部晶振16M,通过内部PLL可得40M总线时钟。

9S12XS128MAA单片机拥有:CAN:1个,SCI:2个,SPI:1个,TIM:8个,PIT:4个,A/D:8个,PWM:8个下面介绍下我们项目用到的几个模块给出初始化代码1、时钟模块初始化单片机利用外部16M晶振,通过锁相环电路产生40M的总线时钟(9S12XS128系列标准为40M),初始化代码如下:view plaincopy to clipboardprint?/******************系统时钟初始化****************/void Init_System_Clock(){asm { // 这里采用汇编代码来产生40M的总线LDAB #3STAB REFDVLDAB #4STAB SYNRBRCLR CRGFLG,#$08,*//本句话含义为等待频率稳定然后执行下一条汇编语句,选择此频率作为总线频率BSET CLKSEL,#$80}}/******************系统时钟初始化****************/void Init_System_Clock(){asm { // 这里采用汇编代码来产生40M的总线LDAB #3STAB REFDVLDAB #4STAB SYNRBRCLR CRGFLG,#$08,*//本句话含义为等待频率稳定然后执行下一条汇编语句,选择此频率作为总线频率BSET CLKSEL,#$80}上面的代码是汇编写的,这个因为汇编代码量比较少,所以用它写了,具体含义注释已经给出,主函数中调用此函数即可完成时钟初始化,总线时钟为40M.2、SCI模块初始化单片机电路做好了当然少不了和PC之间的通信,通信通过单片机串口SCI链接到PC 端的COM口上去。

飞思卡尔S12系列单片机系统硬件设计

飞思卡尔S12系列单片机 系统硬件设计By DEMONEmail:Wangpanbao@智能车制作网站出版目录第一节 MC9S12DG128B功能概述 >>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>第1页第二节时钟电路设计 >>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>第4页第三节S12单片机系统滤波电路设计 >>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>第6页第四节单片机电源电路设计 >>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>第8页第五节S12系列单片机IO接口电路设计 >>>>>>>>>>>>>>>>>>>>>>>>>>>>>第11页第六节单片机复位电路的设计 >>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>第14页第七节BDM接口电路设计 >>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>第16页第八节RS232串行通讯电路设计 >>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>第17页第九节S12单片机的运行模式 >>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>第21页第十节使用DXP设计单片机系统 >>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>第22页第一节 MC9S12DG128B功能概述MC9S12DG128B是飞思卡尔半导体公司的汽车电子类产品,早在飞思卡尔还没有从摩托罗拉分离出来前就已经诞生了。

飞思卡尔MC9S12XS128功能模块驱动

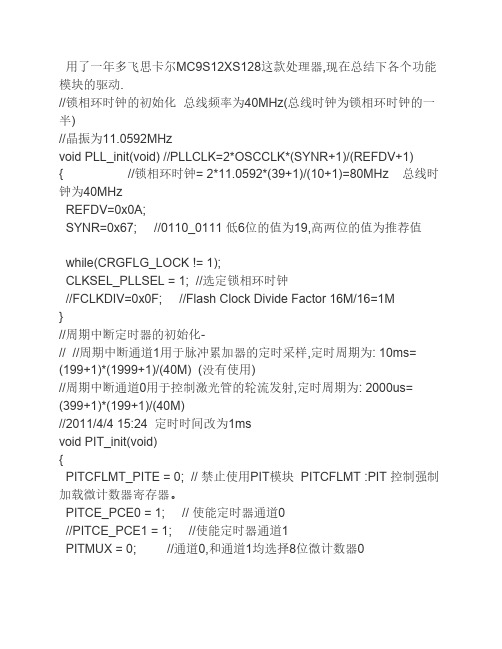

用了一年多飞思卡尔MC9S12XS128这款处理器,现在总结下各个功能模块的驱动.//锁相环时钟的初始化总线频率为40MHz(总线时钟为锁相环时钟的一半)//晶振为11.0592MHzvoid PLL_init(void) //PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1) { //锁相环时钟= 2*11.0592*(39+1)/(10+1)=80MHz 总线时钟为40MHzREFDV=0x0A;SYNR=0x67; //0110_0111 低6位的值为19,高两位的值为推荐值while(CRGFLG_LOCK != 1);CLKSEL_PLLSEL = 1; //选定锁相环时钟//FCLKDIV=0x0F; //Flash Clock Divide Factor 16M/16=1M}//周期中断定时器的初始化-// //周期中断通道1用于脉冲累加器的定时采样,定时周期为: 10ms= (199+1)*(1999+1)/(40M) (没有使用)//周期中断通道0用于控制激光管的轮流发射,定时周期为: 2000us= (399+1)*(199+1)/(40M)//2011/4/4 15:24 定时时间改为1msvoid PIT_init(void){PITCFLMT_PITE = 0; // 禁止使用PIT模块 PITCFLMT :PIT 控制强制加载微计数器寄存器。

PITCE_PCE0 = 1; // 使能定时器通道0//PITCE_PCE1 = 1; //使能定时器通道1PITMUX = 0; //通道0,和通道1均选择8位微计数器0//修改时间只需要改下面四行PITMTLD0 = 199; //向8位微计数器中加载的值PITLD0 = 199; //向16位计数器中加载的值//PITMTLD1 = 39; //向8位微计数器中加载的值 8位,最大值不要超过255//PITLD1 = 1999; //向16位计数器中加载的值PITINTE |= 0x01; //使能定时器通道0的中断PITCFLMT_PITE = 1;//使能PIT模块}//脉冲累加器的初始化, PT7口外接光电编码器//最新修改: 2011/3/25 16:53void PT7_PulAcc_Init(void){DDRT &= 0x77;//设置PT7,PT3口为输入(硬件上PT7,PT3通过跳线联到了一块)PERT |= 0x80; //使能通道7的上拉电阻PPST &= 0x7f; //电阻设为上拉电阻TCTL4 &= 0x3f; //禁止PT3的输入捕捉功能PACTL = 0x50; //启动脉冲累加计数器,上升沿触发,禁止触发中断和溢出中断,主定时器禁止}//通道1用于控制舵机1 PWM 高电平有效,//通道3用于控制电机1 PWM 低电平有效,这与前两代车高电平有效有区别!!!!!//通道7用于给上排激光管提供PWM信号 PWM高电平有效!!!!!//通道6用于给下排激光管提供PWM信号 PWM高电平有效!!!!!// 2011-03-17 7:56 增加了A端口的使用新增通道6//2011-6-9 23:03 //增加了通道4,5的联合使用,用于控制下排方向舵机 void PWM_init(void){PWME = 0x00;//PWM禁止PWMPRCLK = 0x03; // ClockA=40M/8=5M, Clock B = 40M/1=40M PWMSCLB = 10; // Clock SB= 40/2*10= 2MHz(供电机)PWMSCLA = 5; // SA = Clock A/2*5 = 5M/10 = 500K = SA 用于控制舵机PWMPOL = 0xe2; //1110_0010通道7,通道6与通道1、通道5先输出高电平然后输出低电平,POLx=1先输出高电平后输出低电平; PPOLx=0先输出低电平)PWMCAE = 0x00; // 左对齐输出(CAEx=0为左对齐,反之为中心对齐)//PWMCLK = 0010_1010 (0 1 4 5位控制SA_1;或A_0; 2 3 6 7位控制SB_1 或B_0)//为PWM通道1选择时钟 SA(500KHz),//为PWM通道5选择时钟 SA(500KHz),//为通道3选择时钟 SB(10MHz)//为通道7选择时钟B(40MHz)//为通道6选择时钟B(40MHz)PWMCLK = 0x2A; //0010_1010PWMCTL = 0x70; //0111_0000 CON45=1,把通道4,5联合使用。

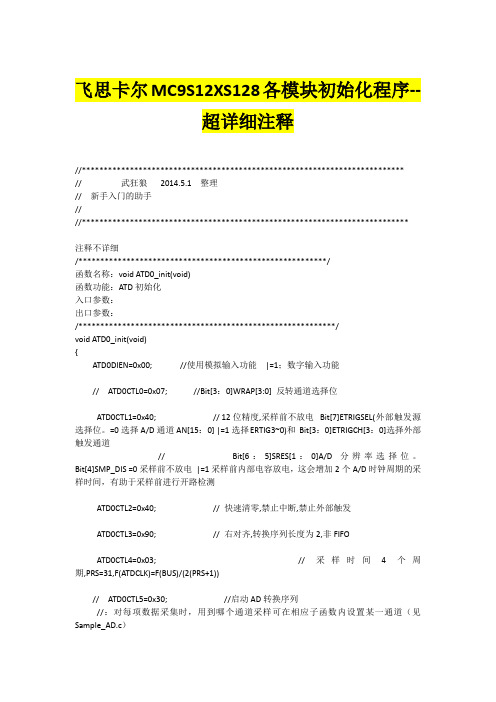

飞思卡尔MC9S12XS128各模块初始化程序--超详细注释

飞思卡尔MC9S12XS128各模块初始化程序--超详细注释//**************************************************************************// 武狂狼2014.5.1 整理// 新手入门的助手////***************************************************************************注释不详细/*********************************************************/函数名称:void ATD0_init(void)函数功能:ATD初始化入口参数:出口参数:/***********************************************************/void ATD0_init(void){ATD0DIEN=0x00; //使用模拟输入功能|=1;数字输入功能// ATD0CTL0=0x07; //Bit[3:0]WRAP[3:0] 反转通道选择位ATD0CTL1=0x40; // 12位精度,采样前不放电 Bit[7]ETRIGSEL(外部触发源选择位。

=0选择A/D通道AN[15:0] |=1选择 ERTIG3~0)和Bit[3:0]ETRIGCH[3:0]选择外部触发通道// Bit[6:5]SRES[1:0]A/D分辨率选择位。

Bit[4]SMP_DIS =0采样前不放电|=1采样前内部电容放电,这会增加2个A/D时钟周期的采样时间,有助于采样前进行开路检测ATD0CTL2=0x40; // 快速清零,禁止中断,禁止外部触发ATD0CTL3=0x90; // 右对齐,转换序列长度为2,非FIFOATD0CTL4=0x03; // 采样时间4个周期,PRS=31,F(ATDCLK)=F(BUS)/(2(PRS+1))// ATD0CTL5=0x30; //启动AD转换序列//:对每项数据采集时,用到哪个通道采样可在相应子函数内设置某一通道(见Sample_AD.c)while(!ATD0STAT2L_CCF0);/*********************************************************/函数名称:void PIT_init(void)函数功能:初始化PIT 设置精确定时时间(1s)入口参数:无出口参数:无说明:无/***********************************************************/void PIT_init(void){PITCFLMT=0x00; //禁止PIT模块Bit[7] PITE:PIT模块使能位,0禁用|1使能// Bit[6] PITSWAI:等待模式下PIT停止位,0等待模式下,PIT模块正常运行| 1等待模式下,PIT模块停止产生时钟信号,冻结PIT模块// Bit[5] PITFRZ: 冻结模式下PIT计数器冻结位。

PIT和TIM(很好好)

哪位高手能传授一下如何使用9s12xs128中的计数器。

感觉书上说得有些乱,我只想实现定时计数功能,如何使用ECT模块?xs128 s 没有ECT模块,而是分成了PIT和TIM两个模块。

PIT的作用是产生周期中断,与51单片机的定时器功能一样,只是不需像51那样在中断中要重赋定时器初值。

计数是在TIM中实现,xs128只有16位一个脉冲累加器PACA(与IOC7脚相连),而dg128还有PACB,比如你用光电编码器测速,编码器传回一系列脉冲,由PACA记录脉冲数,有一个脉冲就记一个数(这与你设定的触发沿有关)。

另外,每个引脚都有一个对应的TCx寄存器,当相应引脚触发时,TIM模块中的自由计数器TCNT中的计数值就存到对应的TCx中(读回TCx),再触发一次TCNT再存入TCx(再读回),两次相减就为两次触发的间隔时间。

那请问有定时器模块吗?我想在一定时间内产生中断,在中断程序中读取基数器内的值,然后清中断。

你的想法可以,你所说的定时器模块就是PIT,比如要让单片机每50ms产生一次中断,按照Datasheet上的公式计算出你要写入PIT寄存器的值,也就是PITMTLD和PITLD这两个寄存器,对他们赋值后别忘了选通计时通道、开中断等等。

发生中断后,在这个PIT中断函数中读PACNT就行,并清除PIT的中断标志。

在xs128中,定时器用的是PIT模块,脉冲计数用的是TIM模块内的脉冲计数器PACNT;不像dg128,这两个功能都在同一个ECT模块中完成。

在这一点上要跳出按dg128的思路去想xs128误区我还是有些疑虑,我看的手册上说只有TIM模块,用的是PT0~PT7口,你说的PIT模块是指什么?我觉得应该还是TIM模块吧,只是使用内部定时中断?你到飞思卡尔官网下一个XS128手册,完整的大约9.2M,里面第347页就是:Chapter 12 Periodic Interrupt Timer (S12PIT24B4CV1),简称PIT。

飞思卡尔s12单片机-ATD模块

Page 6

二、ATD模块简介

•

• • • • • • •

第十章 单片机片内外模块 ——ATD

S12单片机ADC特性如下:

8/10/12位可选

转换速度较高,8位、8MHz、单次转换时间为2us 采样时间可编程设置 多种转换模式:数据对齐方式、单次/连续转换、转换结果比较 外触发控制 转换序列结束可产生中断,能够使能比较中断 模拟输入引脚与通用I/O口复用 多通道扫描, 1~16 转换序列长度。

ETRIGLE –外部信号触发条件选择位 ETRIGP -

ACMPIE - Internal Clock in Stop Mode Bit 0 = 禁止比较中断 1 = 使能比较中断

ATD Registers 4/12 第十章 单片机片内外模块 ——ATD

ATD Control Register 3 (ATDCTL3)

Page 10

ATD Registers 1/12 第十章 单片机片内外模块 ——ATD

ATD Control Register 0 (ATDCTL0)

WRAP[3-0] - Wrap Around Channel Select

0 = Reserved

X = WRAP[3:0]; 多通道转换模式下,从ANx回绕到AN0 1≤x ≤ 15 仅在ATDCTL5的MULT=1时有效

S8C, S4C,S2C, S1C - Conversion Sequence Length

ATD Registers 5/12 第十章 单片机片内外模块 ——ATD

ATD Control Register 4 (ATDCTL4)

注:写ATDCTL4会终止当前转换序列

SMP[2:0] - Sample Time Select, 采样时间包含的ATD时钟周期

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

周期中断定时器寄存器

4、PIT复用寄存器 PITMUX($0343)multiplex

PMUX[3..0]:PTI定时器通道3~0的复用位。 0 相应16位定时器使用微计数器0 1 相应16位定时器使用微计数器1

5、PIT中断使能寄存器 PITINTE($0344)

PINTE[3..0]:PIT定时器通道3~0的定时中断使能位。 0 PIT相应通道定时中断禁止 1 PIT相应通道定时中断使能

周期中断定时器寄存器 (PIT-periodic interrupt timer)

1、PIT控制寄存器 PITCFLMT($0340) control and force load micro timer

PITE:PIT模块使能位 0 禁止PIT 1 使能PIT PITSWAIT:等待模式PIT停止控制位 0 在等待模式下PIT正常运行 1 在等待模式下PIT停止工作 PITFRZ:冻结模式PIT计数器冻结控制位 0 在冻结模式下PIT正常运行 1 在冻结模式下PIT计数器停止运行 PFLMT[1..0]:微计数器1和0的强制加载位 1 相应的8位微计数器的加载寄存器中的值被加载到8位微计数器中 0 强制加载无效

时钟产生器模块 ——寄存器

锁相环模块 利用锁相环可以提高总线频率

—若晶振为4M —不使用锁相环:总线频率为2M —使用锁相环:总线频率可为40MHz

可通过以下锁相环模块的寄存器设置提高总线频率

—锁相环控制寄存器(PLLCTL) —时钟合成寄存器(SYNR) —时钟分频寄存器(REFDV) —时钟产生模块的标志寄存器(CRGFLG) —时钟选择寄存器(CLKSEL) —预分频寄存器(POSTDIV)

周期中断定时器寄存器

2、PIT强制加载寄存器 PITFLT($0341)

PFLT[3..0]:6位1计数器3~0的强制加载位 1相应的16位计数器的加载寄存器中的值被加载到16位计数器中 0 强制加载无效

3、PIT通道使能寄存器 PITCE($0342)channel enable

PCE[3..0]:定时器通道3~0PIT使能控制位。 1 通道使能 0 通道禁止

时钟产生器模块 ——寄存器

1、时钟分频寄存器REFDV($35)

REFFRQ[1..0] :与参考时钟有关 00 1-2M 参考时钟 外部晶振/( REFDV 1) 01 2-6M 10 6-12M 11 12M以上 REFDIV[5..0] :分频因子,有效值为0~63。

2、时钟合成寄存器SYNR($34)synthezizer

程序设计软件定时器

void delay(void) { unsigned int i,j; for(i=0;i<10;i++) for(j=0;j<10000;) j++; }

微处理器常常内置定时器(硬件定时器)

–MCS51单片机内有二个16位定时器、计数器 –MC9S12XS内置 RTI ( Real Time Interrupt) ECT – enhanced capture timer OC – Output comparer PWM – Pulse width modulationPeriod and pulse width measurement 四个24位PIT定时器

PIT模块编程范例

中断服务子程序

void interrupt 66 PIT0(void) { PITTF_PTF0=1;//清中断标志位 vTmpPIT++; if(vTmpPIT==10) { PORTB=~PORTB;//输出取反 vTmpPIT=0; } }

主程序

void main(void) { pllclk(); initIOBoutput(); initPIT(); EnableInterrupts; for(;;) {} /* wait forever */ }

LOCK :锁相环锁定标志,从外部晶振频率时钟切换到VCO时钟时需要查看该标志是否由0变为1。 1 时钟频率已稳定,锁相环频率已锁定 0 时钟频率未稳定,锁相环频率未锁定

时钟产生器模块 ——寄存器

5、时钟选择寄存器(CLKSEL)($39)

PLLSEL:选定锁相环位 1 Bus Clock=PLLCLK/2 0 Bus Clock=OSCCLK/2

第十章 单片机片内外模块

• • • • • • 10.1 并行I/O 10.2 异步串行通信SCI 10.3 同步串行通信SPI 10.4 ATD转换模块 10.5 周期中断定时器PIT 10.6 时钟产生器模块

Page 1

第十章 单片机片内外模块 ——周期中断定时器(PIT)

• • • • • 定时器简介 周期中断定时器简介(PIT) 周期中断定时器寄存器 PIT模块编程范例 时钟产生器模块

周期中断定时器寄存器

6、PIT超时标志寄存器PITTF($0345)time-out flag

PTF[3..0]:PIT定时器通道3~0的超时标志位。

0 PIT相应通道没有发生超时中断 1 PIT相应通道发生了超时中断 向该标志位写1,可以清零该标志位;写0,则无效。

7、PIT微计数器加载寄存器 PITMTLD0($0346) 和PITMTLD1($0347)

定时器简介 ——为什么使用定时器

时间延迟的产生和测量

外部信号周期和脉冲宽度的测量 事件计数器 事件发生时间比较器 波形发生器 周期性的中断产生 定时器实际上是计数器,它通过累计已知时间间隔的个数来 计算时间。被累计的时间间隔若是系统时钟,计数器就变成了定 时器。

定时器简介 ——怎样获得定时器

VCOFRQ[1..0]:压控振动器VCO的增益 00 VCO频率 32-48M 01 VCO频率 48-80M PLL 时钟 2 * OSCCLK * SYNR 1 /( REFDV 1) ( ) 10 VCO频率 80-120M 11 VCO频率 120M以上 SYNDIV[5..0]:锁相环时钟倍频数,有效值为0~63。

第十章 单片机片内外模块 ——周期中断定时器(PIT)

PIT+显示应用实例

实验7 任务:(1) 使用定时器实现跑马灯。 (2) 实现一个电子秒表 (3) 通过键盘输入闪动周期,然后实现跑马灯。 (4) 发挥:电饭煲等家电中的预约功能

Page 22

时钟产生器模块 ——寄存器

3、锁相环控制寄存器(PLLCTL)($3A)phase—locked—loop

CME: 时钟监控允许位 1 允许 0 禁止 PLLON: 锁相环电路允许位 1 允许 0 禁止

4、时钟产生模块的标志寄存器 CRGFLG($37)clock and reset generation

定时器简介 ——定时器的主要性能参数

位数 加1或是减1 时钟 重装载 周期中断定时器:4路24位定时器,每路可以分别 打开或关闭

பைடு நூலகம்

1~2^24个总线周期定时

产生中断信号

周期中断定时器简介(PIT)

定时周期=

( N 1) ( M 1) BusCLK

1、使能某一路定时器,需要写通道使能寄存器和PIT控制寄存器来使能PIT模块 2、4个16位定时器,共享2个8位微计数器,通过写PIT复用寄存器配置 3、某一路定时器使能时,16位和8位计数器对应的加载寄存器的值自动加载 4、按照MCU内部总线时钟,24计数器减1,直至为0时,自动重加载 5、同时置超时标志,若对应的定时中断被使能,则产生定时中断

定时器简介 ——怎样获得定时器

外围扩展定时器

8253内部有三个计数器 ,分别成为计数器0、计数器 1和计数器2,他们的机构完 全相同。每个计数器的输入 和输出都决定于设置在控制 寄存器中的控制字,互相之 间工作完全独立。每个计数 器通过三个引脚和外部联系 ,一个为时钟输入端CLK, 一个为门控信号输入端 GATE,另一个为输出端 OUT。每个计数器内部有一 个8位的控制寄存器,还有一 个16位的计数初值寄存器CR 、一个计数执行部件CE和一 个输出锁存器OL。

定时器简介 ——怎样获得定时器

外围扩展定时器

DS12887把时钟芯片所需的晶振和外部锂电池 相关电路集于芯片内部,可广泛用于各种需要较高 精度的实时时钟场合中。其主要功能如下: (1)内含一个锂电池,断电情况运行十年以上不丢 失数据。 (2)计秒、分、时、天、星期、日、月、年,并有 闰年补偿功能。 (3)二进制数码或BCD码表示时间、日历和定闹。 (4)12小时或24小时制,12小时时钟模式带有 PWM和AM指导,有夏令时功能。 (5)MOTOROLA5和INATAEL总线时序选择。 (6)有128个RAM单元与软件音响器,其中14个作 为字节时钟和控制寄存器,114字节为通用RAM, 所有ARAM单元数据都具有掉电保护功能。 (7)可编程方波信号输出。 (8)中断信号输出(IRQ)可以产生500ms一次到每 122μs一次的中断

6、预分频寄存器POSTDIV

POSTDIV[4..0] :预分频因子。POSTDIV 为默认时(后四位全0),fvoc =fpll。

时钟产生器模块 ——程序示例

锁相环模块寄存器设置程序示例

void pllclk(void) //外部时钟16MHz,锁相环时钟80MHz,总线时钟为40MHz { SYNR=0x53; //PLLCLK =2*OSCCLK*(SYNR + 1)/(REFDV + 1) REFDV=0x07; while(CRGFLG_LOCK==0);//时钟校正同步 CLKSEL_PLLSEL=1; }

($0356)

PCNT[15..0]:该寄存器存放16位递减计数器值

PIT模块编程示例

初始化模块

void initIOBoutput(void)//IO口初始化,B口为输出 { DDRB=0XFF; PORTB=0XFF; } void initPIT(void) //定时中断初始化函数 50ms { PITCFLMT_PITE=0; //关闭PIT模块 PITCE_PCE0=1; //定时器通道0使能 PITMUX_PMUX0=0; //定时器通道0使用微计数器0 PITMTLD0=200-1; //8位定时器初值设定。在40MHzBusClock下为5us. PITLD0=PITTIME-1; //16位定时器初值设定。PITTIME*0.005ms PITINTE_PINTE0=1;//定时器中断通道0中断使能 PITCFLMT_PITE=1; //定时器通道0使能 }