CPU型号大全【V1.1】【修正部分错误】

TCC081E数据手册V1.1

保密等级公开Q/DX 青岛鼎信通讯股份有限公司技术文档Q/TC X.XXX.XXXXXTCC081E数据手册V1.12014- 05-13发布2014- 05 - 13实施目次1 概述 (1)2 芯片特点 (1)3 芯片框图 (2)4 引脚定义 (2)4.1 芯片引脚示意图 (2)4.2 引脚定义 (3)5 芯片电器参数 (4)5.1 工作电压范围 (4)5.2 最大绝对额定值 (TA = 25°C) (4)5.3 外部复位 (4)6 芯片封装图 (5)7 注意事项 (5)TCC081E数据手册1 概述青岛鼎信通讯股份有限公司根据目前国内载波抄表市场需求,结合电网特点研发出专门应用于电力线通信介质的载波通信系统。

其核心技术利用正交码进行数据扩展频谱传输,使用电力线过零分时段得到最利于传输的3.3ms微分时段同步传输,比单纯使用扩频方式的系统通信能力和稳定性有很大提高;内置DSP数字信号处理模块保证载波通信计算需求,使用A/D采样方式进行扩频计算,其抗干扰能力大大增加。

TCC081E芯片是鼎信电力线载波通信系统中的从节点芯片,实现了基于电力线通信网络的电子终端设备之间可靠的数据交换,具备通信中继能力,可自动实现载波节点侦听、主动上报等网络功能。

TCC081E芯片的应用主要集中在自动读表、路灯控制、智能控制等领域,为电力行业或其它公共事业部门提供了一种优秀的自动抄表、控制系统解决方案。

TCC081E芯片进行鼎信规约的电力载波信号和标准DL/T645-1997/2007协议的串口信号之间的转换,支持数据透明传输模式;串口可以连接电表节点和电量显示模块,完成物理层、数据链路层、网络层、传输层四层网络功能。

2 芯片特点采用BFSK调制的扩频通信技术,载波中心频率421kHz;微分交流电时段,选择最有利于传输的时段通信;高性能数字信号处理技术;高效的帧中继转发机制,支持16级中继级别;可编程的网络地址、地址过滤、提供有效的本地访问数据;接收信号强度权重参数指示,为中继搜索算法提供支持,提高通信系统稳定性;提供准确的节点相位信息及信道特征信息;自适应50Hz、60Hz用电环境;支持断电无过零情况下的电力线载波通讯;每相载波通信速率50bps、100bps、600bps、1200bps;支持串口通信速率1200bps、2400bps、4800bps、9600bps;支持DL/T645-1997/2007、透明传输模式;上电自动读取从节点地址;登录未知表号电能表的表号;事件快速上报功能;采用5V 电源供电;温度适用范围(工业级标准) -40℃~+85℃。

曙光天阔A840r-G用户手册V1.1

硬件及数据损坏负责; 8、 当服务器出现故障时,如果您不能确定故障的原因,请及时与曙光技术支持部门联系以

获得帮助; 9、 如主板 CMOS 电池失效,请使用与本机配备的电池相同型号的电池进行更换,替换下的

的稳定运行,并将可以延长服务器的使用寿命; 2、 请使用带接地保护的三芯电源线与插座,并使用220V 交流电,不正确的电源设置可能

会导致漏电、烧毁、爆炸甚至人身伤害; 3、 请不要在服务器正在运行时插拔背板连线或是移动服务器,否则将可能造成服务器当机

或是部件损坏; 4、 请尽量避免频繁重启或开关机,以延长服务器的使用寿命; 5、 请用户及时备份重要数据,曙光信息产业有限公司不为任何情况导致的数据丢失负责; 6、 请使用正版操作系统及软件,并进行正确配置。曙光信息产业有限公司对由于操作系统

声明及注意事项

感谢您选用曙光服务器!

曙光服务器将给您带来强大的应用支持和全新的性能体验。为了您能够更安全、方便的 使用曙光服务器,在使用之前,请详细阅读本节所提示的信息。

曙光服务器在设计和制造过程中均遵循了严格的标准,以保证您所使用的服务器拥有卓 越的品质和完美的“SUMA”特性。但是服务器属于精密电子设备,在使用过程中仍然可能因 为各种原因而导致异常,所以请务必明确以下事项: 1、 请将服务器放置在阴凉、干燥、通风、洁净、无强磁场的环境中使用,这有助于服务器

电池请妥善回收处理。 曙光信息产业有限公司保留对以上条款的解释权。

再次感谢您选用曙光服务器!

-3-

曙光天阔 A840r-G 服务器用户手册 V1.1

目录

第一章 系统简介 ........................

PowerPC QorIQ P2020处理器介绍v1.1

测试例程列表:

CAN 总线通讯测试 FlexRay 总线通讯测试 Norflash 文件系统读写测试 Nandflash 文件系统读写测试 SATA 硬盘文件系统读写测试 USB 读写测试 网络通讯测试 串口通讯测试 I2C 读写测试 SPI 读写测试 Localbus 读写、中断测试 GPIO 测试 RTC 时钟测试 温度监控

和更少的竞争;

P2020 处理器应用领域:

工业控制应用 以太网交换机 军工/航空/航天 医疗电子 测试测量仪器 单板计算机 机器人 电力监控

如何快速进行基于 PowerPC 平台的应用开发:

当用户需要快速进行应用系统开发时,核心板+底板的方式可以帮助用户节省开发时间 和费用。

所谓核心板是指一种集成了嵌入式系统核心功能的电路板,通常包括中央处理器、 存 储器、电源管理芯片、晶振等相关元器件。

10) 集成安全引擎,协议支持包括 SNOW、ARC4、3DES、AES、RSA/ECC、RNG、单通道 SSL/TLS、Kasumi、XOR 加速。

QorIQ P2020 处理器优势

Freescale 半导体的 PowerPC P2020 处理器是可靠性嵌入式应用的理想基础平台。

1、 P2020 处理器集成丰富 I/O 接口,这就使得需要更低系统级 BOM 成本,减少桥路 芯片使用,高集成度缩短研发周期,降低生产成本和功耗;

板载 1GB SLC Nand FLASH; 2 路 10/100/1000M 以太网接口; 2 路串口(RS232),3 线 TTL; 1 路 USB2.0 Host 接口; 2 路 2x I²C, max. 400 kHz; 1 路 SD 卡接口,支持 4 位/8 位数据宽度; 1 路 SPI 接口,支持 4 个片选; 高速总线接口(可配置): 3 路 PCIe1.0 接口,其中 2 路(x1) ,1 路(x2); 2 路 Serial Rapid I/O (SRIO) (仅 P20xx); 2 路光纤网络接口; 1 路增强型的 Local Bus, max. 66 MHz

PowerPC QorIQ P2020处理器介绍v1.1

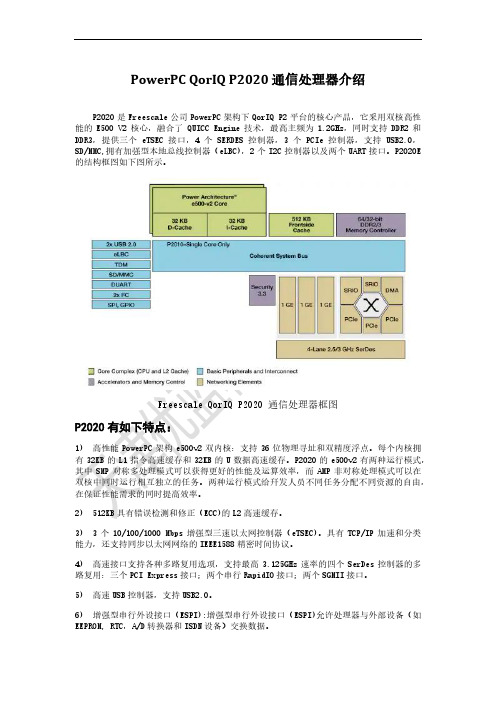

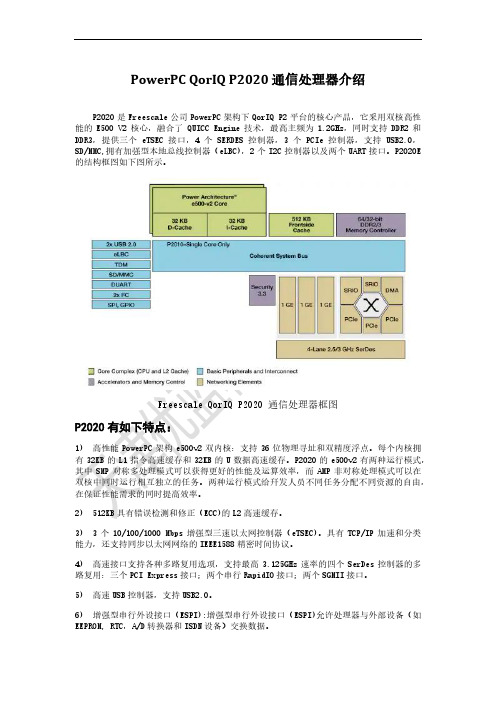

P2020 是 Freescale 公司 PowerPC 架构下 QorIQ P2 平台的核心产品,它釆用双核高性 能的 E500 V2 核心,融合了 QUICC Engine 技术,最高主频为 1.2GHz,同时支持 DDR2 和 DDR3,提供三个 eTSEC 接口,4 个 SERDES 控制器,3 个 PCIe 控制器,支持 USB2.0, SD/MMC,拥有加强型本地总线控制器(eLBC),2 个 I2C 控制器以及两个 UART 接口。P2020E 的结构框图如下图所示。

26 位地址,16 位数据,4 个片选,4 个外部中断 10 路 PPC GPIO,12 路灵活的扩展 GPIO; 支持 RTC,温度监控,看门狗,JTAG 接口; Uboot 引导 VxWorks/linux 操作系统镜像,调试过程更方便;

其他技术指标

供电指标: 电源输入:DC +5V(+/-5%) 功耗 <= 8W

Freescale QorIQ P2020 通信处理器框图

P2020 有如下特点:

1) 高性能 PowerPC 架构 e500v2 双内核:支持 36 位物理寻址和双精度浮点。每个内核拥 有 32KB 的 L1 指令高速缓存和 32KB 的 U 数据高速缓存。P2020 的 e500v2 有两种运行模式, 其中 SMP 对称多处理模式可以获得更好的性能及运算效率,而 AMP 非对称处理模式可以在 双核中同时运行相互独立的任务。两种运行模式给幵发人员不同任务分配不同资源的自由, 在保证性能需求的同时提高效率。 2) 512KB 具有错误检测和修正(ECC)的 L2 高速缓存。 3) 3 个 10/100/1000 Mbps 增强型三速以太网控制器(eTSEC)。具有 TCP/IP 加速和分类 能力,还支持同步以太网网络的 IEEE1588 精密时间协议。 4) 高速接口支持各种多路复用选项,支持最高 3.125GHz 速率的四个 SerDes 控制器的多 路复用:三个 PCI Express 接口;两个串行 RapidIO 接口;两个 SGMII 接口。 5) 高速 USB 控制器,支持 USB2.0。 6) 增强型串行外设接口(ESPI):增强型串行外设接口(ESPI)允许处理器与外部设备(如 EEPROM, RTC,A/D 转换器和 ISDN 设备)交换数据。

CPU型号大全地地总结CPU型号查询一览表

CPU型号大全总结CPU型号查询一览表一、X86时代的CPUCPU的溯源可以一直去到1971年。

在那一年,当时还处在发展阶段的INTEL公司推出了世界上第一台微处理器4004。

这不但是第一个用于计算器的4位微处理器,也是第一款个人有能力买得起的电脑处理器!!4004含有2300个晶体管,功能相当有限,而且速度还很慢,被当时的蓝色巨人IBM 以及大部分商业用户不屑一顾,但是它毕竟是划时代的产品,从此以后,INTEL 便与微处理器结下了不解之缘。

可以这么说,CPU的历史发展历程其实也就是INTEL公司X86系列CPU的发展历程,我们就通过它来展开我们的“CPU历史之旅”。

4004处理器核心架构图1978年,Intel公司再次领导潮流,首次生产出16位的微处理器,并命名为i8086,同时还生产出与之相配合的数学协处理器i8087,这两种芯片使用相互兼容的指令集,但在i8087指令集中增加了一些专门用于对数、指数和三角函数等数学计算指令。

由于这些指令集应用于i8086和i8087,所以人们也这些指令集统一称之为X86指令集。

虽然以后Intel又陆续生产出第二代、第三代等更先进和更快的新型CPU,但都仍然兼容原来的X86指令,而且Intel在后续CPU的命名上沿用了原先的X86序列,直到后来因商标注册问题,才放弃了继续用阿拉伯数字命名。

至于在后来发展壮大的其他公司,例如AMD和Cyrix等,在486以前(包括486)的CPU都是按Intel的命名方式为自己的X86系列CPU命名,但到了586时代,市场竞争越来越厉害了,由于商标注册问题,它们已经无法继续使用与Intel的X86系列相同或相似的命名,只好另外为自己的586、686兼容CPU命名了。

1979年,INTEL公司推出了8088芯片,它仍旧是属于16位微处理器,内含29000个晶体管,时钟频率为4.77MHz,地址总线为20位,可使用1MB内存。

8088内部数据总线都是16位,外部数据总线是8位,而它的兄弟8086是16位。

龙芯 1B 处理器用户手册说明书

龙芯1B处理器用户手册2016年5月龙芯中科技术有限公司版权声明本文档版权归龙芯中科技术有限公司所有,并保留一切权利。

未经书面许可,任何公司和个人不得将此文档中的任何部分公开、转载或以其他方式散发给第三方。

否则,必将追究其法律责任。

免责声明本文档仅提供阶段性信息,所含内容可根据产品的实际情况随时更新,恕不另行通知。

如因文档使用不当造成的直接或间接损失,本公司不承担任何责任。

龙芯中科技术有限公司Loongson Technology Corporation Limited地址:北京市海淀区中关村环保科技示范园龙芯产业园2号楼Building No.2, Loongson Industrial Park, Zhongguancun Environmental Protection Park,电话(Tel):************传真(Fax):************阅读指南《龙芯1B处理器用户手册》主要介绍龙芯1B架构与寄存器描述。

修订历史文档更新记录文档编号:文档名:龙芯1B处理器用户手册版本号V2.3创建人:研发中心创建日期2016-5-4更新历史序号.更新日期更新人版本号更新内容12010-6-7 研发中心V1.0 1B处理器初稿完成22010-11-13 研发中心V1.1 增加了芯片引脚排布,DDR控制器信息等32010-11-15 研发中心V1.2 修改并进行标准排版42010-11-15 研发中心V1.3 修正了第五章DDR的部分错误52011-05-08 研发中心V1.4 修订了调试发现的错误62011-05-17 研发中心V1.5 修订了多个小问题72011-11-15 研发中心V1.6GMAC0/1的RGMII和MII模式需要配置才能使用GPIO配置和复用中修改bugSPI部分,分频时钟明确是DDR2_clk/2DDR2部分,配置16/32位可配置时钟分频部分有改动添加了LCD PAD在不同显示模式下的对应关系GPIO寄存器描述修改82012-4-11 研发中心V1.7 NAND部分寄存器说明修改XTALI/O 与外部有源晶振、无源晶体连接方法92012-4-20 研发中心V1.8 PAD封装位置和封装延迟GPIO复位值和方向GMAC0/1在MII模式下信号处理Wdog地址修改USB启动需要复位10 2012-05-26 研发中心V1.9 针对修改意见,做了GPIO/ LCD/ DMA/ SPI/ UART/I2C/ NAND /CLOCK的修改11 2014-07-30 研发中心V2.0 增加质量等级和封装顶视图12 2015-3-11 研发中心V2.1 增加电特性,CAN的速率计算13 2015-4-1 研发中心V2.2 补充质量等级描述14 2016-5-4 研发中心V2.3 24.1节增加RTC功耗说明,增加焊接要求手册信息反馈:*******************目录 (1)1概述 (1)1.1体系结构框图 (1)1.2芯片主要功能 (2)1.2.1GS232 CPU (2)1.2.2DDR2 (3)1.2.3LCD Controller (3)1.2.4USB2.0 (3)1.2.5AC97 (3)1.2.6GMAC (4)1.2.7SPI (4)1.2.8UART (4)1.2.9I2C (4)1.2.10PWM (4)1.2.11CAN (5)1.2.12RTC (5)1.2.13GPIO (5)1.2.14NAND (5)1.2.15INT controller (5)1.2.16Watchdog (5)1.2.17功耗 (5)1.2.18其它 (7)1.3质量等级 (7)2芯片引脚定义 (9)2.11B引脚分布图 (9)2.2封装顶视图 (16)2.3系统相关引脚定义(6) (17)2.4LCD引脚定义(20) (17)2.5PLL引脚定义(4) (17)2.6VR引脚定义(6) (18)2.7DDR2引脚定义(71) (18)2.8USB引脚定义(10) (19)2.9EJTAG引脚定义(6) (20)2.10GMAC0引脚定义(15) (20)2.11GMAC1引脚定义(4) (20)2.12AC97引脚定义(5) (21)2.13SPI引脚定义(7) (21)2.14UART引脚定义(20) (21)2.15I2C引脚定义(2) (22)2.16CAN引脚定义(4) (22)2.17NAND引脚定义(14) (22)2.18PWM引脚定义(4) (22)2.19电源/地引脚(58) (23)3地址空间分配 (24)3.1一级AXI交叉开关上模块的地址空间 (24)3.2AXI MUX下各模块的地址空间 (24)3.3APB各模块的地址空间分配 (24)4CPU (26)4.1MIPS32指令系统结构 (26)4.1.1CPU寄存器 (27)4.1.2CPU指令集 (27)4.1.3CP0指令集 (31)4.1.4存储空间 (32)4.1.5例外处理 (33)4.1.6CP0寄存器 (35)4.2CP0指令 (53)4.3EJTAG设计 (53)4.3.1EJTAG介绍 (53)4.3.2调试控制寄存器(Debug Control Register) (54)4.3.3硬件断点 (56)4.3.4EJTAG相关的处理器核扩展 (61)4.3.5TAP接口 (64)5DDR2 (72)5.1DDR2SDRAM控制器特性 (72)5.2DDR2SDRAM读协议 (72)5.3DDR2SDRAM写协议 (73)5.4DDR2SDRAM参数设置顺序 (73)5.5DDR2SDRAM采样模式配置 (74)5.6DDR2SDRAM PAD驱动配置 (74)5.7DDR216位工作模式配置 (74)6LCD (75)6.1特性 (75)6.1.1数据格式 (75)6.2寄存器 (75)7GMAC0 (81)7.1配置成MAC的连接和复用方式 (81)7.2DMA寄存器描述 (81)7.3GMAC控制器寄存器描述 (90)7.4DMA描述符 (101)7.4.1DMA描述符的基本格式 (101)7.4.2DMA接收描述符 (102)7.4.3RDES0 (103)7.4.4RDES (104)7.4.5RDES2 (105)7.4.6RDES3 (105)7.4.7DMA发送描述符 (106)7.4.8TDES0 (106)7.4.9TDES1 (107)7.4.10TDES2 (109)7.4.11TDES3 (109)7.5软件编程向导(S OFTWARE P ROGRAMMING G UIDE): (110)8GMAC1 (112)8.1配置成MAC的连接和复用方式 (112)8.2GMAC1外部信号复用和配置 (112)8.3寄存器描述 (113)9USB HOST (114)9.1总体概述 (114)9.2USB主机控制器寄存器 (115)9.2.1EHCI相关寄存器 (115)9.2.2Capability寄存器 (115)9.2.3Operational寄存器 (116)9.2.4EHCI 实现相关寄存器 (116)INSNREG00寄存器(disable) (117)INSNREG01寄存器 (117)INSNREG02寄存器 (117)INSNREG03寄存器 (117)INSNRE04寄存器(仅用于调试,软件不必更改此寄存器) (117)INSNRE05寄存器 (118)INSNREG06寄存器 (118)INSNREG07寄存器 (118)INSNREG08寄存器 (118)9.3OHCI相关寄存器 (119)9.3.1Operational寄存器 (119)9.3.2OHCI 实现相关寄存器 (119)INSNREG06寄存器 (120)INSNREG07寄存器 (120)9.4USB主机控制器时序 (120)9.4.1数据接收时序 (120)9.4.2数据传输时序 (121)10SPI0 (123)10.1SPI控制器结构 (123)10.2SPI控制器寄存器 (124)10.2.1控制寄存器(SPCR) (124)10.2.2状态寄存器(SPSR) (124)10.2.3数据寄存器(TxFIFO/RxFIFO) (125)10.2.4外部寄存器(SPER) (125)10.2.5参数控制寄存器(SFC_PARAM) (125)10.2.6片选控制寄存器(SFC_SOFTCS) (126)10.2.7时序控制寄存器(SFC_TIMING) (126)10.3接口时序 (126)SPI主控制器外部接口时序图 (126)SPI Flash访问时序图 (127)10.4SPI F LASH控制器使用指南 (128)SPI主控制器的读写操作 (128)硬件SPI Flash读 (128)混合访问SPI Flash和SPI主控制器 (129)11SPI1 (130)11.1SPI主控制器结构 (130)12Conf and Interrupt (131)12.1配置和中断控制器总体描述 (131)12.2中断控制器寄存器描述 (132)13DMA (134)13.1DMA控制器结构描述 (134)13.2DMA控制器与APB设备的交互 (134)13.3DMA控制器 (134)13.3.1ORDER_ADDR_IN (134)13.3.2DMA_ORDER_ADDR (135)13.3.3DMA_SADDR (135)13.3.4DMA_DADDR (136)13.3.5DMA_LENGTH (136)13.3.6DMA_STEP_LENGTH (136)13.3.7DMA_STEP_TIMES (137)13.3.8DMA_CMD (137)14UART (139)14.1UART控制器结构 (139)14.2UART控制器寄存器 (140)14.2.1数据寄存器(DAT) (141)14.2.2中断使能寄存器(IER) (141)14.2.3中断标识寄存器(IIR) (141)14.2.4FIFO控制寄存器(FCR) (142)14.2.5线路控制寄存器(LCR) (142)14.2.6MODEM控制寄存器(MCR) (143)14.2.7线路状态寄存器(LSR) (143)14.2.8MODEM状态寄存器(MSR) (144)14.2.9分频锁存器 (144)15CAN (146)15.1概述 (146)15.2CAN控制器结构 (146)15.3标准模式 (147)15.3.1标准模式地址表 (147)15.3.2控制寄存器(CR) (148)15.3.3命令寄存器(CMR) (149)15.3.4状态寄存器(SR) (149)15.3.5中断寄存器(IR) (149)15.3.6验收代码寄存器(ACR) (150)15.3.7验收屏蔽寄存器(AMR) (150)15.3.8发送缓冲区列表 (150)15.3.9接收缓冲区列表 (150)15.4扩展模式 (151)15.4.1扩展模式地址表 (151)15.4.2模式寄存器(MOD) (151)15.4.3命令寄存器(CMR) (152)15.4.4状态寄存器(SR) (152)15.4.5中断寄存器(IR) (152)15.4.6中断使能寄存器(IER) (153)15.4.7仲裁丢失捕捉寄存器(IER) (153)15.4.8错误警报限制寄存器(EMLR) (154)15.4.9RX错误计数寄存器(RXERR) (155)15.4.10TX错误计数寄存器(TXERR) (155)15.4.11验收滤波器 (155)15.4.12RX信息计数寄存器(RMCR) (155)15.5公共寄存器 (155)15.5.1总线定时寄存器0(BTR0) (155)15.5.2总线定时寄存器1(BTR1) (156)15.5.3输出控制寄存器(OCR) (156)16AC97 (157)16.1AC97结构描述 (157)16.2AC97控制器寄存器 (157)16.2.1CSR寄存器 (158)16.2.2OCC寄存器 (158)16.2.3ICC寄存器 (158)16.2.4(输入输出)通道寄存器配置 (159)16.2.5Codec寄存器访问命令 (159)16.2.6中断状态寄存器/中断掩膜寄存器 (160)16.2.7中断状态/清除寄存器 (160)16.2.8OC中断清除寄存器 (160)16.2.9IC中断清除寄存器 (160)16.2.10CODEC WRITE 中断清除寄存器 (161)16.2.11CODEC READ 中断清除寄存器 (161)17I2C (162)17.1概述 (162)17.2I2C控制器结构 (162)17.3I2C控制器寄存器说明 (163)17.3.1分频锁存器低字节寄存器(PRERlo) (163)17.3.2分频锁存器高字节寄存器(PRERhi) (163)17.3.3控制寄存器(CTR) (164)17.3.4发送数据寄存器(TXR) (164)17.3.5接受数据寄存器(RXR) (164)17.3.6命令控制寄存器(CR) (164)17.3.7状态寄存器(SR) (165)18PWM (166)18.1概述 (166)18.2PWM寄存器说明 (166)19RTC (168)19.1概述 (168)19.2寄存器描述 (168)19.2.1寄存器地址列表 (168)19.2.2SYS_TOYWRITE0 (169)19.2.3SYS_TOYWRITE1 (169)19.2.4SYS_TOYMATCH0/1/2 (169)19.2.5SYS_RTCCTRL (170)19.2.6SYS_RTCMATCH0/1/2 (171)20NAND (172)20.1NAND控制器结构描述 (172)20.2NAND控制器寄存器配置描述 (172)20.2.1NAND_CMD(地址:BFE7_8000) (172)20.2.2ADDR_L(地址:BFE7_8004) (173)20.2.3ADDR_H(地址:BFE7_8008) (173)20.2.4NAND_TIMING(地址:BFE7_800C) (173)20.2.5ID_L(地址:BFE7_8010) (173)20.2.6STATUS & ID_H(地址:BFE7_8014) (173)20.2.7NAND_PARAMETER(地址:BFE7_8018) (173)20.2.8NAND_OP_NUM(地址:BFE7_801C) (173)20.2.9CS_RDY_MAP(地址:BFE7_8020) (174)20.2.10DMA_ADDRESS(地址:BFE7_8040) (174)20.3NAND ADDR说明 (174)21WATCHDOG (177)21.1概述 (177)21.2WATCH DOG寄存器描述 (177)21.2.1WDT_EN地址:(0XBFE5_C060) (177)21.2.2WDT_SET(地址:0XBFE5_C068) (178)21.2.3WDT_timer(地址:0XBFE5_C064) (178)22Clock Management (179)22.1C LOCK模块结构描述 (179)22.2C LOCK配置描述 (179)22.3系统其它C LOCK描述 (180)23GPIO and MUX (181)23.1GPIO结构描述 (181)23.2GPIO寄存器描述 (184)23.3MUX寄存器描述 (185)24AC/DC (187)24.1电源域 (187)24.2系统复位 (187)24.3推荐的工作条件 (187)24.4绝对最大额定值 (188)25热特性 (189)25.1焊接温度 (189)图目录图1-1 1B芯片结构图 (2)图 4-1 TLB表项内容 (33)图 4-2 Index 寄存器 (36)图 4-3 Random寄存器 (37)图 4-4 EntryLo0和EntryLo1寄存器 (37)图 4-5 Context寄存器 (38)图 4-6 PageMask寄存器 (38)图 4-7 Wired寄存器界限 (39)图 4-8 Wired寄存器 (40)图 4-9 HWREna寄存器 (40)图 4-10 BadVAddr寄存器 (40)图 4-11 Count寄存器和Compare寄存器 (41)图 4-12 EntryHi寄存器 (41)图 4-13 Status寄存器 (42)图 4-14 IntCtl寄存器 (43)图 4-15SRSCtl寄存器 (44)图 4-16 SRSMap寄存器 (44)图 4-17 Cause寄存器 (45)图 4-18 EPC寄存器 (46)图4-19 Processor Revision Identifier 寄存器 (46)图 4-20 Config寄存器 (47)图 4-21 Config寄存器 (48)图 4-22 Config寄存器 (48)图 4-23 Config寄存器 (49)图 4-24 Config寄存器 (49)图 4-25 WatchLo寄存器 (50)图 4-26 WatchHi寄存器 (50)图 4-27 控制寄存器性能计数寄存器 (51)图 4-28 性能计数器寄存器 (51)图 4-29 TagLo 寄存器(P-Cache) (52)图 4-30 ErrorEPC寄存器 (53)图 4-31 EJTAG调试连接示意图 (54)图 4-32 DCR寄存器格式 (55)图 4-33 硬件指令、数据断点概况 (56)图 4-34 IBS寄存器格式 (57)图 4-35 IBAn寄存器格式 (58)图 4-36 IBMn寄存器格式 (58)图 4-37 IBCn寄存器格式 (58)图 4-38 DBS寄存器格式 (59)图 4-39 DBAn寄存器格式 (60)图 4-40 DBMn寄存器格式 (60)图 4-41 DBCn寄存器格式 (60)图4-42 TAP主要部分 (64)图4-43 ALL指令示意图 (65)图4-44 Fastdata 指令示意图 (65)图 4-45 IDCODE寄存器格式 (66)图 4-46 IMPCADE寄存器示意图 (67)图 4-47 数据寄存器格式 (68)图 4-48 地址寄存器格式 (69)图 4-49 ECR格式 (69)图9-1 USB主机控制器模块图 (114)图9-2 USB主机控制器细节模块图(带EHCI控制器细节) (115)图9-3 接收时序图(16 bit UTMI接口,偶数个数据) (121)图9-4 接收时序图(16 bit UTMI接口,奇数个数据) (121)图9-5 传输时序图(16 bit UTMI接口,偶数个数据) (122)图9-6 传输时序图(16bit UTMI接口,奇数个数据) (122)图10-1 SPI 主控制器结构 (124)图10-2SPI主控制器时序图 (127)图16-1 AC97应用系统 (157)图21-1 看门狗的结构图 (177)图25.1 焊接回流曲线 (189)表目录表 4-1 CPU指令集:访存指令 (27)表 4-2 CPU 指令集:算术指令 (ALU 立即数) (28)表 4-3 CPU 指令集:算术指令 (2操作数) (28)表 4-4 CPU指令集:算术指令(3操作数, R-型) (28)表 4-5 CPU指令集:乘法和除法指令 (29)表 4-6 CPU指令集:跳转和分支指令 (29)表 4-7 CPU指令集:移位指令 (30)表 4-8 CPU指令集:特殊指令 (30)表 4-9 CPU指令集:异常指令 (30)表 4-10 CPU指令集:CP0指令 (31)表 4-11 GS232的CP0指令 (31)表 4-12 GS232IP地址空间的分配 (32)表 4-13 例外编码及寄存器修改 (33)表 4-14 例外入口地址 (34)表 4-15 GS232IP实现的CP0 寄存器 (35)表 4-16 Index寄存器各域描述 (36)表 4-17 Random寄存器各域 (37)表 4-18 EntryLo寄存器域 (37)表 4-19 Context寄存器域 (38)表 4-20 不同页大小的掩码(Mask)值 (39)表 4-21 Wired寄存器域 (40)表 4-22 HWREna寄存器域 (40)表 4-23 EntryHi寄存器域 (41)表 4-24 Status 寄存器域 (42)表 4-25 IntCtl寄存器域 (43)表 4-26 SRSCtl寄存器域 (44)表 4-27Cause寄存器域 (45)表 4-28 Cause寄存器的ExcCode域 (45)表 4-29 PRId 寄存器域 (46)表 4-30 Config 寄存器域 (47)表 4-31 Config 寄存器域 (48)表 4-32 Config 寄存器域 (48)表 4-33 Config 寄存器域 (49)表 4-34 Config 寄存器域 (49)表 4-35 WatchLo寄存器域 (50)表 4-36 WatchHi寄存器域 (50)表 4-37控制域格式 (51)表 4-38 计数使能位定义 (51)表 4-39 计数器0/1事件 (51)表 4-40 Cache Tag寄存器域 (52)表 4-41 CP0指令 (53)表 4-42 DCR寄存器域 (55)表 4-43 硬件断点寄存器 (56)表 4-44 IBS域描述 (57)表 4-45 IBCn域描述 (58)表 4-46 DBS域描述 (59)表 4-47 DBCn域描述 (60)表 4-48 调试例外优先级表 (61)表 4-49 例外屏蔽表 (62)表 4-50 Dseg划分 (63)表 4-51 Dmseg的访问情况 (63)表 4-52 Drseg的访问情况 (63)表 4-53 调试例外中断入口地址 (64)表 4-54 EJTAG指令 (64)表 4-55 TAP数据寄存器 (66)表 4-56 IDCODE寄存器说明 (66)表 4-57 IMPCODE寄存器说明 (67)表 4-58 Psz位的含义 (68)表 4-59 ECR域描述 (69)表 4-60 Sample寄存器说明 (70)表18-18-1 四路控制器描述 (166)表18-18-2 控制寄存器描述 (166)表18-18-3 主计数器设置 (166)表18-18-4 高脉冲计数器设置 (166)表18-18-5 低脉冲计数器设置 (167)表18-18-6 控制寄存器设置 (167)表24-1 1B电源域 (187)表24-2 1B上电配置引脚汇总 (187)表24-3推荐的工作条件 (187)表24-4绝对最大额定值 (188)表25-1 回流焊接温度要求 (189)1 概述龙芯1B芯片是基于GS232处理器核的片上系统,具有高性价比,可广泛应用于工业控制、家庭网关、信息家电、医疗器械和安全应用等领域。

cpu型号排行

CPU型号排行简介CPU(中央处理器)是计算机的核心部件,负责执行和处理计算机的各种指令。

不同的CPU型号拥有不同的性能和功能,因此在选择计算机或升级CPU时,了解不同CPU型号的排行非常重要。

本文将介绍一些当前流行的CPU型号,并对其性能进行综合评估。

Intel系列CPUIntel是全球最大的CPU制造商之一,其CPU产品广泛应用于台式机、笔记本电脑和服务器等设备。

以下是一些知名的Intel系列CPU型号:1. Intel Core i9-10900K•频率:3.7GHz•核心/线程数:10/20•套接字:LGA 1200•制程工艺:14nm•缓存:20MB该款CPU作为Intel顶级桌面处理器,适用于重型应用和游戏。

其多线程性能出色,能够处理复杂任务和多线程应用。

2. Intel Core i7-10700K•频率:3.8GHz•核心/线程数:8/16•套接字:LGA 1200•制程工艺:14nm•缓存:16MB这款CPU是一款高性能的桌面处理器,适用于游戏和多媒体应用。

其性能出色,能够提供流畅的体验。

3. Intel Core i5-10600K•频率:4.1GHz•核心/线程数:6/12•套接字:LGA 1200•制程工艺:14nm•缓存:12MB该款CPU适用于一般应用和轻度游戏。

虽然核心/线程数较少,但在性能和功耗方面均有不错的表现。

4. Intel Core i3-10100•频率:3.6GHz•核心/线程数:4/8•套接字:LGA 1200•制程工艺:14nm•缓存:6MB这款CPU适用于日常办公和轻度应用。

虽然性能相对较低,但其价格实惠,适合预算有限的用户。

AMD系列CPUAMD是另一个著名的CPU制造商,其CPU产品也被广泛应用于各种计算设备。

以下是一些知名的AMD系列CPU型号:1. AMD Ryzen 9 5900X•频率:3.7GHz•核心/线程数:12/24•套接字:AM4•制程工艺:7nm•缓存:70MB该款CPU是AMD顶级桌面处理器之一,适用于专业工作站和高端游戏。

NA200PLC调试说明指导书(V1.1)

NA200系列PLC模块调试指导书(V1.1)编写:审核:批准:南大傲拓科技江苏有限公司2013年6月第一章NA200CPU模块调试说明 (1)1.1 NA200CPU201-1401/1402(V1.0)模块调试说明 (1)1.1.1调试条件 (1)1.1.2调试步骤 (1)1.1.2.1通电前检查 (1)1.1.2.2通电检查 (1)1.1.2.3模块的调试 (1)1.1.2.4调试后的跳线连接 (3)1.2 NA200CPU201-2001/2002(V1.0)模块调试说明 (3)1.2.1调试条件 (3)1.2.2调试步骤 (3)1.2.2.1通电前检查 (3)1.2.2.2通电检查 (3)1.2.2.3模块的调试 (3)1.2.2.4调试后的跳线连接 (4)1.3 NA200CPU201-2401/2402(V1.0)模块调试说明 (4)1.3.1调试条件 (4)1.3.2调试步骤 (4)1.3.2.1通电前检查 (4)1.3.2.2通电检查 (5)1.3.2.3模块的调试 (5)1.3.2.4调试后的跳线连接 (5)1.4 NA200CPU201-4001/4002(V1.0)模块调试说明 (5)1.4.1调试条件 (5)1.4.2调试步骤 (6)1.4.2.1通电前检查 (6)1.4.2.2通电检查 (6)1.4.2.3模块的调试 (6)1.4.2.4调试后的跳线连接 (8)第二章NA200扩展IO模块调试说明 (9)2.1 NA200DIM201-0801\1601调试说明 (9)2.1.1调试条件 (9)2.1.2调试步骤 (9)2.1.2.1通电前检查 (9)2.1.2.2通电检查 (9)2.1.2.3模块的调试 (9)2.2 NA200DOM201-0801\1601调试说明 (10)2.2.2调试步骤 (10)2.2.2.1通电前检查 (10)2.2.2.2通电检查 (10)2.2.2.3模块的调试 (10)2.3 NA200DOM201-0802/1602调试说明 (10)2.3.1调试条件 (10)2.3.2调试步骤 (11)2.3.2.1通电前检查 (11)2.3.2.2通电检查 (11)2.3.2.3模块的调试 (11)2.4 NA200DXM201-0801/1601调试说明 (11)2.4.1调试条件 (11)2.4.2调试步骤 (12)2.4.2.1通电前检查 (12)2.4.2.2通电检查 (12)2.4.2.3模块的调试 (12)2.5 NA200DXM201-0802/1602调试说明 (12)2.5.1调试条件 (12)2.5.2调试步骤 (12)2.5.2.1通电前检查 (12)2.5.2.2通电检查 (13)2.5.2.3模块的调试 (13)2.6 NA200AIM201-0201/0401/0801调试说明 (13)2.6.1调试条件 (13)2.6.2调试步骤 (13)2.6.2.1通电前检查 (13)2.6.2.2通电检查 (13)2.6.2.3模块的调试 (14)2.7 NA200AIM201-0203/0403调试说明 (14)2.7.1 调试条件 (14)2.7.2调试步骤 (14)2.7.2.1通电前检查 (14)2.7.2.2通电检查 (15)2.7.2.3模块的调试 (15)2.8 NA200AIM201-0204/0404调试说明 (15)2.8.1调试条件 (15)2.8.2.1通电前检查 (15)2.8.2.2通电检查 (16)2.8.2.3模块的调试 (16)2.9 NA200AOM201-0201调试说明 (17)2.9.1调试条件 (17)2.9.2调试步骤 (17)2.9.2.1通电前检查 (17)2.9.2.2通电检查 (18)2.9.2.3模块的调试 (18)3.1 NA200AOM201-0202/0402调试说明 (18)3.1.1调试条件 (18)3.1.2调试步骤 (18)3.1.2.1通电前检查 (18)3.1.2.2通电检查 (18)3.1.2.3模块的调试 (19)3.2 NA200AXM201-0601调试说明 (20)3.2.1调试条件 (20)3.2.2调试步骤 (20)3.2.2.1通电前检查 (20)3.2.2.2通电检查 (20)3.2.2.3模块的调试 (21)3.3 NA200CMM201-0203模块调试说明 (22)3.3.1调试条件 (22)3.3.2调试步骤 (23)3.3.2.1通电前检查 (23)3.3.2.2通电检查 (23)3.3.2.3模块的调试 (23)3.4 NA200CMM201-0103模块调试说明 (23)3.4.1调试条件 (23)3.4.2调试步骤 (23)3.3.2.1通电前检查 (23)3.3.2.2通电检查 (24)3.3.2.3模块的调试 (24)附录二、IO模块调试记录表格 (27)附录三、NA200CPU应用程序下载说明 (30)附件四、NA200扩展IO应用程序下载说明 (36)附件五、NA200系列PLC型谱 (43)附件六、NA200 CPU组装对照表 (44)第一章NA200CPU模块调试说明1.1 NA200CPU201-1401/1402(V1.0)模块调试说明1.1.1调试条件(1)DC24V直流电源一个(2)待测NA200CPU201-1401一个(包括电源板,通道板,CPU板)(3)数字式万用表一个(4)编程线缆一根(RS232交叉线)(5)带有串口并装有NA200Pro和FlaStaSp100_v20010软件的PC一台1.1.2调试步骤1.1.2.1通电前检查(1)检查电源板,通道板,CPU板是否完好,有无碰撞变形等现象。

高通各型号处理器规格表

骁龙821

双核Kyro

Adreno

14nm

(MSM8996

+双核 2.34+2.19GHz 530

FinFET

Pro)

Kyro

653MHz

双通道 LPDDR4-

1866

LTE Cat.12(下 2016 载)/Cat.13(上 年Q3

传)

华硕ZenFone 3 Deluxe、乐视乐Pro

三星Galaxy S4(部分版 本)/S4 Active、小米

手机2S

骁龙610 28nm 四核A53

(MSM8936) LP

1.7GHz

Adreno 单通道 405 LPDDR3-800

LTE Cat.4

2014 年

Q3(取 消)

——

联想Vibe P1/Vibe Shot、索尼Xperia M4

Aqua、HTC Desire 820/826、OPPO

330

LPDDR3-800 CDMA、LTE 年Q2

450MHz

LG G2、三星Galaxy S4 LTE-A、

索尼Xperia Z Ultra、 三星Galaxy Note 3

(LTE版) 、Xperia Z1 、宏碁

Liquid S2

骁龙801 28nm 四核Krait (MSM8x74AA) HPM 400

S90、三星Galaxy

HTC One A9、三星 Galaxy C5/On5

(2016)、LG G Vista 2、Alcatel OneTouch

Idol 4、摩托罗拉 G4/G4 Plus、华为荣 耀畅玩5A、中兴Zmax

Pro/Axon 7 mini

intel cpu型号列表

intel cpu型号列表Intel CPU型号列表导言:Intel是全球知名的半导体公司,以生产高性能的中央处理器(CPU)而闻名。

自从第一款Intel CPU推出以来,公司不断推出新的型号,以满足不同用户群体的需求。

本文将列举Intel CPU型号列表,为读者提供了解和比较各款CPU的参考。

1. Intel 4004系列:- 发布年份:1971年- 介绍:Intel 4004是Intel推出的第一款商用微处理器,采用10微米制程技术,拥有2300个晶体管,主要应用于计算机计时器和测量设备。

2. Intel 8008系列:- 发布年份:1972年- 介绍:Intel 8008是Intel推出的第一款8位微处理器,与4004相比,8008的性能更强大,拥有约3,500个晶体管,主要应用于打印终端、移动通信和工业控制等领域。

3. Intel 8086系列:- 发布年份:1978年- 介绍:Intel 8086是Intel推出的第一款16位微处理器,采用16位内部总线,能够处理更大的数据量和更复杂的指令集。

8086被广泛应用于个人计算机和工业自动化等领域,为后来的x86架构奠定基础。

4. Intel 80286系列:- 发布年份:1982年- 介绍:Intel 80286是Intel推出的第二代16位微处理器,与8086相比,80286性能提升显著,支持更高的主频和更大的内存容量。

80286的推出为个人计算机的发展提供了更强大的处理能力。

5. Intel 80386系列:- 发布年份:1985年- 介绍:Intel 80386是Intel推出的第三代32位微处理器,是当时最先进的处理器之一。

80386采用32位内部总线和扩展内存管理功能,提供了更高的处理性能和更大的内存支持,为操作系统和应用程序开发提供了更多可能性。

6. Intel Pentium系列:- 发布年份:1993年- 介绍:Intel Pentium是Intel推出的第一个品牌处理器,是x86架构的一部分。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Pentium E2160 Pentium E2180 Pentium E2200 Pentium E2220 Pentium E2210 Pentium E5200 Pentium E5300 Pentium E5400 Pentium E5500 Pentium E6300 Pentium E6500

FSB 800MHz

FSB 800MHz

FSB 800MHz

FSB 800MHz

FSB 800MHz

FSB 800MHz

FSB 800MHz

FSB 800MHz

FSB 800MHz

FSB 800MHz

FSB 800MHz

FSB 800MHz

FSB 800MHz

FSB 800MHz

FSB 800MHz

2C/2T 2C/2T 2C/2T 2C/2T 2C/2T 2C/2T 2C/2T 2C/2T 2C/2T 2C/2T 2C/2T

1.8GHz 2GHz 2.2GHz 2.4GHz 2.2GHz 2.5GHz 2.6GHz 2.7GHz 2.8GHz 2.8GHz 2.93GHz

FSB 800MHz

补充说明

※带☆的为不锁倍频版本 ※EE(Extreme Edition)为 Intel 至尊版、BE(Black Edition)为 AMD 黑盒版 ※红色为停产产品 ※不包括 90nm 及以前的产品 ※总线频率为等效频率 ※列表数系列

型号

核心架构 核心代号 制造工艺 核心/线程

FSB 800MHz

FSB 800MHz

FSB 800MHz

FSB 800MHz

FSB 800MHz

FSB 800MHz

FSB 800MHz

FSB 800MHz

FSB 1066MHz

FSB 1066MHz

☆Pentium

E6500K Pentium E6600 Pentium E6700 ☞Pentium G6950

Pentium D 935

Pentium D 940

Pentium D 945

Pentium D 950

Pentium D 955

Pentium D 960

Pentium D 965

Pentium E2140

Netburst Netburst Netburst Netburst Netburst Netburst Netburst Netburst Netburst Netburst Netburst Netburst Netburst Netburst Netburst

1C/1T 1C/1T 1C/1T 1C/1T 1C/1T 1C/1T 1C/1T 1C/1T 1C/1T 2C/2T 2C/2T 2C/2T 2C/2T 2C/2T 2C/2T 2C/2T

3.06GHz 3.2GHz 3.33GHz 3.46GHz 3.6GHz 1.6GHz 1.8GHz 2GHz 2.2GHz 1.6GHz 2GHz 2.2GHz 2.4GHz 2.4GHz 2.5GHz 2.6GHz

Conroe Conroe Conroe Conroe Conroe Conroe Conroe Conroe Conroe Conroe Conroe Conroe Conroe Wolfdale Wolfdale Wolfdale Wolfdale Wolfdale Wolfdale Wolfdale Wolfdale Wolfdale

1C/2T 1C/2T 1C/2T 1C/2T 2C/2T 2C/2T 2C/2T 2C/2T 2C/2T 2C/2T 2C/2T 2C/2T 2C/4T 2C/2T 2C/4T 2C/2T

3GHz 3.2GHz 3.4GHz 3.6GHz 2.8GHz 2.8GHz 3GHz 3GHz 3.2GHz 3.2GHz 3.4GHz 3.4GHz 3.46GHz 3.6GHz 3.73GHz 1.6GHz

FSB 800MHz

512KB 512KB 512KB 512KB 512KB 512KB 512KB 512KB 512KB 512KB 512KB 512KB 512KB 1MB 1MB 1MB

虚拟化

不支持 不支持 不支持 不支持 不支持 不支持 不支持 不支持 不支持 不支持 不支持 不支持 不支持 不支持 不支持 不支持

2.2GHz 2.4GHz 2.6GHz 1.86GHz 1.86GHz 2.13GHz 2.13GHz 2.33GHz 2.33GHz 2.4GHz 2.66GHz 2.66GHz 3GHz 2.53GHz 2.66GHz 2.8GHz 2.93GHz 3.06GHz 2.66GHz 2.66GHz 2.83GHz 3GHz

2MB

奔腾系列

VT-X

73W

型号

核心架构 核心代号 制造工艺 核心/线程

主频

总线类型/ 频率

二级缓存

Pentium 4 631

Pentium 4 641

Pentium 4 651

Pentium 4 661

Pentium D 915

Pentium D 920

Pentium D 925

Pentium D 930

FSB 533MHz

FSB 533MHz

FSB 533MHz

FSB 533MHz

FSB 533MHz

FSB 800MHz

FSB 800MHz

FSB 800MHz

FSB 800MHz

FSB 800MHz

FSB 800MHz

FSB 800MHz

FSB 800MHz

FSB 800MHz

FSB 800MHz

DMI 2500MHz

☞集成 GPU 频率 533MHz 内存支持 DDR3-1066

1MB 1MB 1MB 1MB 1MB 2MB 2MB 2MB 2MB 2MB 2MB

2MB

2MB 2MB 3MB

酷睿 2 双核系列

不支持 不支持 不支持 不支持 不支持 不支持 VT-X VT-X VT-X VT-X VT-X

Core 2 Duo E7300

Core 2 Duo E7400

Core 2 Duo E7500

Core 2 Duo E7600

Core 2 Duo E8190

Core 2 Duo E8200

Core 2 Duo E8300

Core 2 Duo E8400

Core Core Core Core Core Core Core Core Core Core Core Core Core Core Core Core Core Core Core Core Core Core

Core 2 Duo E6320

Core 2 Duo E6400

Core 2 Duo E6420

Core 2 Duo E6540

Core 2 Duo E6550

Core 2 Duo E6600

Core 2 Duo E6700

Core 2 Duo E6750

Core 2 Duo E6850

Core 2 Duo E7200

FSB 800MHz

FSB 800MHz

FSB 800MHz

Core Core Core

Westmere

Wolfdale 45nm

2C/2T

FSB 2.93GHz

1066MHz

Wolfdale 45nm

2C/2T

FSB 3.06GHz

1066MHz

Wolfdale 45nm

2C/2T

3.2GHz

FSB 1066MHz

Clarkdale 32nm

2C/2T

2.8GHz

Netburst Allendale

Netburst Allendale

Netburst Allendale

Core Wolfdale

Core Wolfdale

Core Wolfdale

65nm 65nm 65nm 65nm 65nm 65nm 65nm 65nm 65nm 65nm 65nm 65nm 65nm 45nm 45nm 45nm

TDP

86W 86W 86W 65W 65W 35W 35W 35W 35W 65W 65W 65W 65W 65W 65W 65W

☞Celeron G1101

Westmere

Clarkdale 32nm

2C/2T

DMI 2.26GHz

2500MHz

☞集成 GPU 频率 533MHz 内存支持 DDR3-1066

65nm 65nm 65nm 65nm 65nm 65nm 65nm 65nm 65nm 65nm 65nm 65nm 65nm 45nm 45nm 45nm 45nm 45nm 45nm 45nm 45nm 45nm

2C/2T 2C/2T 2C/2T 2C/2T 2C/2T 2C/2T 2C/2T 2C/2T 2C/2T 2C/2T 2C/2T 2C/2T 2C/2T 2C/2T 2C/2T 2C/2T 2C/2T 2C/2T 2C/2T 2C/2T 2C/2T 2C/2T

FSB 800MHz

2MB 2MB 2MB 2MB 4MB 4MB 4MB 4MB 4MB 4MB 4MB 4MB 4MB 4MB 4MB 1MB

虚拟化

不支持 不支持 不支持 不支持 不支持 VT-X 不支持 VT-X 不支持 VT-X 不支持 VT-X VT-X VT-X VT-X 不支持

TDP

86W 86W 86W 86W 95W 95W 95W 95W 95W 95W 95W 95W 95W 95W 95W 65W

65nm 65nm

2C/2T 2C/2T