ModelSim10.1中代码覆盖率查看

PERL生成遍历文件和MODELSIM覆盖率检测方法

1用Perl语言编程生成不同工作模式的测试文件Perl是一种通用且应用广泛的脚本语言,可以不需要编译而直接解释运行,可移植能力强,兼有多种语言的精华和特性,效率也比较高,基于这些方面的优越性,其在实际的IC 设计和验证中得到了广泛的应用。

Perl的安装在Linux系统下和大部分的UNIX系统下,perl都是随系统安装的,Windows 需要下载安装perl,推荐使用ActivePerl,下载安装后可已在命令行输入perl–v来查看是否正确安装和perl的版本(见图1.1),通过perl xxx.pl来解释运行perl程序。

图 1.1perl版本查看test_enc.vhd文件中69-75行的作用是通过设置4个变量pat_code、pat_disturb、pat_mix 和pat_frame的值来指定一种工作模式,根据它们的取值范围可以得出总共会有8*4*4*16=2048种组合,对应2048种工作模式。

Perl语言有别于其他语言的特性中,最重要的就是对正则表达式的支持,可以方便快捷的处理字符串相关的问题,因此可以利用这种特性,通过查找变量字符串和替换指令(s///)进行对测试文件变量值的更改,产生不同工作模式的激励。

s///:替换运算符。

s/searchattern/replacement/表示查找searchattrn并用replacement代替。

利用4层for循环编写perl程序,每次循环查找一个变量并改变变量的值,然后输出一个文件名与变量值相关的vhd文件(例如4个变量值分别为“011”、“11”、“01”、“1111”时文件名可以设为test_3_3_1_15.vhd。

需要注意的是,变量的值是一定位的二进制数,循环变量则默认为十进制数,所以要进行十进制与二进制数的转换,并在高位为0时也要显示出来。

新建一个txt文件,并输入程序,保存文件名为test_gen并修改后缀为.pl,生成test_gen.pl 文件,打开命令行,跳转到文件所在目录,输入:perl test_gen.pl,按回车键解释运行便会得到2048个vhd文件,对应不同的工作模式,而且参数的选值与各个文件的名字相关,方便进行选取和测试。

ModelSim10.1中代码覆盖率查看

3、查看代码覆盖率•代码覆盖率常常被拿来作为衡量测试好坏的指标,甚至,用代码覆盖率来考核测试任务完成情况,比如,代码覆盖率必须达到80%或 90%。

•Modelsim代码覆盖率功能Code coverage,能报告出statement(语句)、branch(分支)、condition(条件)、expression(表达)、toggle(信号翻转)、fsm(有限状态机)等多种覆盖率情况。

Compile/CompileProperties...)覆盖率选项卡2、弹出ProjiectCompiler Settings选项卡,单击Coverage选项,如下图•3、选择如图,单击OK后,Compile All这4个都选上这3个只能选一个丆最好选上面二者之一丆否则后面无法加载波形图0/1或1/0翻转高阻变为0或1也被认为是下降沿丆在6.2之后的版本才有选择默认即可选择前两项•4、如图,切换到Library空间,右键如图所示,选择Simulate withCoverage,如下图为我在testbench中调用了系统函数$stop(),所以会自动停止仿真。

或者多单击几次Run,然后单击Break暂停仿真),如图•7、这时仿真界面会多出很多窗口,如右最大化图标图,有Instance、Files等窗口选项。

最大化Instance窗口,如下图覆盖率高显示绿色丆覆盖率低显示红色。

如果覆盖率低丆需要修改代码丆直到覆盖率满足要求为止。

出代码覆盖率报告•9、选择默认就可以了,单击OK,得到覆盖率报告TXT文件,如下图完成。

代码覆盖率说明个人总结

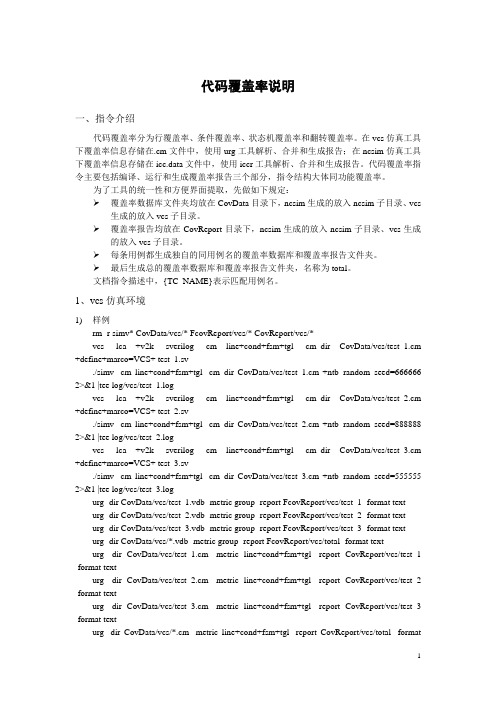

代码覆盖率说明一、指令介绍代码覆盖率分为行覆盖率、条件覆盖率、状态机覆盖率和翻转覆盖率。

在vcs仿真工具下覆盖率信息存储在.cm文件中,使用urg工具解析、合并和生成报告;在ncsim仿真工具下覆盖率信息存储在icc.data文件中,使用iccr工具解析、合并和生成报告。

代码覆盖率指令主要包括编译、运行和生成覆盖率报告三个部分,指令结构大体同功能覆盖率。

为了工具的统一性和方便界面提取,先做如下规定:覆盖率数据库文件夹均放在CovData目录下,ncsim生成的放入ncsim子目录、vcs生成的放入vcs子目录。

覆盖率报告均放在CovReport目录下,ncsim生成的放入ncsim子目录、vcs生成的放入vcs子目录。

每条用例都生成独自的同用例名的覆盖率数据库和覆盖率报告文件夹。

最后生成总的覆盖率数据库和覆盖率报告文件夹,名称为total。

文档指令描述中,{TC_NAME}表示匹配用例名。

1、vcs仿真环境1)样例rm -r simv* CovData/vcs/* FcovReport/vcs/* CovReport/vcs/*vcs -lca +v2k -sverilog -cm line+cond+fsm+tgl -cm_dir CovData/vcs/test_1.cm +define+marco=VCS+ test_1.sv./simv -cm line+cond+fsm+tgl -cm_dir CovData/vcs/test_1.cm +ntb_random_seed=666666 2>&1 |tee log/vcs/test_1.logvcs -lca +v2k -sverilog -cm line+cond+fsm+tgl -cm_dir CovData/vcs/test_2.cm +define+marco=VCS+ test_2.sv./simv -cm line+cond+fsm+tgl -cm_dir CovData/vcs/test_2.cm +ntb_random_seed=888888 2>&1 |tee log/vcs/test_2.logvcs -lca +v2k -sverilog -cm line+cond+fsm+tgl -cm_dir CovData/vcs/test_3.cm +define+marco=VCS+ test_3.sv./simv -cm line+cond+fsm+tgl -cm_dir CovData/vcs/test_3.cm +ntb_random_seed=555555 2>&1 |tee log/vcs/test_3.logurg -dir CovData/vcs/test_1.vdb -metric group -report FcovReport/vcs/test_1 -format texturg -dir CovData/vcs/test_2.vdb -metric group -report FcovReport/vcs/test_2 -format texturg -dir CovData/vcs/test_3.vdb -metric group -report FcovReport/vcs/test_3 -format texturg -dir CovData/vcs/*.vdb -metric group -report FcovReport/vcs/total -format texturg -dir CovData/vcs/test_1.cm -metric line+cond+fsm+tgl -report CovReport/vcs/test_1 -format texturg -dir CovData/vcs/test_2.cm -metric line+cond+fsm+tgl -report CovReport/vcs/test_2 -format texturg -dir CovData/vcs/test_3.cm -metric line+cond+fsm+tgl -report CovReport/vcs/test_3 -format texturg -dir CovData/vcs/*.cm -metric line+cond+fsm+tgl -report CovReport/vcs/total -format text2)指令说明(1)编译-lca:增加LCA的支持,vcs0812及以后的版本需要,此前的版本不需要。

modelsim-中代码覆盖率使用详解

一、代码覆盖率

Modelsim代码覆盖率功能Code coverage,能报告出statement(语句)、branch(分支)、condition(条件)、expression(表达)、toggle(信号翻转)、fsm(有限状态机)等多种覆盖率情况。

1、编译选项(compile option):

在Modelsim的Workspace里选中需要查看代码覆盖率的文件,然后点击右键选择compile—>compile properties,如下图,

之后选择“Coverage”选项,出现下图所示的窗口,根据需要选择选项,这里选statement、branch、condition、expression和toggle。

选完点ok。

2、编译(compile)

点工具栏中的,编译所有的选中的文件,成功后进行下面的步骤。

3、仿真(simulate)

点工具栏中的,出现下面的窗口:

(注:不要选择“Enable optimization”)

选择Others,出现如下图所示的窗口:。

浅析vivado和ModelSim联合仿真信号处理

浅析vivado和ModelSim联合仿真信号处理摘要:本文基于对识别音抗干扰模块的功能仿真,来浅析基于信号处理类的FPGA设计的仿真过程。

通过MATLAB仿真产生激励数据文件,由vivado开发软件读取测试数据作为输入数据源,联合Modelsim产生相应的输出波形和文件进行分析,以此来判断FPGA程序是否满足设计需求。

关键词:功能仿真;信号处理类;Vivado;Modelsim;1 引言数字信号处理系统在很多领域中,都发挥着十分重要的作用,随着社会的不断发展,对于数字信号处理系统的功能设计要求也日益提升。

FPGA技术的发展,在数字信号处理系统设计中,能够发挥出良好的作用与效果,而功能仿真是FPGA 项目开发中重要一环,它是确保HDL设计代码在功能上准确无误的重要方法,对于FPGA设计效率和质量的提升,有着极大的积极作用。

本文以对识别音抗干扰模块的功能仿真做为应用背景,结合实际经验,探究了信号处理类的FPGA设计的仿真过程。

2 识别音抗干扰模块的功能仿真2.1 识别音抗干扰模块功能简介仪表着陆功能不仅具备引导着陆功能,还可以通过识别音信号告知飞行员飞临的机场编码。

识别音信号是用1020Hz±50Hz单音幅度调制到航向射频载波上产生,调制度在5%至15%限度之间。

识别音发送采用国际莫尔斯电码形式,因此1020Hz±50Hz单音为键控调制。

飞机在进场着陆时(射频信号强度在-101dBm左右),作用距离较远处,本身射频载波信号幅度很小,空间存在干扰信号,加之识别音信号调制度浅,键控调制的识别音信号很难区分。

很有可能会出现识别音信号解析错误的情况。

针对上述问题,提出改进方法以提高识别音功能抗干扰能力。

此处的识别音抗干扰模块代码为mores_process.vhd。

2.2 在Vivado中和ModelSim进行联合仿真Modelsim是优秀的HDL仿真软件之一,它能提供友好的仿真环境,是业界唯一的单内核支持VHDL和Verilog混合仿真的仿真器。

代码覆盖率说明(个人总结)

代码覆盖率说明一、指令介绍代码覆盖率分为行覆盖率、条件覆盖率、状态机覆盖率和翻转覆盖率。

在vcs仿真工具下覆盖率信息存储在.cm文件中,使用urg工具解析、合并和生成报告;在ncsim仿真工具下覆盖率信息存储在icc.data文件中,使用iccr工具解析、合并和生成报告。

代码覆盖率指令主要包括编译、运行和生成覆盖率报告三个部分,指令结构大体同功能覆盖率。

为了工具的统一性和方便界面提取,先做如下规定:➢覆盖率数据库文件夹均放在CovData目录下,ncsim生成的放入ncsim子目录、vcs 生成的放入vcs子目录。

➢覆盖率报告均放在CovReport目录下,ncsim生成的放入ncsim子目录、vcs生成的放入vcs子目录。

➢每条用例都生成独自的同用例名的覆盖率数据库和覆盖率报告文件夹。

➢最后生成总的覆盖率数据库和覆盖率报告文件夹,名称为total。

文档指令描述中,{TC_NAME}表示匹配用例名。

1、vcs仿真环境1)样例rm -r simv* CovData/vcs/* FcovReport/vcs/* CovReport/vcs/*vcs -lca +v2k -sverilog -cm line+cond+fsm+tgl -cm_dir CovData/vcs/test_1.cm +define+marco=VCS+ test_1.sv./simv -cm line+cond+fsm+tgl -cm_dir CovData/vcs/test_1.cm +ntb_random_seed=666666 2>&1 |tee log/vcs/test_1.logvcs -lca +v2k -sverilog -cm line+cond+fsm+tgl -cm_dir CovData/vcs/test_2.cm +define+marco=VCS+ test_2.sv./simv -cm line+cond+fsm+tgl -cm_dir CovData/vcs/test_2.cm +ntb_random_seed=888888 2>&1 |tee log/vcs/test_2.logvcs -lca +v2k -sverilog -cm line+cond+fsm+tgl -cm_dir CovData/vcs/test_3.cm +define+marco=VCS+ test_3.sv./simv -cm line+cond+fsm+tgl -cm_dir CovData/vcs/test_3.cm +ntb_random_seed=555555 2>&1 |tee log/vcs/test_3.logurg -dir CovData/vcs/test_1.vdb -metric group -report FcovReport/vcs/test_1 -format text urg -dir CovData/vcs/test_2.vdb -metric group -report FcovReport/vcs/test_2 -format text urg -dir CovData/vcs/test_3.vdb -metric group -report FcovReport/vcs/test_3 -format text urg -dir CovData/vcs/*.vdb -metric group -report FcovReport/vcs/total -format texturg -dir CovData/vcs/test_1.cm -metric line+cond+fsm+tgl -report CovReport/vcs/test_1 -format texturg -dir CovData/vcs/test_2.cm -metric line+cond+fsm+tgl -report CovReport/vcs/test_2 -format texturg -dir CovData/vcs/test_3.cm -metric line+cond+fsm+tgl -report CovReport/vcs/test_3 -format texturg -dir CovData/vcs/*.cm -metric line+cond+fsm+tgl -report CovReport/vcs/total -formattext2)指令说明(1)编译-lca:增加LCA的支持,vcs0812及以后的版本需要,此前的版本不需要。

modelsim使用命令

1. 常用仿真命令vlib work // 建立work仿真库vmap work wrok // 映射库vlog -cover bcest *.v // 加覆盖率分析的编译vsim -coverage -voptargs="+acc" -t ns test // 仿真文件为test.vadd wave * // 将所有模块waveform. dump出来add wave sim:/test/t/M2/Reg_out // 将模块Reg_out中的waveform. dump出来delete wave /test/i2. SVA 断言仿真命令vlog -sv a.vvsim -assertdebug testview assertionsvsim -assertdebug ScaleBlock_tf -L xilinxcorelib_ver -L unisims_ver // 加载xilinxlib库3. verror 3601 // 查错4. 给仿真工具加载xilinx 库命令(1)加载之前将modelsim.ini改为非“只读”(2)“运行” cmd,到xilinx目录下(3) C:\Xilinx > compxlib -s mti_se -p c:\Modeltech_6.0\win32 -f all -l verilog -o C:\ Modeltech_6.0\Xilinx_lbis或者Xilinx目录下.\bin\nt\下有compxlib.exe简单得modelsim命令行仿真用do文件进行仿真真得很方便,比写testbench方便多了,我是深有感触呀,开始时因为不知道,只知道写testbence,在小得模块也写testbench,真得很烦躁!而且信号定义什么得比较多,采用do文件得方法就没有那么多信号定义了,管理也比较方便,呵呵,真得很方便,而且采用命令行得形式,感觉特有成就感,呵呵!1.运行仿真,在主窗口输入命令:vsim work.实体名2.为时钟信号添加驱动,输入命令:force clk 0 0,1 10 -r 20,将仿真时钟设为50MHz;(设时间单位为ns)3.打开波形窗口,输入命令:view wave4.为波形窗口添加信号,输入命令:add wave -hex *,这里的*表示添加设计中所有的信号,-hex 表示以十六进制来表示波形窗口中的信号值;5.开始仿真,输入命令,run 3us,这时候在波形窗口中出现仿真波形6.退出仿真,输入命令:quit –sim。

Modelsim与debussy在FPGA仿真和debug中的应用

Modelsim与debussy在FPGA仿真和debug中的应⽤仿真是FPGA设计中的⼀个⾮常重要的环节,但很多朋友在做FPGA设计的过程中,却并没有意识到仿真的作⽤,也没有⼀个好的仿真流程来保证仿真验证的效果。

我们做仿真的⽬的是要通过仿真找到设计中潜在的问题并解决之,这就需要⼀个debug 的过程。

在这篇⽂章中,会讨论⼀下我对FPGA设计中仿真验证和debug的看法,也介绍⼀下modelsim+Debussy在仿真和debug中的应⽤流程。

记得在学校的时候,搭硬件系统要⽤到FPGA。

那时候没有任何FPGA设计的经验,也没有好的设计流程可以参考。

在做设计的时候,基本上是很随意的去写代码,很少顾及到甚⾄很基本的设计原则。

代码写好后,尽管有验证代码正确性的意识,但并没有成熟可靠的⽅法可以使⽤,基本上就是画⼀些简单的波形作为激励信号,通过开发软件⾃带的仿真⼯具,⼤概看⼀下输出的波形是不是正确。

这样做存在很多问题。

⾸先测试覆盖率⾮常的低,激励信号不可能做的很复杂,不可能涵盖所有需要验证的设计环节;再者就是要看被测设计的输出波形来检验设计是否正确,这样就需要⼤量的时间,效率很低。

在发现设计有问题的时候,检查设计代码,也⽤很原始的⼿段,⼀⾏⼀⾏的去查看,没有意识到或者说根本就不知道有⼯具软件可以来做trace。

更通常的验证⽅法就是在FPGA程序写好以后,综合出来,烧录到实际的系统中,在系统上直接验证。

但这种做法,效率低下且有问题的话,很难debug。

另外⽐较糟糕的是很难发现⼀些⽐较特殊的问题。

后来在公司的时候,做IC设计,公司有⽐较成熟和完善的设计流程。

主要⽤NC来做仿真,⽤debussy来做debug。

成熟和完善的设计流程带来的就是⽐较⾼的仿真的效率和⽐较⾼的覆盖率,我们在debug的时候,基于⽐较好的流程和⽅法,效率也⽐较⾼。

数年⼯作下来,让我建⽴起了⼀个基本的仿真验证的概念,这个时候,再回头看当初做FPGA设计的时候所遇到的问题,感触颇深。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3、查看代码覆盖率

•代码覆盖率常常被拿来作为衡量测试好坏的指标,甚至,用代码覆盖率来考核测试任务完成情况,比如,代码覆盖率必须达到80%或 90%。

•Modelsim代码覆盖率功能Code coverage,能报告出statement(语句)、branch(分支)、condition(条件)、expression(表达)、toggle(信号翻转)、fsm(有限状态机)等多种覆盖率情况。

Compile/Compile

Properties...)

覆盖率选项卡2、弹出Projiect

Compiler Settings选

项卡,单击

Coverage选项,如

下图

•3、选择如图,单击OK

后,Compile All

这4个都选上

这3个只能选一个丆

选上面二者之一丆

否则无法查看翻转

覆盖率0/1或1/0翻转高阻变为0或1也被认为是下

降沿丆在6.2之

后的版本才有

选择默认即可

选择前两项

•4、如图,切换到Library空间,右键如图所示,选择Simulate with

Coverage,如下图

为我在testbench中

调用了系统函数

$stop(),所以会自

动停止仿真。

或者

多单击几次Run,

然后单击Break暂

停仿真),如图

•7、这时仿真界面会

多出很多窗口,如右

最大化图标图,有Instance、Files

等窗口选项。

最大化

Instance窗口,如下图

覆盖率高显示绿色丆覆盖率低显示红色。

如果覆盖率低丆需要修改代码丆直到覆盖率满足要求为止。

出代码覆盖率报告

•9、选择默认就可以了,单击OK,得到覆盖率报告TXT文件,如下

图

完成。