多处理机系统

多核处理器体系结构及并行程序设计

13

Floating Point

Integer

Floating Point

Integer

L1 D-Cache and D-TLB

L1 D-Cache and D-TLB

Even 2 floating point threads can be executed at the same time now (per processor) as there are multiple floating point execution units

– 只共享系统总线,独立缓存 – 高性能,资源冲突少

9

双核技术 VS. 超线程技术

• 双核是真正意义上的双处理器

– 不会发生资源冲突 – 每个线程拥有自己的缓存、寄存器和运算器

• 一个3.2GHz Smithfiled在性能上并非等同于3.2GHz P4 with HT 的2 倍

Integer

Rename/Alloc uop Queues Schedulers

BTB & I-TLB Decoder

Trace Cache

Floating Point

uCode ROM

2 threads CANNOT be executed at the same time (per processor) if

BTB & I-TLB Decoder

Trace Cache

Floating Point

uCode

ROM

14

多核技术与超线程技术的结合

Dual Core

2 threads/socket

Dual Core with Hyper-Threading

单处理器系统和多处理器系统介绍

单处理器系统和多处理器系统介绍如果一个计算机系统只包括一个运算处理器,则称之为单机系统;如果有多个运算处理器,则称之为多机系统。

早期的计算机系统是基于单个处理器的顺序处理机器。

程序员编写串行执行的代码,让其在CPU上串行执行,甚至每一条指令的执行也是串行的(取指令、取操作数、执行操作、存储结果)。

为提高计算机处理的速度,首先发展起来的是联想存储器系统和流水线系统,ghost win7前者提出了数据驱动的思想,后者解决了指令串行执行的问题,这两者都是最初计算机并行化发展的例子。

随着硬件技术的进步,并行处理技术得到了迅猛的发展,计算机系统不再局限于单处理器和单数据流,各种各样的并行结构得到了应用。

目前计算机系统可以分为以下4类。

(1)单指令流单数据流(SISD)。

一个处理器在一个存储器中的数据上执行单条指令流。

(2)单指令流多数据流(SIMD)。

单条指令流控制多个处理单元同时执行,每个处理单元包括处理器和相关的数据存储,一条指令事实上控制了不同的处理器对不同的数据进行操作。

向量机和阵列机是这类计算机系统的代表。

(3)多指令流肀数据流(MISD)。

一个数据流被传送给一组处理器,通过这一组处理器卜.的不同指令操作最终得到处理结果。

该类计算机系统的研究尚在实验室阶段。

(4)多指令流多数据流(MIMD)。

多个处理器对各自不同的数据集同时执行不同的指令流。

可以把MIMD系统划分为共享内存的紧密耦合MIMD系统和内存分布的松散耦合MIMD系统两大类。

根据处理器分配策略,紧密耦合M1MD系统可以分为主从式系统(Main/Slave Multiprocessor)和对称式系统(Symmetric Multiprocessor,SMP)两类。

主从式系统的基本思想是:在一个特別的处理器上运行操作系统内核,其他处理器上则运行用户程序和操作系统例行程序,内核负责分配和调度各个处理器,并向其他程序提供各种服务(如输人输出)。

系统结构——多处理机

. . .

采用总线结构的多处理机系统

优点: (1)系统硬件成本最低且最简单,每个处理机的物理 接口、寻址、判优和分时逻辑线路与单处理机系统相同。 (2)通过增、删功能模块可方便地改变系统硬件配臵。

缺点: (1)全部存贮访问都要经过总线,所以全系统的速度 受到总线工作周期的限制,带宽窄,可连接的处理机数少。 (2)系统以增加模块方式进行扩充会降低整个系统的 吞吐率; (3)这种互联方式其可靠性差,系统效率较低。

第六章 多处理机

一、 多处理机的硬件结构

二、 多处理机高速缓冲存储器(cache)一致性

三、 多处理机的操作系统 四、 机群系统 五、 新型计算机系统结构

一、 多处理机的硬件结构 一、多处理机概念 一种系统构造方式; 多个处理机共享主存或输入输出的子系统; 统一操作系统控制; 实现作业,任务级甚至指令级间并行。 多计算机系统: 共享主存; 每个处理机都有自己局部存储器,甚至输入、输出设备, 本身就构成了一台完整的计算机; 每台计算机分别受各自独立操作系统控制,机间往往以通 道或通信线路进行通讯,以文件或数据集交互作用实现任务 作业级并行。

多级互连网

MIMD和SIMD计算机都使用多级网络。每一级都用了多 个a×b开关,相邻各级开关之间都有固定的级间连接。为了 在输入和输出之间建立所需的连接,可用动态设臵开关的状 态来实现。

各种多级网络的区别就在于所用开关模块、控制方式和 级间连接(ISC)模式的不同。最简单的开关模块是2×2开 关。前面介绍的有立方体多级网,多级混洗交换网等。这些 交叉开关在处理机时比较复杂,可采用改进的方法,即把多 个较小规模交叉开关“串联”和“并联”,组成多级交叉开 关网络。

)

X:数据 CT

CP1

多处理机系统介绍(翻译)

多处理机系统介绍随着用户计算需求的增长,多处理系统能够提供一个自然地、不断提高的升级途径。

只要核心的用户程序能够提供线程级并行,给系统添加处理器,或者将较小的系统替换为较大的、包含更多处理器的系统,都能给用户提供一个直接增加计算能力的途径。

其次,多处理机系统使系统供应商能够将单个微处理器的设计代价分摊到多种设计方案中,这些设计方案能够提供不同层次的性能和扩展能力。

最后,使用一致共享存储器的多处理机系统能够提供与分时共享的但处理机兼容的编程模式,便于用户使用以前已经存在的应用程序,也便于开发新的应用程序。

在这些系统中,硬件和操作系统软件综合起来提供给用户和程序员的功能界面,实际上是基于以下4点多处理机理想假设:完全共享存储器即系统中所有处理机对所有物理存储器的访问都是平等的。

单位延迟即所有的访存请求都能在一个周期内满足。

无竞争即一个处理机的访存不会受到另一个处理机访存的影响。

写的瞬间船舶即某个处理机写存储器导致的更新立刻对所有的处理机可见。

系统及处理机的设计者必须努力使系统尽量接近这些理想假设,从而满足用户对于性能和正确性的要求。

显然,在实现这些目标时,诸如造价以及可扩展性等因素起着重要作用,但是一个优秀的系统必须很好的满足这些假设。

完全共享存储器,单位延迟以及无竞争诸如图9.4所示,大多数提供一致存储器访问(UMA,Uniform Memory Access)的传统共享存储器多处理机系统使用一种“dancehall”的组织结构,一组存储器模块或者存储体通过交叉开关互联网络与另一组处理机连接起来,并且每个处理机通过交叉开关访问存储器的延迟是相通的。

这种方法的弊端在于交叉开关的价格,该价格会随着处理机和存储器的总数按平方增长,同时每次访存都必须穿过交叉开关,另一种方法是非一致存储访问(NUMA,Nonuniform Memory Access),许多系统供应商现在都按照这种方法构造系统,在这种方法中,处理机仍然通过一个交叉开关互联网络连接在一起,但是每个处理机有一个本地的存储器,它的访问延迟要低得多,在NUMA结构中,只有对远程存储器的访问才存在穿越交叉开关的延迟开销。

多处理机new

1. 二维数组的无冲突访问存储器 • 要求:一个n×n的二维数组,按行、列、对 角线和反对角线访问,并且在不同的变址位 移量情况下,都能实现无冲突访问。 • 顺序存储:按行、对角线访问没有冲突,但 按列访问每次冲突

0 号体 体内地址 0 1 2 3

2012年8月15日星期三

1 号体

2 号体

3 号体

16

3. 二维数组的无冲突访问存储方案(之二) • 规则:对于任意一个n×n的数组,如果能够 找到满足n=22P关系的任意自然数p,则这个 二维数组就能够使用n个并行存储体实现按行、 列、对角线和反对角线的无冲突访问。 • 4×4数组用4个存储体的无访问冲突存储方案

0 号体 体内地址 0 1 2 3

或(SSM,Scalable Shared-Memory)

物理上分离的多个存储器可作为一个逻辑上共享的 存储空间进行编址.

• 通信机制:可利用Load和Store指令中的地址隐 含地进行数据通信. 2.多计算机(multicomputers)

整个地址空间由多个独立的地址空间构成,它们在逻 辑上是独立的,远程的处理器不能对其直接寻址.

2012年8月15日星期三 计算机系统结构 第九章 多处理机 18

7.2.1.2 多处理机的Cache一致性

1. Cache不一致性原因

• 在并行处理机和多处理机系统中,采用局部 Cache会引起Cache与共享存储器之间的一致 性问题。 • 出现不一致性问题的原因有三个: 共享可写的数据、进程迁移、I/O传输

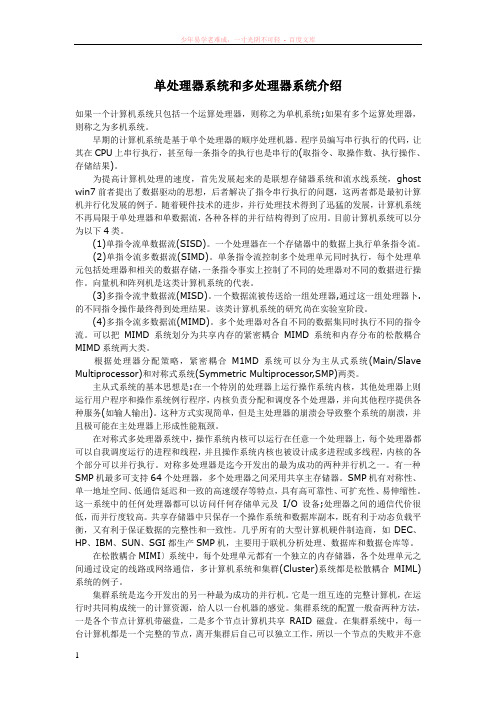

第七章 多处理机

• 多处理机定义: 两个或两个以上处理机(包括PU和CU),通 过高速互连网络连接起来,在统一的操作 系统管理下,实现指令以上级(任务级、 作业级)并行。 • 按照Flynn分类法,多处理机系统属于 MIMD计算机 • 研究多处理机的目的:提前10年得到性能 高100倍的高性能计算机系统。

CA第五章—多处理机系统.

• SIMD(Single-Instruction Multi-Data,带分布存 储器)

• MISD(Multi-Instruction Single-Data,搏动式阵 列)

• MIMD(Multi-Instruction Multi-Data,带共享存储 器)

出端编码与连接的入端结点编码相差2i。

互连函数:

PM2I+i(j)=(j+2i) mod N; n=log2N,0≤i≤n-1,

PM2I-i(j)=(j-2i) mod N; 0≤j≤N-1 共有2n个互连函数(2n-1种不同)。 0

连接图:

1

7

±0:顺环圆周连接;

2

6

±1:顺环内接n/2边形连接;

特性要求--高效率的同步原语

• 处理机设计时必须能提供作为同步原语基础的 某种不可再分的操作。这些同步原语需要有互 斥机构支持。当两个以上的进程并发地运行或 相互交换数据时,需要互斥。

• 互斥机构包含某种形式的读—修改—写存储周 期和排队。信号灯(semaphore)是互斥机构的 一种。每个信号灯有其队列,队列中的项是被 挂起来的进程。信号灯操作是不可分操作,利 用读—修改—写存储周期,测试和修改信号灯。 队列操作也应是不可分的。

• 阵列机的处理属于SIMD形式(单指令流 多数据流),它最适合作向量数组运算。 每个处理单元相当于一个向量数组元素 的运算,包括定点和浮点的多种运算操 作。对于是阵列机处理单元个数的倍数 的向量数组运算尤为合适。如PE=64,则 16,32,64,128,256,512···阵列向量 数组就很方便地使阵列机发挥最佳效能。

多cpu操作系统的工作原理

多cpu操作系统的工作原理多CPU操作系统,也称为多处理器操作系统,是一种能够同时管理和协调多个中央处理器(CPU)的操作系统。

它通过将计算任务分配给不同的处理器,以提高系统的整体性能和效率。

下面将介绍多CPU操作系统的工作原理。

在多CPU操作系统中,存在多个物理或逻辑的CPU核心。

这些核心可以是同一种类型的处理器,也可以是不同类型的处理器。

每个CPU核心都有自己的寄存器和执行单元,可以独立地执行指令。

多CPU操作系统利用并行处理的能力,将任务划分为多个子任务,并将它们分配给空闲的CPU核心进行处理。

这种任务分配和调度的过程可以通过多种方式实现,如轮转调度、优先级调度、时间片轮转等。

在任务分配过程中,操作系统需要考虑到各个任务之间的依赖关系和资源竞争。

例如,如果两个子任务之间存在数据共享和依赖关系,那么它们应该被分配给同一个CPU核心执行,以避免数据不一致性的问题。

此外,多CPU操作系统还需要实现进程间通信(IPC)机制,以便不同的CPU 核心之间能够共享信息和进行协作。

常用的IPC机制包括共享内存、消息传递、信号量等。

在多CPU操作系统中,还需要进行资源管理和调度。

操作系统需要监视CPU核心的使用情况,以便及时发现并处理负载的不平衡问题。

通过动态调整任务分配和调度策略,操作系统可以实现负载均衡,提高系统的整体性能。

总而言之,多CPU操作系统通过将任务分配给多个CPU核心并实现适当的任务调度和资源管理,实现了并行处理和负载均衡,从而提高了系统的性能和效率。

这种工作原理使得多CPU操作系统成为处理大规模计算任务和高性能需求的理想选择。

并行处理机和多处理机

(4) 产生和向所有处理单元广播公共的数 据; (5) 接收和处理PE、I/O操作以及B6700产 生的陷阱中断信号。 2、输入输出系统 IlliacIV的输入输出系统由磁盘文件系统 DFS、I/O分系统和一台B6700处理机组 成。 I/O分系统又由输入输出开关IOS、控制描 述字控制器CDC和输入输出缓冲存储器 BIOM三个部分组成。

7

8.2 多处理机结构和实例

两个或两个以上处理机(包括PU和 CU),通过高速互连网络连接起来,在统 一的操作系统管理下,实现指令以上级 (任务级、作业级)并行。 按照Flynn分类法,多处理机系统属于 MIMD计算机。 多处理机系统由多个独立的处理机组 成,每个处理机都能够独立执行自己的 程序。

并行性在很大程度上依赖于R/C比值, 其中:R代表程序执行时间,C代表通信开销。 通常:R/C比值小,并行性低。R/C比值大,并行性高 如果把作业分解成较大的块,就能得到较大的R/C值, 但是所得到的并行性比最大可能的并行性要小得多。 R/C比值是衡量任务粒度(Granularity)大小的尺度 在粗粒度(Coarsegrain)并行情况下,R/C比值比较 大,通信开销小 在细粒度(Finegrain)并行情况下,R/C比值比较小, 通信开销大 细粒度并行性需要的处理机多,粗粒度并行性需要的处 理机少。 细粒度并行性的基本原理是把一个程序尽可能地分解成 能并行执行的小任务。在极端情况下,一个小任务只完 成一个操作。

11

1.基本模型 1.基本模型

在两台处理机情况 每个任务的执行时间为R个单位时间 两个任务不在同一台处理机上时,通信开 销为C个单位时间 K个任务给一台处理机 M-K个任务给另一台处理机 总处理时间=Rmax(M-K,K)+C(M-K)K

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

量减少并行程序的执行时间。

2. 多处理机调度方式

确定性调度:在调度之前必须知道所有有关信息,例如每个任务的执行时间 和任务间的依赖关系,以便合理地把任务分派到处理机。 不确定性调度:根据任务运行的动态行为,将任务分配到特定的处理机上。

3. 调度性能评价

评价多处理机调度性能的参数有: 任务流时间 :完成任务所需要的时间

2.独立监督式

独立监督式中,每一个处理机均有各自的管理程序(核心)。

3.浮动监督式

每次只有一台处理机作为执行全面管理功能的“主处理机”,但根 据需要,“主处理机”是可浮动的,即从一台切换到另一台处理机。

多处理机系统控制

多处理机调度

1.什么是多处理机调度

将作业或任务分配给指定的处理机,并要求在指定的时间内完成。调度算 法的一般目标是:使用最少的处理机、在最短的时间内完成并行程序的执 行任务。在处理机器数目固定时,要改进处理机分配和进程调度算法,尽

I/O操作

Cache中的内容可能与由I/O子系统输入输出形成的存储 器对应部分的内容不同。

共享数据

不同处理器的Cache都保存有对应存储器单元的内容。

存储器的一致性

如果对某个数据项的任何读操作均可得到其最新写入的值,

则认为这个存储系统是一致的 需满足以下条件 ① 处理器P对X进行一次写之后又对X进行读,读和写之间没有

存储器

I/O 系统

多个处理器共享一个存储器 当处理器规模较小时,这种机器十分经济 支持对共享数据和私有数据的cache缓存 私有数据供一个单独的处理器使用,而共享数据供多个处 理器使用

共享数据进入cache ,产生一个新的问题

Cache一致性问题!

多处理机cache的一致性

产生cache不一致的原因

其它处理器对X进行写,则读的返回值总是写进的值。

②一个处理器对X进行写之后,另一处理器对X进行读,读和写 之间无其它写,则读X的返回值应为写进的值。 ③ 对同一单元的写是顺序化的,即任意两个处理器对同一单 元的两次写,从所有处理器看来顺序都应是相同的。

实现一致性的基本方案

(1) Cache一致性协议:对多个处理器维护一致性的协议 (2) 关键:跟踪记录共享数据块的状态 (3) 共享数据状态跟踪记录技术

多处理机系统结构

多处理机硬件结构——紧耦合和松耦合

1.紧耦合多处理机

紧耦合多处理机是通过共享主存来实现处理机间通信的, 其通信速率受限于主存的频宽。但是,由于各处理机与主存

经互连网络连接,系统中处理机数就受限于互连网络带宽及

多台处理机同时访问主存发生冲突的概率。

图 7.1 紧耦合多处理机的结构

带非对称I/O子系统的多处理机

第二种方法是在私有的地址空间进行通信。多个私有地址空 间在逻辑上是分散的,并且不能被远程处理器寻址,数据通 信通过显式地在处理器间传松消息来完成。如集群,就是使 用消息传递的一类系统。

多处理机系统死锁

死锁问题是由于各处理机为争夺全局范围内的资源而引发的。

传统的狭义多处理机系统是利用系统内的多台处理器并行执行用

处理器 +cache

处理器 +cache

处理器 +cache

处理器 +cache

节点通过网络互连。访问可以是

互 连 网 络

本地的,也可是远程的;

可以不支持cache一致性协议,

I/o 存储器 I/o

存储器

I/o

存储器

I/o

存储器

规定共享数据不进入cache,仅私

有数据才保存在cache中。

处理器 +cache 处理器 +cache 处理器 +cache 处理器 +cache

解决Cache一致性问题的关键:

寻找替代监听协议的一致性协议

目录协议

在每个结点增加目录存储器,用于存放目录 基于目录的Cache一致性及其实现 目录协议必须实现两种基本操作

处理读失效;处理对共享、干净块的写

目录必须跟踪记录每个存储块的状态

必须记录哪些块有该处理器的拷贝

多处理机操作系统

1.主从式

主从式操作系统由一台主处理机记录、控制其它从处理机的状态, 并分配任务给从处理机。

调度流时间 :调度中所有任务流的时间

平均流 : 平均流等于调度流之和除以最大有效时间单位 加速比 :用于度量系统的速度,等于各处理机忙时间之和除以并行工作 时间

吞吐率:单位时间内系统完成的任务数

多处理机间进程通讯

第一种方法是在共享的地址空间进行通信。物理上分开的存 储器能够作为逻辑上共享的地址空间进行寻址,利用地址空 间通过load和store操作隐式地传递数据;

采用冗余连接的非对称I/O子系统

2.松耦合多处理机

松耦合多处理机是通过消息传送系统连接的多处理机结 构。

机间互联形式

1. 总线形式 多个处理机、存贮器模块和外围设备通过接口与公用总线

相连,采用分时或多路转接技术传送。其中,单总线方式结构

简单、成本低, 系统上增减模块方便,但对总线的失效敏感。 而且,处理机数增加会增大访问总线冲突的概率而导致系统效 率急剧下降。虽然可以在处理机中设置局部存贮器和专用外围 设备来减少访问总线的冲突,但这种单总线形式也只适用于处 理机数较少的场合。IBM Stretch和UNIVAC Larg多处理机采用 的就是单总线方式。

目录

物理存储器中共享数据块的状态及相关信息均被保存 在一个称为目录的地方。

监听(snooping)

每个Cache除了包含物理存储器中块的数据拷贝之外, 也保存着各个块的共享状态信息。

2.分布式共享存储器 特点:

存储器分布于各节点中,所有

存储器 I/o 存储器 I/o 存储器 I/o 存储器 I/o

2. 环形互连形式

机间采用环形互连的多处理机

3. 交叉开关形式

图 7.7 交叉开关形式

交叉开关中结点开关的结构

存储器组织

1.集中式共享存储器 三个特点:

CPU0 CPU1 CPU2 CPU3

一级或 多级 cache

一级或 多级 cache

一级或 多级 cache

一级或 多级 cache

处理器数量不大——从而所有 处理器可共享一个集中式存储器, 处理器和存储器通过总线互连。 ������ 采用大容量Cache——可使采 用单一总线和单一存储器满足数 目不多处理器对存储器的要求。 ������ 每一处理器访问存储器的时 间是相等的