calibre_LVS入门

Calibre DRC和LVS验证总结材料

Calibre学习总结第一章 Calibre简述1.1 Calibre 简介Calibre 作为Mentor Graphics 公司出品的后端物理验证(Physical Verification)工具,它提供了最为有效的DRC/LVS/ERC 解决方案,特别适合超大规模IC电路的物理验证。

它支持平坦化(Flat mode )和层次化(Hierarchical mode)的验证,大大缩短了验证的过程;它高效可靠的性能已经被各大Foundry 认证,作为Tape Out 之前的验证标准。

它独有的RVE(Result ViewEnviroment)界面可以把验证错误反标到版图工具中去,而且良好的集成环境便于用户在版图和电路图之间轻松转换,大大提高了改错的效率。

xCalibre 具有版图寄生参数抽取的功能。

1.2手册在工作站下输入mgcdocs &命令,就可阅读Calibre的所有手册。

1.3几个常用的缩写命令1、SVRF---Standard Verification Rule Format(标准的检查文件)2、RVE---Results Viewing Environment(显示结果用的环境窗口)3、SVDB---Standard Verification Database (LVS results)4、DRC---Design Rule Checking5、LVS---Layout Versus Schematic6、ERC---Electrical Rule Checking第二章Calibre DRC2.1数据准备完成CalbireDRC需要的数据有版图数据和执行DRC检查的命令文件(Runset)。

版图数据支持GDSII、CIF、BINARY、ASCII 格式。

2.2流程图Runset Completed LayoutCalibre DRCASCII Report DRC Results DatabaseLocate Errors Using Calibre RVE and Layout Tool Correct Layout Errors2.3 DRC Runset File1 基本控制,原有DRACULA的file可以用drac_cvt sourcefile targetfile命令来转换。

Calibre LVS指令描述

Setting: Specify ERC results file path

Usually, we use ASCII format.

Calibre LVS command description

· 14 ·

ERC MAXIMUM RESULTS {number | ALL}

Setting: Specify a number

Setting: Default

It specifies Calibre whether to recognize logic gates from transistor level data. You can select a value according to your need.

Calibre LVS command description

Calibre LVS command description

· 20 ·

LVS BUILTIN DEVICE PIN SWAP {YES | NO}

Setting: NO

It specifies whether LVS should apply pin swappability rules in built-in devices.

Calibre LVS command description

· 3 ·

LVS options setting (cont’)

LVS REVERSE WL LVS SPICE PREFER PINS LVS SPICE SLASH IS SPACE LVS SPICE ALLOW FLOATING PINS LVS SPICE CONDITIONAL LDD LAYOUT CASE SOURCE CASE LVS COMPARE CASE LVS PROPERTY RESOLUTION MAXIMUM LVS FILTER UNUSED OPTION

Calibre LVS的使用方法

•

了重要的数据文件和子目录,并且在用

RVE反标及xCalibre

• 的数据;

进行寄生参数提取时需要用到该目录下

• TOPCELL.rep Calibre LVS Report File,所有 的错误信息均在该文件中,

•

查错过程主要就是基于此文件;

• TOPCELL.rep.ext Calibre LVS Extraction Report

Calibre LVS的使用方法

3.3 Calibre LVS的执行命令:

cd ~/check/calilvs (进入LVS的运一次LVS产生的数据目录,以免影响本次执行结果)

calibre –lvs -hier -spice ./svdb/TOPCELL.sp –hcell hcells -auto ../rule/CLVS.ru |tee TOPCELL.log

File;

• CLVS.ru Calibre LVS规则文件。

Calibre LVS is OK !

Calibre LVS Report File

Circuit Extraction Report File

Connectivity Errors Calibre LVS

Failed !

Calibre LVS Report File

Circuit Extraction Report File

(5) –hcell hcells表示额外得将hcells文件中指定的Layout和电路网表单元进行 比较并在最后的报告中给出相应的比较结果。hcells也可以用其它的文件名

• 3.4 Calibre LVS所用到和产生的文件列表及说明:

• svdb/

这是Calibre LVS在执行过程中

Calibre LVS 介绍

Calibre LVS 介绍本篇就讲解有关LVS方面的内容。

具体实例可以参照 ”dracula LVS介绍”中的说明。

一、具体操作:%drac_cvt %caliber –lvs | tee mlvs.logopen cell view “lvs_test”%calibre –rveLoad LVS result databasemodify layoutuse query tools to highlight errors (举例)*注:当然还有其他一些工具来帮助查找错误所在,点击就可以,不至于要想半天来判断错在source端还是drain 端等扼杀脑细胞的问题了。

有一大特点就是很人性化的点击,就到显示到相应的位置,无法是layout还是schematic或者是source net list。

二、相关文件内容1, netlist***** lvs_test NETLIST ******.BIPOLAR.GLOBAL VSS VDD************************************************************************************.SUBCKT lvs_test OUT INRI6 net2 IN 1kCI4 OUT VSS 0.2pMI1 VSS net2 OUT VSS PMI0 VDD net2 OUT VDD N.ENDS可以用 caliber –lv –cs 对netlist进行转换和语法分析。

*建议:subckt name最好与cell name一致。

2,由dracula 转换过来作了些小的修改,只是保证了语法没有错,并且能达到基本的要求为目的,所以大家可以对比上次 dracula 来看。

Caliber ERC 一般与 LVS 一起验证,要产生 LVS 可RVE 的database,需要加入 MASK SVDB DIRECTORY "svdb" QUERY 会产生 svdb目录,要产生ERC database 要使用 ERC SELECT CHECK 。

Calibre DRC、LVS的详细教程

//

rule_4a { @ res minimum enclosure of oxide is 7

enclosure oxide res < 7 }

// oxide 的内外边的间距 ,enclosure 具体的介绍见下一节

rule_4b { @ oxide minimum enclosure of res is 6

Begin Cell Definition Cell Name : VG, View Name : layout Rectangle - Layer : 7 Data Type : 0 BBOX : (5000,-10500) (16000,-8100) Rectangle - Layer : 7 Data Type : 0 BBOX : (5000,5900) (16000,8300) Rectangle - Layer : 1 Data Type : 0 BBOX : (5000,0) (16000,10200) End Cell Definition

T8.4 Internal operation 理解 Internal 指令的关键是 Internal 指令是 polygon 的内边(interior edge)的相对关系, 只有 interior edge 之间才能检查。T8.4 的左边是在同一个 polygon 的 internal 检查,请注意左 边凹进去的相对两边不作检查,这是因为这两边是 exterior edge。同一 layer 的 polygon 的

8.2 DRC Rule File

T8.2 DRC flow 如图 T8.2 所示,DRC 的输入有两项,一个是 layout,就是手工或 APR 生成的版图,一 般是 GDSII 格式。另一个是 Rule File,Rule File 告诉 DRC 工具怎样做 DRC,这个文件十分 重要,一般,由流片厂家提供,或者由 designer 根据流片厂家提供的版图几何规范自己写。 Calibre 读入 GDS(版图)和 Rule File,进行处理,输出结果,输出结果是 calibre 自己定义 的格式,designer 可以通过一个 Viewer 来看,一般用 cadence 的 virtuoso 来分析输出结果和 修改版图。

calibre_LVS入门

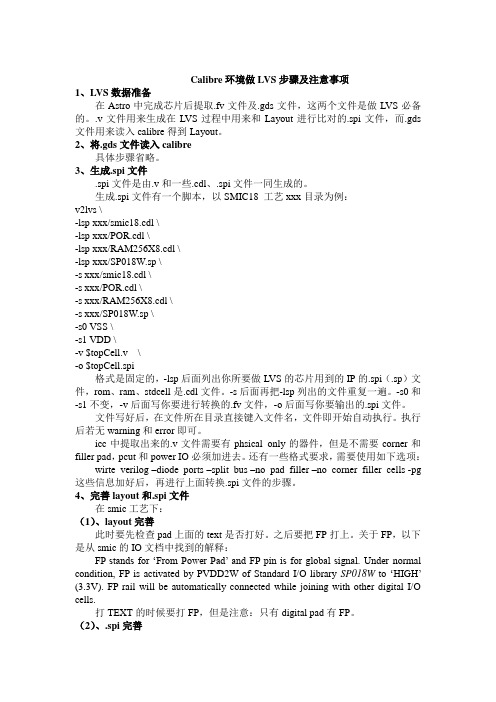

Calibre环境做LVS步骤及注意事项1、LVS数据准备在Astro中完成芯片后提取.fv文件及.gds文件,这两个文件是做LVS必备的。

.v文件用来生成在LVS过程中用来和Layout进行比对的.spi文件,而.gds 文件用来读入calibre得到Layout。

2、将.gds文件读入calibre具体步骤省略。

3、生成.spi文件.spi文件是由.v和一些.cdl、.spi文件一同生成的。

生成.spi文件有一个脚本,以SMIC18 工艺xxx目录为例:v2lvs \-lsp xxx/smic18.cdl \-lsp xxx/POR.cdl \-lsp xxx/RAM256X8.cdl \-lsp xxx/SP018W.sp \-s xxx/smic18.cdl \-s xxx/POR.cdl \-s xxx/RAM256X8.cdl \-s xxx/SP018W.sp \-s0 VSS \-s1 VDD \-v $topCell.v \-o $topCell.spi格式是固定的,-lsp后面列出你所要做LVS的芯片用到的IP的.spi(.sp)文件,rom、ram、stdcell是.cdl文件。

-s后面再把-lsp列出的文件重复一遍。

-s0和-s1不变,-v后面写你要进行转换的.fv文件,-o后面写你要输出的.spi文件。

文件写好后,在文件所在目录直接键入文件名,文件即开始自动执行。

执行后若无warning和error即可。

icc中提取出来的.v文件需要有phsical only的器件,但是不需要corner和filler pad,pcut和power IO必须加进去。

还有一些格式要求,需要使用如下选项:wirte_verilog –diode_ports –split_bus –no_pad_filler –no_corner_filler_cells -pg 这些信息加好后,再进行上面转换.spi文件的步骤。

Calibre 中文教程

Lab-4.Calibre –DRC與LVSI•目的:實習六是介紹一個大部分業界所使用的一套佈局驗證的軟體―Calibre(為Mentor公司之產品),Calibre是被世界上大多數的IC設計公司做為sign-off的憑據,適合做大型電路的驗證。

Calibre和Dracula、Diva有許多不同之處。

Calibre是一套類似Diva的驗證軟體,但其嚴謹度與考靠性遠優於Diva,這也是大家為何要使用Dracula的原因,但Dracula的操作不易,且無法做on-line的驗證。

但Calibre改進了這些缺點,不但操作簡易,更可搭配Virtuoso或其他layout軟體做線上的驗證,由於Calibre的已被大多數的公司所採用,因此CIC也將轉向支援Calibre的技術而漸漸取代Dracula。

本實習的目的是要將前一實習的電路,經過Calibre的佈局驗證後,以便能將此Layout送去製造。

而本實習將延續實習四的Layout為實例,藉此介紹整個Dracula的操作流程。

II•DRC(Design Rule Check):1•建立子目錄、拷貝calibre_035.drc檔及撰寫DRC的主要檔案:<i>因為作DRC佈局驗證時會造出非常多檔案,因此在此強烈建議建立一個屬於此Layout作DRC時之新目錄夾,也就是說在你的根目錄下鍵入mkdir 0.35然後再進入0.35的資料夾內,即鍵入cd0.35,再鍵入mkdirdrcnand3,建立一個名為drcnand3的子目錄 。

..<ii>先進入/avanti/Lab610/avanti/Lab/610/test/lab/drc/目錄下再利用filemgr &或拷貝指令cp ,將calibre_035.drc 拷貝至你的工作目錄底下。

<iii>為配合Layout ,因此在作DRC 驗證時必須利用編輯軟體(ex Vi 、textedit….),編輯下面的檔案並存為drc_rules的檔。

CALIBRE使用流程

Running Calibre for GUI在(terminal)command line 執行hpmenu,選擇b再執行 calibre -gui可開啟Calibre視窗畫面DRC:Design Rule checkLVS:Layout vs. SchematicPEX:Parasitic Extraction using XCalibreRVE:Results Viewing Environment建立目錄Full_CustomCadence lakerCalibrehspicecdslib techfile cdslib techfile inv 其他 techfilemylib *.tf *.dsp mylib *.tf *.dspinv 其他 inv 其他PS:此目錄結構並不是唯一的,僅供參考Design Rule Check檢查佈局設計與製程規則的一致性基本設計規則包含各層之Width,Spacing及不同層間之Spacing、enclosure等關後Design rule 的規定是基於process variation Equipment limitation,circuit reliability等之考量在特殊的設計需求下,Design rule允許部份的彈性。

但設計者需掌握Rule violation對電路的影響。

Calibre DRC使用流程圖Running Calibre – DRC (1/4)將路徑指向Calibre 之DRC command file ,此檔可到/disk/standard/Full_custom 底下copy 。

以TSMC 0.35 2P4M 為例,檔案為D35M24P5.22b指定 run Calibre DRC 的目錄,其所產生之相關檔案(Output),將存放在此目錄Running Calibre – DRC (2/4)可指定 Hierarchical或Flat,Calibre CB是配合Mentor軟體電路佈局工具用的,目前請先選取Hierarchical或Flat即可。

Calibre DRC和LVS验证总结

Calibre学习总结第一章Calibre简述1. 1 Calibre 简介Calibre 作为Mentor Graphics 公司出品的后端物理验证(Physical Verification)工具,它提供了最为有效的DRC/LVS/ERC 解决方案,特别适合超大规模IC电路的物理验证。

它支持平坦化(Flat mode )和层次化(Hierarchical mode)的验证,大大缩短了验证的过程;它高效可靠的性能已经被各大Foundry 认证,作为Tape Out 之前的验证标准。

它独有的RVE(Result ViewEnviroment)界面可以把验证错误反标到版图工具中去,而且良好的集成环境便于用户在版图和电路图之间轻松转换,大大提高了改错的效率。

xCalibre 具有版图寄生参数抽取的功能。

1.2手册在工作站下输入mgcdocs &命令,就可阅读Calibre的所有手册。

1.3几个常用的缩写命令1、SVRF---Standard Verification Rule Format(标准的检查文件)2、RVE---Results Viewing Environment(显示结果用的环境窗口)3、SVDB---Standard Verification Database (LVS results)4、DRC---Design Rule Checking5、LVS---Layout Versus Schematic6、ERC---Electrical Rule Checking第二章Calibre DRC2.1数据准备完成CalbireDRC需要的数据有版图数据和执行DRC检查的命令文件(Runset)。

版图数据支持GDSII、CIF、BINARY、ASCII 格式。

2.2流程图Runset Completed LayoutCalibre DRCASCII Report DRC Results DatabaseLocate Errors Using Calibre RVE and Layout Tool Correct Layout Errors2.3 DRC Runset File1 基本控制,原有DRACULA的file可以用drac_cvt sourcefile targetfile命令来转换。

CalibreDRC和LVS验证归纳

CalibreDRC和LVS验证归纳Calibre学习总结第⼀章Calibre简述1. 1 Calibre 简介Calibre 作为Mentor Graphics 公司出品的后端物理验证(Physical Verification)⼯具,它提供了最为有效的DRC/LVS/ERC 解决⽅案,特别适合超⼤规模IC电路的物理验证。

它⽀持平坦化(Flat mode )和层次化(Hierarchical mode)的验证,⼤⼤缩短了验证的过程;它⾼效可靠的性能已经被各⼤Foundry 认证,作为Tape Out 之前的验证标准。

它独有的RVE(Result ViewEnviroment)界⾯可以把验证错误反标到版图⼯具中去,⽽且良好的集成环境便于⽤户在版图和电路图之间轻松转换,⼤⼤提⾼了改错的效率。

xCalibre 具有版图寄⽣参数抽取的功能。

1.2⼿册在⼯作站下输⼊mgcdocs &命令,就可阅读Calibre的所有⼿册。

1.3⼏个常⽤的缩写命令1、SVRF---Standard Verification Rule Format(标准的检查⽂件)2、RVE---Results Viewing Environment(显⽰结果⽤的环境窗⼝)3、SVDB---Standard Verification Database (LVS results)4、DRC---Design Rule Checking5、LVS---Layout Versus Schematic6、ERC---Electrical Rule Checking第⼆章Calibre DRC 2.1数据准备完成CalbireDRC 需要的数据有版图数据和执⾏DRC 检查的命令⽂件(Runset )。

版图数据⽀持GDSII 、CIF 、BINARY 、ASCII 格式。

2.2流程图2.3 DRC Runset File1 基本控制,原有DRACULA 的file 可以⽤drac_cvt sourcefile targetfile 命令来转换。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Calibre环境做LVS步骤及注意事项

1、LVS数据准备

在Astro中完成芯片后提取.fv文件及.gds文件,这两个文件是做LVS必备的。

.v文件用来生成在LVS过程中用来和Layout进行比对的.spi文件,而.gds 文件用来读入calibre得到Layout。

2、将.gds文件读入calibre

具体步骤省略。

3、生成.spi文件

.spi文件是由.v和一些.cdl、.spi文件一同生成的。

生成.spi文件有一个脚本,以SMIC18 工艺xxx目录为例:

v2lvs \

-lsp xxx/smic18.cdl \

-lsp xxx/POR.cdl \

-lsp xxx/RAM256X8.cdl \

-lsp xxx/SP018W.sp \

-s xxx/smic18.cdl \

-s xxx/POR.cdl \

-s xxx/RAM256X8.cdl \

-s xxx/SP018W.sp \

-s0 VSS \

-s1 VDD \

-v $topCell.v \

-o $topCell.spi

格式是固定的,-lsp后面列出你所要做LVS的芯片用到的IP的.spi(.sp)文件,rom、ram、stdcell是.cdl文件。

-s后面再把-lsp列出的文件重复一遍。

-s0和-s1不变,-v后面写你要进行转换的.fv文件,-o后面写你要输出的.spi文件。

文件写好后,在文件所在目录直接键入文件名,文件即开始自动执行。

执行后若无warning和error即可。

icc中提取出来的.v文件需要有phsical only的器件,但是不需要corner和filler pad,pcut和power IO必须加进去。

还有一些格式要求,需要使用如下选项:wirte_verilog –diode_ports –split_bus –no_pad_filler –no_corner_filler_cells -pg 这些信息加好后,再进行上面转换.spi文件的步骤。

4、完善layout和.spi文件

在smic工艺下:

(1)、layout完善

此时要先检查pad上面的text是否打好。

之后要把FP打上。

关于FP,以下是从smic的IO文档中找到的解释:

FP stands for ‘From Power Pad’ and FP pin is for global signal. Under normal condition, FP is activated by PVDD2W of Standard I/O library SP018W to ‘HIGH’ (3.3V). FP rail will be automatically connected while joining with other digital I/O cells.

打TEXT的时候要打FP,但是注意:只有digital pad有FP。

(2)、.spi完善

在.spi文件中要加入pcut的连接关系,即VSS1=…,VSS2=…。

VSS1和VSS2是pcut的port名字,…处你要写他们和什么相连。

另外,一些打了字的pad也要写清楚它的连接关系,如VSSD=VSSD_pad,等号前面是pad出的port,等号后面写pad上打的text。

另外,在.spi文件中的出现的变量名,要写在.GLOBAL后面,否则LVS的时候会报错。

如果有连接关系要注明,则在.spi文件后面写*.CONNECT后面写明两个要连接的名字就可以了。

5、进行LVS

所有准备工作都做完了,开始LVS。

启动calibre,选nmLVS,出现LVS界面。

选左边一栏的Rules,在Calibre Rules File中填入LVS的rule。

一般我们在做LVS的时候,会先把rom,ram,analog 等IP部分box起来不查,先让其他部分的LVS通过了,再查整体的LVS。

因此这个rule可以自己加一些box,格式是LVS BOX instance name。

在左边一栏中选Inputs,Layout一栏不动,选Netlist,在Files处填入你修改好了的.spi文件。

之后在上面一条菜单中选Setup>LVS Options,选Connect中的Connect nets with colon (:)。

选好后,点左侧的Run LVS,则LVS过程就开始了。

运行完后,如果没有问题,则你会看到绿色的笑脸,如果有问题,则要进行分析,修改.spi或者layout来通过LVS。

补充资料:

Useful Abbreviations

SVRF——Standard Verification Rule Format

Mentor Rule

RVE——Results Viewing Environment 显示环境

SVDB——Standard Verification Rule Database (LVS results)

在LVS rule中写上这句话,LVS会产生一个SVDB的文件夹存放一些中间结果文件。

ERC——Electrical Rule Verification

PEX——Parasitic Ectraction

MDP——Mask Data Preparation 是foundary做的mask的ORC检查。

(ORC:optical rules checking 光学规则校验)

TVF——Tcl Verification Format 65nm以下的rule file格式,SVRF很难cover所有的corner所以有TVF

Connect nets with colon (:) 虚拟连接,例如A:1和A:2将被认为是一条net

有时候smic18工艺中,ram,rom的LVS netlist文件.cdl是由dataprepare生成的,但是要把文件中N,P后面加上18变成N18和P18(必须保证stdcell和其rule的命名相匹配才可以)还有要把文件中DN改为NDIO18。

在.v转换成.spi文件的过程中,会在instance前面加X。

当有IP Merge时,一些IP的PIN、PORT都要当作BOX注释掉,否则在LVS中会报错。