TimeQuest 使用步骤

TimeQuest实例:约束生成时钟

TimeQuest实例: 约束生成时钟采用 Synopsys 设计约束 (SDC) 命令 create_generated_clock ,您可以建立任意数量以及任意深度的生成时钟。

这在以下情况时非常有用 ( 参见图 1 和图 2) 。

在图 1 的简单电路中,寄存器 div2reg 输出需要一个生成时钟。

图1.2 分频生成时钟下面的 SDC 命令对上面电路的时钟进行约束。

#Constrain the base clockcreate_clock -add -period 10.000 \-waveform { 0.000 5.000 } \-name clock_name \[get_ports clock]#Constrain the divide by 2 register clockcreate_generated_clock -add -source clock \-name div2clock \-divide_by 2 \-master_clock clock_name \[get_pins div2reg|regout]下载电路实例create_generated_clock_ex1.qar 。

在图2的简单电路中,寄存器 div2reg 输出需要一个生成时钟。

图2. PLL生成时钟下面的 SDC 命令对上面电路的时钟进行约束。

#Constrain the base clockcreate_clock -add -period 10.000 \-waveform { 0.000 5.000 } \-name clock_name \[get_ports clock]#Constrain the output clock clockcreate_generated_clock -add -source PLL_inst|INCLK[0] \ -name PLL_inst|CLK[1] \-multiply_by 2 \-master_clock clock_name \[get_pins PLL_inst|CLK[1]]下载电路实例create_generated_clock_pll.qar。

timegetsystemtime用法

时间获取函数timegetsystemtime是Windows API中的一个函数,它用于获取当前系统的时间。

这个函数返回的时间是以毫秒为单位的整数值,表示自系统启动以来经过的毫秒数。

在本文中,我将深入探讨timegetsystemtime的用法,主要包括其功能、调用方法以及相关注意事项。

1. timegetsystemtime的功能timegetsystemtime函数是一个非常有用的时间获取函数,它可以帮助我们获取系统的当前时间。

由于返回的是以毫秒为单位的时间值,因此可以用于各种时间相关的应用和计算,比如定时操作、时间间隔计算等。

2. timegetsystemtime的调用方法要使用timegetsystemtime函数,首先需要包含Windows.h头文件,然后就可以直接调用这个函数。

它的原型定义如下:```cvoid timegetsystemtime(LPSYSTEMTIME lpSystemTime)```在调用这个函数时,需要传入一个SYSTEMTIME结构体指针,用于存储获取到的系统时间信息。

这个结构体包括年、月、日、时、分、秒、毫秒等成员,可以详细描述一个时间点的信息。

调用示例:SYSTEMTIME st;timegetsystemtime(&st);```通过这种调用方法,就可以获取到当前系统的时间,并存储在st结构体中。

3. 注意事项在使用timegetsystemtime函数时,需要注意一些问题。

由于返回的时间是一个以毫秒为单位的整数值,因此可能会导致溢出问题。

在长时间运行的系统中,这个值可能会变得非常大,导致溢出。

在使用这个时间值时,需要进行适当的范围判断和处理。

timegetsystemtime返回的时间值是从系统启动开始计算的,因此无法直接表示一个具体的日历时间。

如果需要获取当前的日历时间,可以结合其他函数来进行转换和处理。

4. 个人观点和理解我个人认为,timegetsystemtime函数是一个非常方便实用的系统时间获取函数。

TimeQuest就一定要搞定 完整版

一、为什么一定要搞定为什么一定要搞定时序分析在ASIC设计中的重要性毋须多说(我也不甚了解)。

在FPGA设计中,很少进行细致全面的时序约束和分析,Fmax是最常见也往往是一个设计唯一的约束。

这一方面是由FPGA的特殊结构决定的,另一方面也是由于缺乏好用的工具造成的。

好的时序约束可以指导布局布线工具进行权衡,获得最优的器件性能,使设计代码最大可能的反映设计者的设计意图。

花些功夫在静态时序分析上既可以保证设计质量,也可以促使设计者再认识自己的代码。

这后一点,对于我们这些逻辑设计初学者来说,尤为重要。

从门级(在Altera的FPGA 器件中是LE级)再认识自己的代码,可以更深入地体会语言的特点,也可以更深入地理解综合工具对语言的处理,对于设计能力的提高帮助很大。

TimeQuest是Altera在6.0版的软件中加入的具备ASIC设计风格的静态时序分析(STA)工具。

通过初步试用和观看网络教程,我感觉TimeQuest确实比Timng Analyzer 功能强大一些,而且使用界面比较友好,易于进行深入的时序约束和结果分析。

TimeQuest采用Synopsys Design Constraints(SDC)文件格式作为时序约束输入,不同于Timing Analyzer采用的Quartus Settings File(QSF)约束文件。

这正是TimeQuest 的优点:采用行业通用的约束语言而不是专有语言,有利于设计约束从FPGA向ASIC设计流程迁移;有利于创建更细致深入的约束条件。

二、时序分析基本概念时序分析基本概念以下内容译自Quartus II Version 10.0 Handbook, Volume 3:Verification的SectionII 7.3:Timing Analysis Overview部分。

TimeQuest需要读入布局布线后的网表才能进行时序分析。

读入的网表是由以下一系列的基本单元构成的:1. Cells:Altera器件中的基本结构单元(例如,查找表、寄存器、IO单元、PLL、存储器块等)。

Quartus II 11[1].0安装教程

![Quartus II 11[1].0安装教程](https://img.taocdn.com/s3/m/418b861255270722192ef791.png)

创造平台——Quartus II 11.0 安装指南一、Altera Quartus II 11.0套件介绍所谓巧妇难为无米之炊,再强的软硬件功底,再多的思维创造力,没有软件的平台,也只是徒劳。

因此,一切创造的平台——Quartus II 软件安装,由零开启的世界,便从此开始。

自从Bingo 2009年开始接触FPGA,Quartus II 版本的软件从n年前的5.1版本到今天的最新发布的11.0,都使用过;当然对于软件核心构架而言,万变不离其宗。

虽然多多少少有点bug,但这10多个版本发展到了现在,能看到Altera一直在努力,致力于更完美的用户界面,更快的综合速度的软件开发。

虽然很多老的工程师不介意积极更新软件,但一次一次的视觉冲击,版本的更新,承受不住古老,使用11.0从某种意义上讲,还是有很大的好处的。

本书中以Quartus II 11.0 软件的安装为例,作为安装指南。

此外,关于Quartus II 10.0 以前版本,安装都大同小异,Bingo曾经写过“Quartus II 9.1的安装指南.pdf”,下载地址为/lib/detail.aspx?id=86239,或者在线浏览网页:/detail/9878.html/crazybingo/archive/2010/05/14/1735341.html如有需要,请自行下载。

对于Quartus II 11.0 ,最基本的套件包含以下三个不部分:(1)Quartus II 11.0 for windows软件(2)Quartus II 11.0 Devices for windows 硬件库(3)Altera-Modelsim for windows第三方仿真器二、Quartus II 11.0 套件下载1.Quartus II 11.0套件下载Quartus II 11.0 与之前的软件有些不同,有以下几个不同的地方:(1)Quartus II 9.1之前的软件自带仿真组件,而之后软件不再包含此组件,因此必须要仿真安装Modelsim。

TimeQuest使用教程(中文版)

骏龙科技(西安办事处)

Vincent Song

Q2 2008

© 2008 Cytech Technology Ltd., Co

TimeQuest使用教程

简介 使用步骤 时序分析中的要点 设计实例 常见时序优化方法

© 2008 Cytech Technology Ltd., Co

加入任何新的约束后,需要更新时序网表 执行

Update_timing_netlist的tcl命令

Update Timing Netlist (任务窗或者Netlist菜单下)

© 2008 Cytech Technology Ltd., Co

22

5) 生成时序报告

验证时序要求,找到违规 (Violated) 检查全约束的设计,或者 忽略时序约束 使用控制窗输入tcl命令、 任务窗双击所需报告或者 Reports菜单下

高级时序要求----TimeQuest 提供全脚本功能,建立约束,生成报告,管理时

序分析流程。TimeQuest支持高级报告,并且能够建立定制报告。

© 2008 Cytech Technology Ltd., Co

4

TimeQuest软件及器件支持

QuartusII从6.0版本开始支持TimeQuest时序分析器

要保证setup时序满足slow model 要保证hold时序满足fast model 源同步接口设计中的要点

第三种模式 (slow, 0 º C)目前只有Stratix III和CycloneIII支持

© 2008 Cytech Technology Ltd., Co

Quartus_II_时钟约束概念

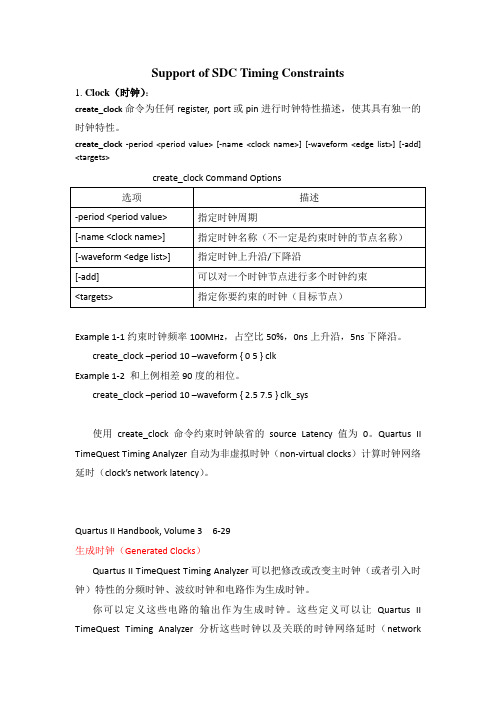

Support of SDC Timing Constraints1. Clock(时钟):create_clock命令为任何register, port或pin进行时钟特性描述,使其具有独一的时钟特性。

create_clock-period <period value> [-name <clock name>] [-waveform <edge list>] [-add] <targets>create_clock Command OptionsExample 1-1约束时钟频率100MHz,占空比50%,0ns上升沿,5ns下降沿。

create_clock –period 10 –waveform { 0 5 } clkExample 1-2 和上例相差90度的相位。

create_clock –period 10 –waveform { 2.5 7.5 } clk_sys使用create_clock命令约束时钟缺省的source Latency值为0。

Quartus IITimeQuest Timing Analyzer自动为非虚拟时钟(non-virtual clocks)计算时钟网络延时(clock’s network latency)。

Quartus II Handbook, Volume 3 6-29生成时钟(Generated Clocks)Quartus II TimeQuest Timing Analyzer可以把修改或改变主时钟(或者引入时钟)特性的分频时钟、波纹时钟和电路作为生成时钟。

你可以定义这些电路的输出作为生成时钟。

这些定义可以让Quartus II TimeQuest Timing Analyzer分析这些时钟以及关联的时钟网络延时(networklatency)。

使用create_generated_clock命令定义生成时钟。

UnconstrainedPaths解决办法

UnconstrainedPaths解决办法⽤TimeQuest对DAC7512控制器进⾏时序分析在对某个对象下时序约束的时候,⾸先要能正确识别它,TimeQuest 会对设计中各组成部分根据属性进⾏归类,我们在下时序约束的时候,可以通过命令查找对应类别的某个对象。

TimeQuest对设计中各组成部分的归类主要有cells,pins,nets和ports ⼏种。

寄存器,门电路等为cells;设计的输⼊输出端⼝为ports;寄存器,门电路等的输⼊输出引脚为pins;ports和pins之间的连线为nets。

具体可以参照下图(此图出⾃Altera Time Quest的使⽤说明)。

下⾯我们按照本⽂第⼆部分⽤TimeQuest做时序分析的基本操作流程所描述的流程对DAC7512控制器进⾏时序分析。

建⽴和预编译项⽬的部分相对简单,涉及到的也只是QuartusII的⼀些基本操作,这⾥我们就不再做具体的叙述。

主要介绍如何向项⽬中添加时序约束和如何进⾏时序验证。

⾸先建⽴⼀个名称与项⽬top层名字⼀致的sdc⽂件,然后按照下⾯的步骤添加时序约束。

1. 创建时钟添加时序约束的第⼀步就是创建时钟。

为了确保STA结果的准确性,必须定义设计中所有的时钟,并指定时钟所有相关参数。

TimeQuest⽀持下⾯的时钟类型:a) 基准时钟(Base clocks)b) 虚拟时钟(Virtual clocks)c) 多频率时钟(Multifrequency clocks)d) ⽣成时钟(Generated clocks)我们在添加时序约束的时候,⾸先创建时钟的原因是后⾯其它的时序约束都要参考相关的时钟的。

基准时钟:基准时钟是输⼊到FPGA中的原始输⼊时钟。

与PLLs输出的时钟不同,基准时钟⼀般是由⽚外晶振产⽣的。

定义基准时钟的原因是其他⽣成时钟和时序约束通常都以基准时钟为参照。

很明显,在DAC7512控制器中,CLK_IN是基准时钟。

TimeQuest快速入门

TimeQuest快速入门简介本教程介绍用TimeQuest Analyzer进行时序约束和静态时序分析的必要步骤。

所用示例文件在\qdesigns\fir_filter文件夹下。

TimeQuest约束步骤下面的步骤描述了用TimeQuest对设计进行时序约束的步骤,每一步操作包含GUI和Command-line的操作方法。

第1步:在QuartusII中打开&建立工程启动QuartusII软件,在\qdesigns\fir_filter文件夹下打开工程compile_fir_filter.qpf。

第2步:设置TimeQuest Analyzer默认状态下,QuartusII使用Classic Timing Analyzer作为默认的时序分析工具。

需要在QuatusII中进行如下设置将TimeQuest Analyzer设为当前工程的时序分析器。

在【Assignment】菜单下单击【Settings】,在【Category】列表中展开【Timing Analysis Processing】,选择【Use TimeQuest Analyzer during compilation】,然后点击【OK】即可。

第3步:进行初始的编译在将时序约束应用到设计之前,需要为TimeQuest创建初始的数据。

初始数据是通过post-map结果产生的。

步骤如下:在【Processing】菜单栏下,选择【Start】/【Start Analysis&Synthesis】。

通过运行【Analysis&Synthesis】产生post-map数据。

还可以用post-fit网表来产生初始数据。

但是创建post-map数据所用时间更少,而且post-map数据对本设计示例工程来说已经够用。

第4步:启动TimeQuest Analyzer为了创建并验证时序约束,需要启动TimeQuest Analyzer。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Timequest timing analyzer使用方法

步骤1:执行初始编译

在应用时序约束设计之前,创建一个初始数据库:post-map。

表 1-1. 执行初始编译(1)

3.也可为初始数据库创建一个post-fit网表。

不过,创建一个post-map网表耗时较少。

图1 Analysis & Synthesis

当您直接从Quartus II软件中运行TimeQuest Timing Analyzer时,当前工程将会自动打开。

如果使用GUI,那么当出现下面的消息时,请选择No:

"No SDC files were found in the Quartus Settings File and filtref.sdc doesn't exist. Would you like to generate an SDC file from the Quartus Settings File?"

图2TimeQuest Timing Analyzer

步骤3:创建一个Post-map时序网表

在指定时序要求之前,请创建一个时序网表。

表3-1. 创建一个Post-Map时序网表

注意:不要在Tasks面板中使用Create Timing Netlist命令来创建一个post-map时序网表。

默认情况下,Create Timing Netlist创建一个post-fit数据库。

图3 Create Timing Netlist

图4 Input netlist

图5waiting

图7Create clock

图8设置参数

图9指定时钟

图10 Create clock设置完毕

图11Drive PLL clocks

图12Update Timing Netlist

步骤6:保存到SDC文件

在为设计指定时钟约束并更新时序网表后,您可以通过表6-1中的程序来选择创建SDC 文件。

通过TimeQuest Timing Analyzer GUI或者在控制台(console)中指定的约束不会自动保存。

因此,Altera建议单独保存利用文本编辑器可以手动编辑的一个golden SDC 文件。

这使您能够根据自身的规范输入注释并组织文件。

如下图:

而不是从TimeQuest GUI的Constraints下拉菜单输入约束:

图14时钟报告

图15时钟传输报告(Clock Transfers Report)

完成编译后,TimeQuest Timing Analyzer在Compilation Report中生成时钟建立和时钟保持的检查总结报告。

步骤10:在TimeQuest中验证时序

要获得指定路径中详细的时序分析数据,请查看TimeQuest Timing Analyzer中的时序分析结果。

完全执行布线布局功能(place-and-route)后,运行"步骤2:运行TimeQuest Timing Analyzer"中所介绍的TimeQuest Timing Analyzer,生成一个post-fit时序网表,通过表10-1中的程序,读取SDC文件并更新时序网表来生成关于最新编译的报告。

#1. Summary报告:

表 10-1. 生成关于Latest Compilation的报告

Summary (Setup)报告

clkx2时钟没有出现在Summary (Setup)报告中,这是因为clk和clkx2之间所有的时钟路径已经声明是伪路径。

此外,fir_filter设计不包含任何寄存器到寄存器的路径,其中目的寄存器路径由clkx2来驱动。

Summary (Setup)报告中的Slack列表明clk能满足约束,并有11.588 ns的余量。

End Point TNS列是指定时钟域中所有的总负裕量(TNS)的总和。

使用这个值来测量指定时钟域中失败路径的总数。

#3. Clock Hold报告:

生成Summary (Setup)报告后,通过表 2-21中的程序,生成一个时钟保持检查总结。

表 10-3. 生成Summary (Hold) Report

图16Summary (Hold)报告

Summary (Hold)报告表明clk时钟节点符合时序约束,并有0.661 ns的余量。

#4. Unconstrained Paths报告:

在执行全编译之前,通过表10-4中的程序指定所有的时序约束和例外。

这样可以确保Fitter 优化设计中的关键路径。

您可以使用Report Unconstrained Paths命令来验证已经约束

fir_filter设计中的所有路径。

表 10-4. 指定时序约束和例外

图17Unconstrained Paths总结报告

#5. Set_input_delay / set_output_delay设置:

Unconstrained Paths总结报告表明有大量的未约束路径,并详细介绍了这些路径的类型。

要充分约束此设计,利用由TimeQuest Timing Analyzer所提供的整套SDC约束。

要充分约束fir_filter设计,约束所有的输入和输出端口。

使用Set Input Delay和Set Output Delay 对话框,或set_input_delay和set_output_delay约束来指定输入和输出延迟值。

由于附加约束应用于设计,通过文本编辑器(例如:inout_delay.sdc)创建仅包含输入和输出约束的额外SDC。

添加表10-5所示的输入和输出延迟分配到"步骤8:保存约束到SDC文件"创建的新SDC中。

表10-5. 输入和输出延迟分配

使用Tasks面板中的Report Top Failing Paths命令来生成一个报告,该报告详细介绍了设计中的最差的失败路径。

也可以通过菜单设置。