真随机数发生器芯片的设计

智能卡攻击技术浅析与高安全性芯片设计

智能卡攻击技术浅析与高安全性芯片设计【摘要】随着智能卡应用越来越广泛,安全威胁成为了急需解决的问题。

通过分析相应的需求,设计并实现了一种高安全性的智能卡芯片。

集成了8位微处理器内核,真随机数发生器,DES/3DES、SF33加解密协处理器,存储器访问控制机制和专用的硬件安全电路来保证智能卡的安全性。

【关键词】智能卡;攻击技术;安全机制Smartcard Attack Techniques Analysis and High Security Chip Desig【Abstract】As smartcard using more and more widely,security threats become a serious problem,this paper analysis security threats of smart card, design and implement a high-security smart card. Integrated 8-bit microprocessor, true random number generator, DES/3DES, SF33 encryption co-processor, memory access control mechanisms and dedicated hardware security circuit to ensure the security of smartcard.【Key words】Smartcard; Attack techniques; Security logic0引言随着微电子技术、计算机通信和信息安全技术的进步,智能卡技术得到了进一步的发展。

随着智能卡应用范围的不断扩大,针对智能卡的各种各样的攻击性的犯罪现象已经出现,而且有增长的趋势。

因此,智能卡的安全性和保密性显得日益重要。

本文实现了一种高安全性的智能卡芯片,且其面积、功耗、速度均在一个可接受的合理范围之内。

基于 FPGA 一种真随机数生成器的设计和实现

基于 FPGA 一种真随机数生成器的设计和实现吴飞;李艳萍【摘要】Aiming at the application of random number in secure communication , we design and implement a new FPGA-based true random number generator ( TRNG) in this paper .It takes the metastability of RS flip-flop as the random source to reduce the phase shift of clock signal and minimises the process differences of internal components so as to guarantee the randomness of output sequence .The outputs of multi-triggers are conducted the XOR operations and are added the post-processing module for enhancing the quality of random sequences and increasing the entropy per bit .This design has been implemented on Xilinx Spartan 3 XC3S400 platform, the random sequence generated can pass the NIST test , and all the indexes meet the design requirements .The true random number generator consists of common logic unites only, it can be quickly transplanted into ASIC design and shorten the development cycle .%针对随机数在保密通信中的应用,设计并实现一种基于FPGA的真随机数生成器,将RS触发器的亚稳态作为随机源,减小时钟信号的相位偏移,最小化内部元件的工艺差异,从而保证输出序列的随机性,对多个触发器的输出进行异或操作并且加入后处理模块来提高随机序列的质量和增加每比特的熵。

一位硬件随机数发生器的设计与仿真

一位硬件随机数发生器的设计与仿真周新淳【摘要】This paper presents a random number generating circuit , It can generate a random decimal number.The circuit is composed of a switching circuit, a pulse generating circuit, a counting circuit and a display e common chip design , The design has the characteristics of convenience , reliability and low cost. And using simulation software for data statistics. The computer simulation results show that the design implements generator of random number from 0 to 9.%文中设计了一种随机数发生电路,可以生成一位十进制随机数,电路分为开关电路、脉冲产生电路、计数电路和显示电路,采用常用芯片设计,产品方便可靠,成本低廉.并利用仿真软件进行数据统计,仿真结果表明该电路可以有效实现随机产生数码0到9的功能.【期刊名称】《电子设计工程》【年(卷),期】2017(025)006【总页数】4页(P19-22)【关键词】随机数;硬件电路;Multisim;仿真【作者】周新淳【作者单位】宝鸡文理学院陕西宝鸡 721016【正文语种】中文【中图分类】TN709现代生活对随机数的依赖越来越多,比如彩票摇号,车牌摇号,抽取幸运观众等等。

很多地方要求有使用方便、安全快捷的随机数产生方法。

当前主流的随机数电路分为两种,软件型和硬件型。

软件型的随机数产生电路方便快捷,但是安全性不高,而且必须借助电脑运行,在一些重要场合往往不方便使用,而且有安全漏洞。

应用于UHF RFID标签的低功耗真随机数发生器

2 真 随机数 发生器 的实现 方案

21 直 接 放 大 法 .

直 接 放 大 法对 电 阻热 噪 声 进 行 放 大 、 比较 后 得 出随机 数 。它 可 以得 到 性 能十 分 理 想 的 随机 数 ,但

收 稿 日期 t2 1-33 修 订 日期 :2 1 -5 1 000 —0 0 00 - 1 基 金 项 目 ;8 3计划 重 大 项 目 ( 0 8 6 20 AA0A12 4 0)

息传 送 。

已发 表 的 成果 中 ,真 随 机 数 发 生器 多应 用 在 有源 通 信 设 备 的密码 系统 中 , 电路 结 构采 用 多级 异 或 链 、伪 随机 网络 及 减 相 关 性 操 作 模 块 等 手 段 提 高 随 机 性 【 。该 种 结 构 的 随机 数 发 生 器 虽 具 有 很好 的 2 ] 随机 性 能 ,但 电路 结 构 复 杂 , 功耗 多达 到 mW 量 级 ,并 且芯 片 面 积 较 大 , 显然 不 适 合 集 成在 R I 标 FD

真 随机 数 发 生 器 依 托 于 自然 界 物 理 现 象 的 随机 特 性 ,随机 数来 源 于 真 实 的 随机 物 理 过 程 ,即使 算 法 等 重 要信 息 被 暴 露 , 也无 法 猜 测 其 结 果 ,理 论 上 高 质 量 的真 随机 数 发 生 器 产 生 的 随机 数 永 远 不 具备 周 期 性 。因 此 ,RFD标 签 芯 片 采 用真 随机 数 发 生 器 能够 有 效 地 提 高 R I 芯 片 的安 全 性 从 而 更好 的保 护 信 I FD

第l 5卷 第 4期

2 1 年 8月 00

文 章 编 号 : 10 -29(0 0 0 —100 0 704 2 1) 40 2 .5

基于物理噪声源的真随机数发生器的设计与实现

中 图 分 类 号 :TP 2 7 3 文 献 标 识 码 :A

0 引 言

1 真 随 机 数 发 生 器 电 路 设 计 与 实 现

预 测 性 。基 于 该 思 想 ,设 计 了 一 种 基 于 物 理 热 噪 声 与 单 片 机 技 术 的 真 随 机 数 发 生 器 , 可 产 生 0 Mb / s ~ 2 Mb / s 速 率 可 调 的 真 随 机 数 序 列 ;相 关 性 分 析 及 E NT 测 试 结 果 表 明所 产 生 的 随 机 序 列 具 备 良好 的 随机 统 计

发 生 器 如 图 2所 示 。

+ 3 . 3 V. 竖坠 § Q E 塑

泛 应 用于信 息 加密 、 密 码芯 片等 领域 。

本文设计 了一种 基 于物 理 热 噪声 源与 单 片机 技 术 的真 随机数 发 生器 , 该装 置 可 以产 生 0 Mb / s  ̄2 Mb / s

第 5期 ( 总第 1 9 2期 )

2 0 1 5年 1 O月

机 械 工 程 与 自 动 化

M ECHANI CAL E NGI NEE RI NG & AUTOM ATI ON

No. 5

0c t .

文章编号 : 1 6 7 2 - 6 4 1 3 ( 2 0 1 5 ) 0 5 — 0 0 0 1 — 0 3

峰值 为 3 . 3 V 的 随机 数 电信 号 ; ② 利 用 串行 通 信方 式

将 真 随机数 发 生器 产 生 的 “ 0 ” 、 “ 1 ” 随 机 比特序 列 以字 节 为单 元发 送 至上 位机 ( P C) 软 件进 行 分 析 、 处理 和存 储, 以方便 进一 步应 用 。发生 器 设计 完成 后 , 将 其产 生 的真 随机序 列进 行 了二 维点 阵 图 、 相 关性 分 析 和 E NT

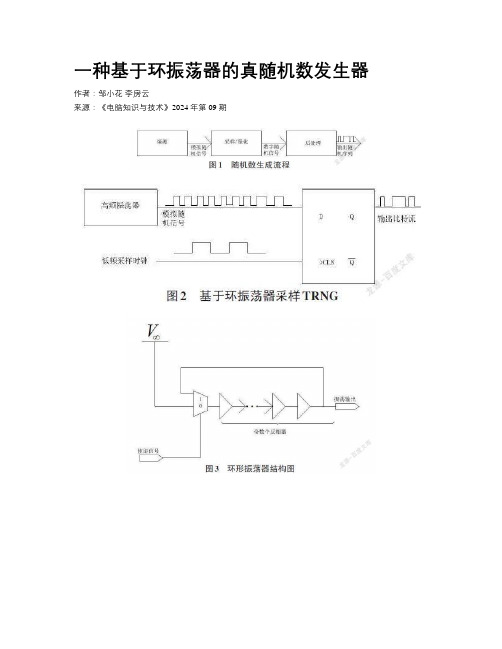

一种基于环振荡器的真随机数发生器

一种基于环振荡器的真随机数发生器作者:邹小花李房云来源:《电脑知识与技术》2024年第09期摘要:真随机数发生器(TRNG)是一种用于生成真随机数的设备,是安全芯片中的重要单元之一,生成的真随机数是确保通信加密及身份认证等密码协议安全性的必要工具。

仿真实验结果表明,随着抖动源抖动程度的增大,每次采样的熵趋近于1,即使在最坏的情况下也能达到误差低于10-4的水平。

文章进一步分析环振荡器(RO)的数学模型并提出一种基于环振荡器的高效率、低成本的真随机数发生器。

关键词:真随机数发生器;TRNG;环振荡器;RO;抖动源;jitter中图分类号:TN79,TN918 文献标识码:A文章编号:1009-3044(2024)09-0008-04开放科学(资源服务)标识码(OSID)0 引言随机数在现实世界中有广泛的应用,比如保障互联网安全的各种加密算法、计算机仿真、电子游戏、抽签等方面。

随机数分为两种,伪随机数和真随机数。

伪随机数是以数论和计算机理论为基础生成的,实现方便、分布均匀、成本低。

由于存在有限的可计算状态,伪随机数具有周期性,使其很容易破解[1]。

自然现象或物理过程中的各种随机噪声是真随机数发生器(True Random Number Generator,TRNG)產生随机数的方式。

伪随机数存在的周期性问题的解决方法让序列具有了真正的随机性,根据热噪声、闪烁噪声等随机噪声往往都是不可预测和产生的随机数无规律难破解的特点。

真随机数发生器产生的随机数存在生成速率相对较慢、随机数的统计特性不好、内外部环境影响的问题。

如何设计满足现代加密系统加密需求、具备良好性能的随机数已成为研究的重要问题。

关注熵源的设计和优化非常重要,因为熵源的品质从根本上决定着随机数发生器性能的好坏[2]。

梳理国内外相关研究的现状表明,有些科研人员已经实现了根据不同原理结构设计的真随机数发生器。

国内科研人员如鲁迎春提出基于可配置异步反馈环形振荡器的真随机数发生器,利用与非门和异或门形成可配置的异步反馈环形振荡器,改善熵源的随机性通过增加相位噪声和扩大时间抖动范围来实现[3]。

真随机数发生器的制作方法

真随机数发生器的制作方法

要制作一个真随机数发生器,我们需要利用物理过程或现象来

产生随机性。

下面我将从硬件和软件两个方面来介绍制作真随机数

发生器的方法。

硬件方法:

1. 热噪声发生器,利用半导体器件的热噪声来产生随机数。

可

以利用二极管的热噪声或者场效应晶体管的热噪声来作为随机数源。

2. 光电效应,利用光电二极管或者其他光敏器件接收自然光或

其他光源的微弱光信号,并转换为电信号作为随机数源。

3. 核衰变,利用放射性同位素的核衰变过程来产生随机数。

通

过探测放射性同位素衰变事件的时间间隔来获取随机数。

软件方法:

1. 基于环境噪声的随机数生成,通过利用计算机系统的环境噪声,如鼠标移动、键盘敲击、磁盘I/O等,来获取随机数。

2. 基于时间的随机数生成,利用计算机系统的高精度时钟和时

间戳来产生随机数。

3. 基于混沌理论的随机数生成,利用混沌系统的特性,通过迭

代计算产生随机数序列。

无论是硬件方法还是软件方法,都需要经过严格的测试和验证,确保生成的随机数具有均匀分布、独立性和不可预测性。

此外,真

随机数发生器的安全性也是非常重要的,特别是在密码学和安全通

信领域的应用中。

因此,在制作真随机数发生器时,需要考虑到系

统的安全性和可靠性。

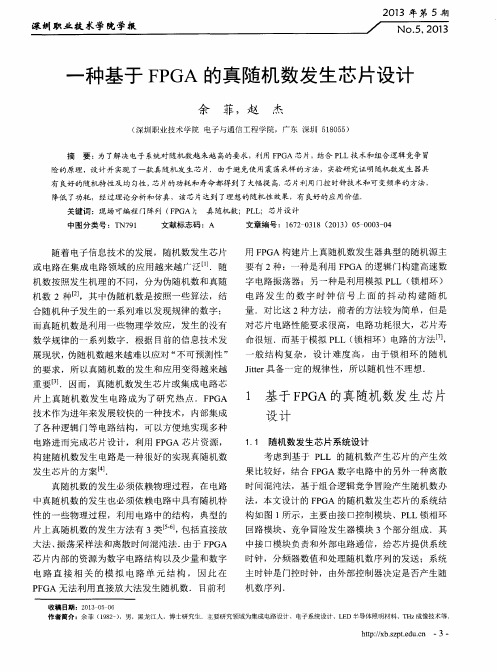

一种基于FPGA的真随机数发生芯片设计

用F P G A 构建 片上 真 随机数 发生 器典 型 的随机 源主 要有 2种 :一种 是利 用 F P GA 的逻辑 门构 建高 速数 字 电路振 荡器 ;另 一种 是利 用模 拟 P L L( 锁相 环 ) 电路 发 生 的 数 字 时 钟 信 号 上 面 的 抖 动 构 建 随 机 量 .对 比这 2种方 法 ,前者 的方 法较 为简 单 ,但是 对芯 片 电路性 能要 求很 高 , 电路 功耗 很大 ,芯 片寿 命很 短 .而基 于模 拟 P L L( 锁相 环 )电路 的方 法 J ,

h t t p : / / x b . s z p t . e d u . c n 一3一

在 多路 扰动 器线 当 中, 一共 有 4个控 制 位 . 每 个 控 制位 可 以控 制选 择 一条 延迟 线 或者 是 一条 导 线 进 行扰 动 , 利用 F P G A 中的 C MOS传 输 门来 实 现 两 路选 择 的 效果 .4个控 制 位 的延迟 线 按 照 2 作为 延 迟 的权值 ,第 一 个延 迟 线延 迟为 1个 时间 单位 ,第二 个延 迟 线 的延 迟为 2个 时 间单 位 ,第 三个 延 迟线 的 延迟 为 4个 时 间单位 ,第 四个 延迟 线 的延 迟为 8个时 间单 位 .这 样 ,随着 4个控 制

中接 口模 块负 责和 外部 电路 通信 ,给 芯片 提供 系统

构建 随机数 发 生 电路是 一种 很 好 的实 现真 随机 数

发生 芯 片 的方案 L 4 J .

真 随机 数 的发 生必 须依 赖物 理 过程 ,在 电路 中真 随机 数 的 发生 也必 须依 赖 电路 中具 有 随机 特 性 的一 些物 理过 程 ,利 用 电路 中 的结构 ,典 型的 片上 真 随机 数 的发 生方 法有 3类I 5 J , 包 括 直接 放 大法 、 振 荡采 样 法 和离散 时 间混 沌法 . 由于 F P G A 芯片 内部 的资源 为数 字 电路 结构 以及少 量和 数 字