一种基于FPGA的真随机数发生器设计与实现 (1)

一种仿 252Cf中子源随机脉冲信号参数检测系统的FPGA设计与实现

21 0 0年

第1 2期

l 2月

核 电子 学与探测 技术

Nu la e to i s& Dee t n Te h oo } ce r Elcr n c tc i c n lg o

Vo. 0 No 2 13 l De . c

2 O 0l

一

种 仿 2 f中子 源 随 机 脉 冲 信 号 参 数 5C 2

C /发裂 变 中子 源 所 产 生 的核 事 件 , 身 因 fl  ̄ 本 其 随机 性 而 在探 测上 出现统 计 涨 落 , 这表 现 核

信号 在 时 间上呈 泊松 分 布 , 幅度 上 服从 高斯 在

分布 。正 是 随 机 核 信 号 的 这 一 特 征 , 基 于 为

FG P A技术 开展 仿 c 中子 源 的核 信 号脉 冲参 f 数检测 提供 了理论 依 据 , 为仿 C 源 随 机 核 并 f 信 号用 于频 谱测 量 与分析 创 造 了条 件 。

关键词 : 仿 c 随机核脉 冲;P A;aV E f F G L b Iw

中 图分 类 号 : T 1 N91 文 献 标 识码 : A 文 章 编号 : 0 5 -9 4 2 1 ) 210 -5 280 3 ( 00 1—6 2 0

利用 c 自发 裂变 中子 源作 为激 发 源 , f 与

图1

收 稿 日期 :00 )-7 2 144 0

C 裂变 中子源核信号相关时域 f

分 析 原 理 示 意 图

由此 可见 , 上述 核 信 号 经过 核 辐射 探 测器

后输 出 的信号 , 是 一系列 大小不 一 95 , , 李 18 一 男 四川 遂 宁 市 人 , 士 博

检 测 系统 的 F GA 设 计 与 实 现 P

基于FPGA的串口通信设计与实现

置和输人数据计算出响应

的奇偶校验位,它是通过

纯组合逻辑来实现的。

2.6总线选择模块

总线选择模块用于

选择奇偶校验器的输入是

数据发送总线还是数据接

收总线。

2.7计数器模块

计数器模块的功能

是记录串行数据发送或者

接收的数日,在计数到某

数值时通知UART内核模

块。 3 UART程序设计 UART完整的工作流程可以分为接收过程

关键词:FPGA:UART:RS232

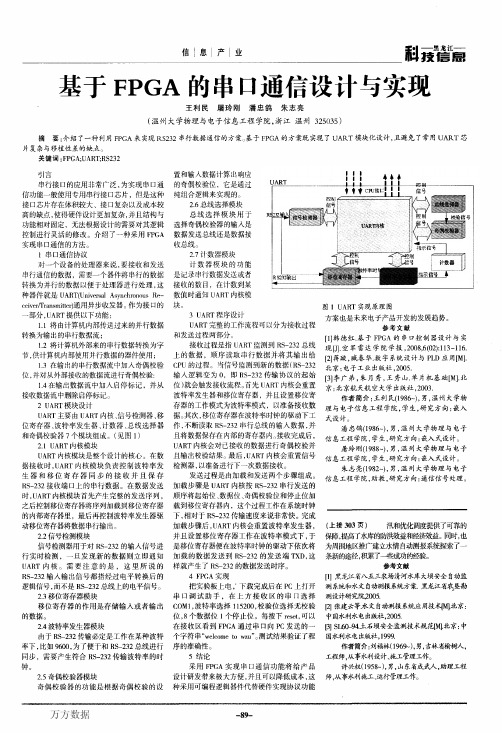

引言 串行接口的应用非常广泛,为实现串口通 信功能一般使用专用串行接口芯片,但是这种 接口芯片存在体积较大、接口复杂以及成本较 高的缺点,使得硬件设计更加复杂,并且结构与 功能相对固定,无法根据设计的需要对其逻辑 控制进行灵活的修改。介绍了一种采用FPGA 实现串口通信的方法。 1串口通信协议 对一个设备的处理器来说,要接收和发送 串行通信的数据,需要一个器件将串行的数据 转换为并行的数据以便于处理器进行处理,这 种器件就是UART(Universal Asynchronous Re— ceiver/Transmitter)通用异步收发器。作为接iSl的 一部分,UART提供以下功能: 1.1将由计算机内部传送过来的并行数据 转换为输出的串行数据流; 1.2将计算机外部来的串行数据转换为字 节,供计算机内部使用并行数据的器件使用; 1.3在输出的串行数据流中加入奇偶校验 位,并对从外部接收的数据流进行奇偶校验: 1.4在输出数据流中加入启停标记,并从 接收数据流中删除启停标记。 2 UART模块设计 UART主要由UART内核、信号检测器、移 位寄存器、波特率发生器、计数器、总线选择器 和奇偶校验器7个模块组成。(见图1) 2.1 UART内核模块 UART内核模块是整个设计的核心。在数 据接收时,UART内核模块负责控制波特率发 生器和移位寄存器同步的接收并且保存 RS一232接收端口上的串行数据。在数据发送 时,UART内核模块首先产生完整的发送序列, 之后控制移位寄存器将序列加载到移位寄存器 的内部寄存器里,最后再控制波特率发生器驱 动移位寄存器将数据串行输出。 2_2信号检测模块 信号检测器用于对RS一232的输入信号进 行实时检测,一旦发现新的数据则立即通知 UART内核。需要注意的是,这里所说的 RS一232输入输出信号都指经过电平转换后的 逻辑信号,而不是RS一232总线上的电平信号。 2_3移位寄存器模块 移位寄存器的作用是存储输入或者输出 的数据。 2.4波特率发生器模块 由于RS一232传输必定是工作在某种波特 率下,比如9600,为了便于和RS一232总线进行 同步,需要产生符合RS一232传输波特率的时 钟。 2.5奇偶校验器模块 奇偶校验器的功能是根据奇偶校验的设

基于FPGA的IIR数字滤波器的设计与仿真

万方数据万方数据模模图1IIR数字滤波器实现平台硬件结构及在线编程。

4IIR数字滤波器的设计与仿真4.1IIR数字滤波器的设计IIR数字滤波器系统函数在r程上呵在传统模拟滤波器设计的基础J二,采用阶跃响应不变法、冲激响应不变法或双线性变换法等方法得到;或者通过Matlab软件,调用相应的专用函数或工具包很方便的得到IIR滤波器的系统函数。

本文设计的滤波器采用Matlab与Verilog编程相结合的方式,首先根据滤波器的性能指标在Matlab中得到系统函数,然后采用Verilog编程实现。

在Matlab中对设计好的滤波器进行仿真确保所设计的滤波器符合要求,然后编写Verilog代码实现算法,在QuartusII中仿真以验证算法的正确性,最后以FPGA作为硬件实现平台测试滤波效果。

采用这种方法没计滤波器即快捷又能获得优化过的硬件电路,节约硬件资源。

本文引例是二阶的低通滤波器的没计,记采样频率为4MHz,通带截止频率为100kHz,阻带截止频率为1MHz,通带最大衰减为0.86dB,阻带最小衰减为30.4dB。

利用Matlab软件中的FDATool专用数字滤波器设计工具,可得到如下系统函数:肌,=等等蒜等等㈣4.2Matlab仿真在FDATool中设计好滤波器后,导出滤波器系数,采用编程的方式对所设计的滤波器进行仿真验证,以60kHz和1MHz的正弦信号叠加作为滤波器输入信号,在Matlab中运行程序,仿真结果如下图2和图3。

·--——306---——图2滤波器的输入信号圈3滤波器的输出信号4.3传输函数系数的量化处理与Verilog代码设计好的滤波器,需要把系数放大若干倍取整数部分,在FPGA中以节点形式进行存储,取整的二进制位数越多逼近程度越好,但所占用的硬件资源也越大,对速度也有影响。

同时,系数量化处理必须保证量化前后系统幅频特性曲线基本一致,以满足滤波要求。

另外,数字滤波器运算过程中有限字长效应也会造成误差,因此对滤波器中乘加法器及寄存器的数据位宽也要进行合理设计,以防止产生极限环现象和溢出振荡。

随机交织器的设计与实现

随机交织器的设计与实现随机交织器是一种常用于通信系统中的技术,能够提高数据传输的可靠性和信号质量。

在本文中,我们将介绍随机交织器的设计与实现,并给出一些相关的参考内容。

一、随机交织器的设计1. 原理概述随机交织器通过以随机的方式改变信号的时序,将连续的数据按照一定规律重新排列,从而达到提高信号质量的目的。

其基本原理是在发送端将要发送的数据乱序传输,然后在接收端再将其恢复为原有的顺序。

2. 设计步骤(1) 确定随机交织器的输入输出数据格式,包括数据长度、数据类型等。

(2) 设计随机交织器的随机数生成器,用于产生随机的交织规则。

可以使用伪随机数生成算法,如线性反馈移位寄存器(LFSR)算法。

(3) 实现交织函数,将输入的数据按照随机生成的规则进行交织处理,生成交织后的输出数据。

(4) 实现反交织函数,将接收到的交织后的数据按照相同的交织规则进行反交织处理,恢复原始的数据顺序。

(5) 验证设计的正确性,通过在仿真环境中进行测试,比较输入数据和输出数据的差异。

二、随机交织器的实现1. 硬件实现随机交织器的硬件实现通常采用FPGA(Field-Programmable Gate Array)或ASIC(Application-Specific Integrated Circuit)等可编程逻辑器件。

相关的参考内容可以包括FPGA的开发手册、硬件描述语言(VHDL、Verilog)的教程以及现有的随机交织器的设计实例。

2. 软件实现随机交织器的软件实现可以通过编程语言来实现,例如C、C++或MATLAB等。

相关的参考内容可以包括编程语言的语法手册、相关算法的原理解释与实现思路以及现有的随机交织器的源代码。

3. 开源库与工具在设计与实现随机交织器时,可以借助现有的开源库与工具来简化开发过程。

例如,Matplotlib和NumPy库可用于数据可视化和数值计算;GNU Radio是一个开源的软件无线电平台,提供了大量的通信系统模块,包括随机交织器。

基于FPGA的核辐射脉冲信号发生器研究

基于FPGA的核辐射脉冲信号发生器研究摘要本文研究了一种基于FPGA的核辐射脉冲信号发生器。

首先,本文介绍了核辐射脉冲信号的基本概念和特点,包括脉冲宽度、幅度、频率等。

接着,本文阐述了基于FPGA的核辐射脉冲信号发生器的设计方法,包括硬件设计和软件设计。

硬件设计包括FPGA芯片的选择、电路设计和调试等;软件设计包括VHDL语言编写、模块设计和功能仿真等。

最后,本文通过实验验证了该发生器的性能和可靠性,并指出了未来研究的方向和挑战。

引言核辐射脉冲信号发生器是一种能够产生核辐射脉冲信号的仪器,广泛应用于核物理、医学、安全等领域。

传统的核辐射脉冲信号发生器通常采用模拟电路实现,存在着电路复杂、调试困难、稳定性差等问题。

随着FPGA技术的不断发展,基于FPGA的核辐射脉冲信号发生器逐渐成为研究的热点。

FPGA具有高度的可编程性和可重复性,能够实现复杂的逻辑电路,具有体积小、重量轻、可靠性高等优点。

因此,研究基于FPGA的核辐射脉冲信号发生器具有重要的理论意义和实际应用价值。

基于FPGA的核辐射脉冲信号发生器设计基于FPGA的核辐射脉冲信号发生器主要包括硬件设计和软件设计两部分。

硬件设计主要包括FPGA芯片的选择、电路设计和调试等;软件设计主要包括VHDL语言编写、模块设计和功能仿真等。

2.1 硬件设计硬件设计是实现基于FPGA的核辐射脉冲信号发生器的基础。

在硬件设计中,我们选择了Xilinx公司的Virtex-5 FPGA 芯片,该芯片具有高度集成、高性能、低功耗等优点,能够满足我们的设计要求。

同时,我们设计了包括电源电路、时钟电路、复位电路、数据采集电路等外围电路,实现了完整的硬件系统。

2.2 软件设计软件设计是实现基于FPGA的核辐射脉冲信号发生器的核心。

在软件设计中,我们采用了VHDL语言编写程序,实现了包括脉冲宽度调整、幅度调整、频率调整等模块。

同时,我们采用了MATLAB软件对生成的核辐射脉冲信号进行了仿真和验证。

FPGA_ASIC-基于FPGA的RS编码器的设计与实现

基于FPGA的RS编码器的设计与实现何秋阳 来源:EDN摘要:FPGA能够快速和经济地将电路描述转化为硬件实现,而且对设计的修订也比较方便。

而通常的ASIC需要的设计时间较长,制作费用也较高,也不便于调整。

所以本设计是基于FPGA的RS编码设计。

关键词:FPGA,RS编码器,ASIC1 RS编码原理RS编码是一种线性的块编码,其表示形式为RS(N,K)。

当编码器接收到一个数据信息序列,该数据信息序列被分割成若干长度为K的信息块,并通过运算将每个数据信息块编码成长度为N 的编码数据块。

在RS码中的码元符号不是二进制而是多进制符号,其中2m进制使用更为广泛。

能纠正t个错的RS码具有,如表1参数所示。

上述参数,t表明最多可以纠正t个随机错误符号。

由于RS码是对多进制符号纠错,RS码可用于纠正突发错误,比如能纠两个八进制符号错误的RS(7,3)码,每个符号可用3 bit二进制符号表示。

八进制的RS(7,3)码相当于二进制的(21,9)码,因此纠两个符号就相当于纠连续6 bit二进制符号的突发错误,然而二进制的(2l,9)码却没有纠6 bit突发错误的能力,它能纠任何2个随机错误以及长度≤4的突发错误。

通用的RS编码的运算步骤:(1)确定RS编码器的生成多项式g(x),这里选用了最为常用的生成多项式,如式(1)所示。

式中a定义为m阶初等多项式p(x)的根它可生成全部GF域的元素。

(有关GF域的内容可参阅相关书籍)。

以RS(15,9)为例,RS(15,9)的生成多项式,如式(2)(2)通过对取模运算产生校验信息多项式p(x)如式(3)式中m(x)表示RS编码码字中的数据信息,它是K一1阶的线性多项式。

(3)通过加法运算生成最终的编码后的多项式c(x)如式(4)RS码的编码主要是围绕码的生成多项式g(x)进行的,一旦生成多项式确定了,则码就完全确定了。

2 RS编码的设计实现在一些特定应用域中,RS码的设计与实现是比较困难的。

基于FPGA的DDS信号发生器的设计——开题报告

毕业设计(论文)材料之二(2)本科毕业设计(论文)开题报告题目:基于FPGA的DDS信号发生器的设计课题类型:设计□√实验研究□论文□学生姓名: XXX学号: 0000000000专业班级: XXXX学院:电气工程学院指导教师: XX开题时间: 201X年X月X日201X年 X月X 日一、毕业设计(论文)内容及研究意义(价值)本问设计基于FPGA的DDS的信号发生器,主要满足一下几个要求:1.通过编程产生正弦波、方波、三角波信号基波;2.有足够宽的频率;3.输出的信号电压能在一定范围内调节;研究意义信号发生器是一种常用的信号源,它是一种为电子测量和计量工作提供信号的设备,信号源作为一种基本电子设备无论是在教学、科研还是在部队技术保障中,都有着广泛的使用。

在测试、研究、调整电子电路及设备时,为测定电路的一些电参量,如测量频率响应、噪声系数,为电压表定度等提供符合所定技术条件的电信号,以模拟在实际工作中使用的待测设备的激励信号。

随着科学技术的发展和测量技术的进步经济的发展,对信号源的要求越来越高,传统的信号发生器大多采用专用芯片或单片机或模拟电路,成本高、控制方式不灵活,已无法满足目前日益发展的数字技术领域科研和教学的需要。

但近几年随着FPGA和DDS 技术的快速发展和广泛应用,它具有频率分辨率极高、频率切换速度快、切换相位连续、输出信号相位噪声低、可编程、全数字化易于集成、体积小、重量轻、有效的降低成本等优点。

其在信号发生器上的应用得到了很好的认同,很好的解决了有传统信号发生器带来的一些问题,信号发生器己成为测试仪器中至关重要的一类,因此开基于FPGA的DDS发信号发生器具有重大意义。

二、毕业设计(论文)研究现状和发展趋势(文献综述)信号发生器的国内外现状和应用近几年随着FPGA和DDS技术的快速发展,基于FPGA实现的DDS信号发生器不仅能产生传统函数信号发生器说能产生的波形,还可以产生任意编辑的波形,这是其他频率合成方式所没有的。

基于FPGA的高斯白噪声生成

基于FPGA的高斯白噪声生成王林;芮国胜;田文飚【摘要】高斯白噪声生成用于宽带短波信道模拟器系统,利用m序列发生器及查表法实现,采用现场可编程门阵列(FPGA)实现噪声生成器的设计,整个噪声生成器由VHDL语言编写,便于修改升级.仿真结果表明,基于FPGA设计实现的高斯白噪声生成器能够满足宽带短波信道模拟器性能指标要求,并且具有灵活性、通用性、修改参数方便等特点,具有很好的实用价值.%The Gaussian white noise generating was applied to wideband HF channel simulator, which adopts m sequence generator and look-up table.The noise generator designed by FPGA technology and programmed by VHDL can be easily upgrade.The simulation results indicate that the Gaussian white noise generator based on FPGA can satisfy the performance request of wideband HF channel simulator, and has characteristics of agility, universality and conveniences.It has a good practical value.【期刊名称】《现代电子技术》【年(卷),期】2011(034)003【总页数】3页(P104-106)【关键词】信道模拟器;高斯分布;现场可编程逻辑器件;m序列【作者】王林;芮国胜;田文飚【作者单位】海军航空工程学院研究生管理大队,山东烟台264001;海军航空工程学院信号与信息处理山东省重点实验室,山东烟台,264001;海军航空工程学院研究生管理大队,山东烟台264001【正文语种】中文【中图分类】TN911-340 引言短波信道是时变色散信道[1],在短波通信装备测试中,需要在各种地域反复测量,必然消耗大量人力、物力和财力,而通过短波信道模拟器可以解决在真实地域通信试验中遇到的上述问题。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第19卷第lO期电子设计工程2011年5月V01.19No.10ElectronicDesignEngineeringMay2011

一种基于FPGA的真随机数发生器设计与实现张聪,于忠臣(北京工业大学北京市嵌入式系统重点实验室。北京100124)

摘要:设计并实现了一种基于FPGA的真随机数发生器。利用一对振荡环路之间的相位漂移和抖动以及亚稳态作为随机源。使用线性反馈移位寄存器的输出与原始序列运算作为后续处理。在Xili啦Virtex一5平台的测试实验中,探讨了振荡器数量以及采样频率等参数对随机序列的统计特性的影响。测试结果表明本设计产生的随机序列能够通过DIEHARD测试。性能满足要求。由于仅使用了普通逻辑单元,使得本设计能够迅速移植到ASIC设计。大大缩短了开发周期。关键词:真随机数发生器;振荡环;相位漂移与抖动;亚稳态;FPGA中图分类号:TN782文献标识码:A

文章编号:1674-6236(2011)10-0176埘

Designandimplementationa

FPGA・basedtruerandom

number

generator

ZHANGCong,YUZhong-then

(BeijingEmbeddedSystemKeyLab,BellingUniversityofTechnology,Be;iing100124,China)

Abstract:AFPGA-basedtruerandomnumbergenerator(TRNG)ispresentedinthispaper.Thedesignutilizesapairofoscillatorsthata弛permittedtofree-run.Atsomepoint.thefree-runningoscillatorsarecoercedtomatchstatesviaa

bi—stabledevice.Metastabilityandoscillatordriftandjitteraretwopossiblecausesofrandomness,andalinearfeedbackshiftregister(LFSR)isusedtoaspost-precessinKInthetestsollXilinxVirtex-5physicalplatform,thee如ctsofthedesign

parameters。suchasthenumberofoscillatorsandsamplingfrequency,arediscussed.TheresultofDIEHARDsuitetests

forrs.ndomes8indicatesthattheperformanceoftherandomsequenceoftheTRNGmeetstherequirement.Sincethe

TRNGonlyUseScommonlogicunites,itcanbequicklytransplantedtotheASICdesignandshortenthedevelopment

cycle.Keywords:truerandomnumbergenerator;oscillationring;phasedriftandjitter;metastability;FPGA

真随机数发生器(TRNG)在统计学、信息安全等领域有着广泛的应用。在这些领域中。不仅要求数据序列分布均匀、彼此独立.而且要求其具有不可预测性.能够抵御针对随机性的攻击。B.Sunar。W.J.Martin和D.R.Stinson提出【”,真随机数发生器的性能受3个因素的影响:熵源(EntropySource),采集方式(HarvestingMechanism)和后续处理(Post—Processing)。在电路系统中最常见的三种真随机数产生方法为田:1)直接放大法:放大电路中的电阻热噪声等物理噪声。通过比较器进行比较后获得随机数序列;2)振荡采样法:用带有抖动的慢振荡器通过D触发器采样一个周期固定的快振荡器,输出随机序列;3)离散时间混沌法:利用混沌电路不可预测以及对初始条件敏感的依赖性的特点产生随机序列。基于模拟电路的结构,熵源的统计分布更加理想,且熵源噪声不随采样周期的变化而改变;基于数字电路的结构,集成度高。便于在FPGA等通用可编程平台上实现,但熵源的统计特性与模拟电路相比不够理想131。本文尝试了一种用纯数字电路实现的TRNG结构,且不收稿日期:2011—02—24稿件编号:201102063使用诸如PLL等特殊资源。便于设计由FPGA验证移植到芯片设计。其核心思想是使用反相器和延时单元构成两个相互独立的振荡器.由于内部噪声的差异引起的相位偏移作为熵源,经过一段时间振荡后。随机的状态由数字双稳态电路锁存。多组振荡器的输出。经过异或和同步处理后得到随机序列。该TRNG在FPGA物理平台上实现并进行了测试验证。

1TRNG的设计1.1相位漂移与抖动由于受到电路中噪声的影响,数字电路中时钟信号的周期在每个不同的周期上可能缩短或者加长。这就是时钟抖动。抖动可以用许多方法来衡量和表征.它是一个均值为零的随机变量。振荡器起振时刻的差异和电路元件的工艺偏差,使得振荡器间存在相位漂移。因此抖动信号和相位漂移适合在数字电路中作为TRNG的随机源。1.2亚稳态锁存器是有逻辑‘l’和‘0’两个稳定状态的双稳态器件。但是在特殊情况下其可能进入亚稳态[41。此时它的输出是介

作者简介:张聪(1985一),男,辽宁铁岭人,硕士研究生。研究方向:集成电路数字前端设计。-176..

万方数据张聪.等一种基于FPGA的真随机数发生器设计与实现于‘l’和‘0’之间的中间电平。如图l所示锁存器用两个反相器和两个开关表征。当锁存器导通时,采样开关闭合,保持开关打开(图a);当锁存器关闭时,采样开关打开,保持开关闭合(图b)。图e展示了两个反相器的直流传输特性。当锁存器关闭时A=B,稳态是A=B--0和A=B=Vno,亚稳态为A=B=V。。其中V。不是一个合理的逻辑值。因为电平在该点是相互稳定的并且可以无限期停留,所以称该点为亚稳态。但是,任何噪声或者其他干扰都会使得A和B最终稳定在两个稳态中的一个状态。图d非常形象地表征了亚稳态。它就好像处于山顶的小球任何干扰都会使小球滚落到山两端的稳定状态。∞…∞一鸶矗图

(a)采样("¥ampling(b)保持

《b)hold图1

Fig.11.3振荡器的设计如图2所示。二选一复用器既作为延迟单元又作为选通单元使用。当选通信号为‘1’时,形成两个相互独立、自由振荡的环形振荡器。当选通信号为‘0’时,两组反相器交叉相连形成双稳态器件。自由振荡时.两个振荡器之间存在着抖动和相位偏移。在振荡的停止时刻,即振荡环路断开、两组反相器交叉连接时。反相器的瞬时输出电压以及内部噪声的绝对和相对值决定了电路最终稳定在哪个逻辑值上。有时即使反相器跨接在一起。电路也会振荡很长・段时间才能稳定下来。形成亚稳态。综上所述,随机序列的来源用到了抖动和亚稳态两种机制。图2振荡器结构图Fig.2Oscillatorstructure波形如图3所示,为了方便数据采集选通信号是由时钟经过分频得到的。在自由振荡阶段,输出信号快速变化不属于任何稳定状态。在图中用斜线表示。在解析阶段,电路是双稳态器件。此时应该保持解析时间足够长。从而使输出电平在大多数情况下稳定在逻辑‘l’或‘0’。采样时钟选通信号振荡输出图3波形图Fig.3Waveform1.4随机源模块的电路设计各个振荡器的输出经过异或运算可以增加随机性,而亚‘c)transferchal"actefistic亚稳态Metability

(d】mechanicaldiagram

ofmeta¥table

稳态的传播会造成后续电路的错误动作。因此使用同步器将异或后的随机序列与后续电路隔离开来。同时也方便采集稳定的输出序列做性能分析。此处采用了三级寄存器的同步结构。由MTBF(MeanTimeBetweenFailure)四的定义可知,平均需要经过数百年时间才会发生一次亚稳态通过同步器向下传播的事件。因此是满足设计要求的。该模块电路图如图4所示。

图4随机源模块电路Fig.4Circuitofrandomsource

1.5后续处理模块的设计理想情况下.D触发器所采集的信号具有随机的统计特性。可是FPGA内部电路不可避免地会受到温度漂移、电压抖动等不良因素影响。从而导致采样得到的随机信号中存在偏置.影响结果的统计特性。所以在采样得到随机序列后要对数据进行消偏处理.使O和l出现的概率相当。本设计采用16位最大长度二进制伪随机序列(PseudoRandomBinary

Sequence)ts的输出与采样得到的随机序列进

行异或运算作为后续处理,PRBS产生电路消耗资源少并且使用线性反馈移位寄存器实现,非常适合于在FPGA上实现。它的生成多项式是:G116FXl6+X13+X12+X“+F+X6+X3+X+l(1)多项式表示如图5所示。

2TRNG的FPGA实现与测试整个TBNG的实验环境由外部时钟源、FPGA开发板以及逻辑分析仪组成。TRNG采用Xilinx公司的Virtex一5系列中的XCSVLXI10作为物理实现平台,外部时钟频率为64MHz。

由FPGA产生的随机数据,经逻辑分析仪采集后,使用

图5PRBS的多项式表示Fig.5Polynomialrepresentation

ofPRBS

一177—

万方数据