武汉大学计算机学院数字逻辑2010级(A卷A类)期末考试卷

2010武汉大学数字逻辑试题答案

D2 D1 0 0 1 1 0 0 1 1 0 1 1 0 0 1 1 0 状态表

Q3n 1

0 0 1 1 0 0 1 1

n 1 Q2

n 1 Q2

Q1n 1

0 1 0 1 1 0 1 0

0 1 0 1 0 1 0 1

Q3n 1

0 0 1 1 0 0 1 1

Q1n 1

0 1 0 1 1 0 1 0

6.11 8.增加冗余项,增加惯性延迟环节,选通法

6. A

7.B

8. A

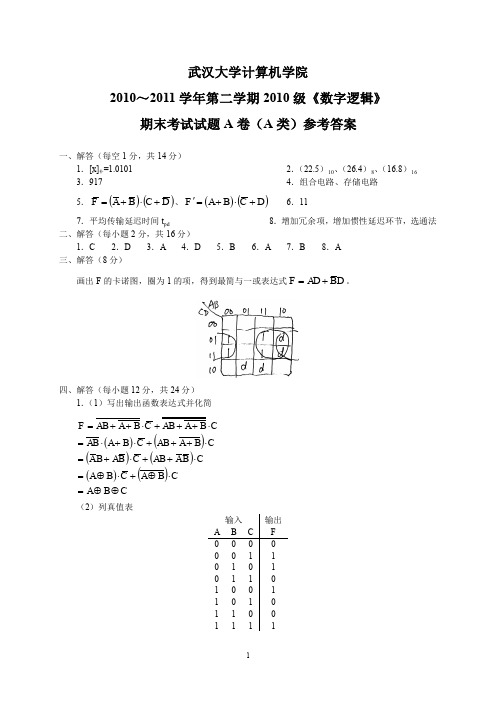

画出 F 的卡诺图,圈为 1 的项,得到最简与一或表达式 F AD B D 。

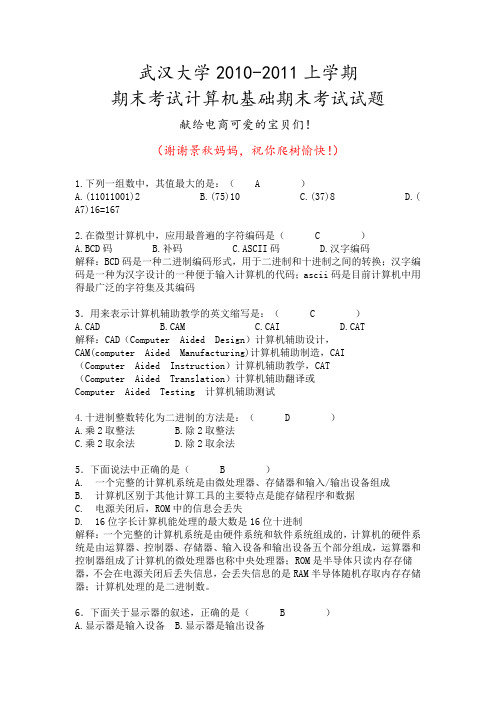

四、解答(每小题 12 分,共 24 分) 1. ( 1)写出输出函数表达式并化简

F AB A B C AB A B C AB A B C AB A B C A B AB C AB A B C A B C A B C A B C

Si m1 m2 m4 m7 m1 m2 m4 m7 Ci m3 m5 m6 m7 m3 m5 m6 m7

(4)画逻辑图

2. (1)QDQCQBQ A:寄存器状态输出端;DCBA:并行数据输入端;DR:右移串行数据输入端; DL:左移串行数据输入端; CLR :清零端, CLR =0 时,QDQCQBQ A=0000,正常工作时 CLR =1; CP:工作脉冲;S 1S0:工作方式控制端,可控制实现右移、左移、并入、保存。 (2)a、因为序列周期 TP =8,所以需要移位寄存器的级数 n≥ 3,假设选择 QDQC QB 三位,要产 生的序列从右移串行输入端 DR 输入,在 CP 作用下,经 QDQCQB 右移从 QB 端一位一位串行输出, QDQCQB 的初态应为最先输出的右边三位,即 000。 b、令 CLR =0,使 QDQCQB=000。 c、 再令 CLR =1, S 1S0=01, 在 CP 作用下, DR 端依次输入 10111000, 即可从 QB 端循环产生 11101000 序列。

数字逻辑电路期末考试试卷及答案

期末考试试题(答案)一、选择题(每小题2分,共20分)1. 八进制(273)8中,它的第三位数2 的位权为___B___。

A .(128)10B .(64)10C .(256)10 D .(8)10 2. 已知逻辑表达式C B C A AB F ++=,与它功能相等的函数表达式_____B____.A .AB F = B .C AB F += C .C A AB F +=D . C B AB F +=3. 数字系统中,采用____C____可以将减法运算转化为加法运算.A . 原码B .ASCII 码C . 补码D . BCD 码4.对于如图所示波形,其反映的逻辑关系是___B_____。

A .与关系B . 异或关系C .同或关系D .无法判断 5. 连续异或1985个1的结果是____B_____。

A .0B .1C .不确定D .逻辑概念错误6。

与逻辑函数D C B A F +++= 功能相等的表达式为___C_____。

A . D C B A F +++= B . D C B A F +++=C .D C B A F = D .D C B A F ++=7.下列所给三态门中,能实现C=0时,F=AB ;C=1时,F 为高阻态的逻辑功能的是____A______。

B A F & ∇ F B A &8. 如图所示电路,若输入CP脉冲的频率为100KHZ,则输出Q的频率为_____D_____。

A. 500KHz B.200KHzC. 100KHz D.50KHz9.下列器件中,属于时序部件的是_____A_____.A.计数器B.译码器C.加法器D.多路选择器10.下图是共阴极七段LED数码管显示译码器框图,若要显示字符“5”,则译码器输出a~g应为____C______。

A. 0100100 B.1100011 C. 1011011 D.0011011二、填空题(每小题2分,共20分)11.TTL电路的电源是__5__V,高电平1对应的电压范围是__2。

《数字逻辑》期末考试A卷参考答案

《数字逻辑》期末考试 A 卷参考答案、判断题:下面描述正确的打’/,错误的打‘X’(每小题1分,共10 分)1、为了表示104个信息,需7位二进制编码[V ]2、BCD码能表示0至15之间的任意整数[X ]3、余3码是有权码[X ]4、2421码是无权码[X ]5、二值数字逻辑中变量只能取值6、计算机主机与鼠标是并行通信7、计算机主机与键盘是串行通信8、占空比等于脉冲宽度除于周期0和1,且表示数的大小[X ][X ][V ][V ]9、上升时间和下降时间越长,器件速度越慢[V ]10、卡诺图可用来化简任意个变量的逻辑表达式[X ]、写出图中电路的逻辑函数表达式。

(每小题5分,共10分)1、F=A B2、F= AB CD2分,共20分)1、在图示电路中.能实现逻辑功能F = ATH 的电路是 A °TTL 电路(A) F = ABCD(B) F = AH ・ CD -(C) F= A + B + C + D(D) F = A + B • C + D (E) F= A BCD4 . 己知F 二ABC + CD ■可以肯定使F = 0的情况是 _°(A) A=0, BC= 1; (B) B= 1 , C= 1 } (C) AB= 1, CD=Q.(D) BC= 1 , D= 15、逻辑函数A B+BCD+A C+ B C 可化简为A,B,C,D 。

(A) AB + AC + BC (B) AB + C (A4-B)(C) AB + CABA — O ?=11 QA |— I1 F •-&1 Q AB L Il —(B)悬0----空。

—A — &Bo —Co- &BA3 •满足如图所示电路的输岀函数F 的表达式为丄3B 1 o — VOF(D) AB +C (E) 19.图示电路中,当各触发器的状态为C 时.再输入一个CP 脉冲,融发器的 状态为QiQ 严0 0。

(附解析)武汉大学计算机基础2010试卷

武汉大学2010-2011上学期期末考试计算机基础期末考试试题献给电商可爱的宝贝们!(谢谢景秋妈妈,祝你爬树愉快!)1.下列一组数中,其值最大的是:( A )A.(11011001)2B.(75)10C.(37)8D.( A7)16=1672.在微型计算机中,应用最普遍的字符编码是( C )A.BCD码B.补码C.ASCII码D.汉字编码解释:BCD码是一种二进制编码形式,用于二进制和十进制之间的转换;汉字编码是一种为汉字设计的一种便于输入计算机的代码;ascii码是目前计算机中用得最广泛的字符集及其编码3.用来表示计算机辅助教学的英文缩写是:( C )A.CADB.CAMC.CAID.CAT解释:CAD(Computer Aided Design)计算机辅助设计,CAM(computer Aided Manufacturing)计算机辅助制造,CAI(Computer Aided Instruction)计算机辅助教学,CAT(Computer Aided Translation)计算机辅助翻译或Computer Aided Testing 计算机辅助测试4.十进制整数转化为二进制的方法是:( D )A.乘2取整法B.除2取整法C.乘2取余法D.除2取余法5.下面说法中正确的是( B )A. 一个完整的计算机系统是由微处理器、存储器和输入/输出设备组成B. 计算机区别于其他计算工具的主要特点是能存储程序和数据C. 电源关闭后,ROM中的信息会丢失D. 16位字长计算机能处理的最大数是16位十进制解释:一个完整的计算机系统是由硬件系统和软件系统组成的,计算机的硬件系统是由运算器、控制器、存储器、输入设备和输出设备五个部分组成,运算器和控制器组成了计算机的微处理器也称中央处理器;ROM是半导体只读内存存储器,不会在电源关闭后丢失信息,会丢失信息的是RAM半导体随机存取内存存储器;计算机处理的是二进制数。

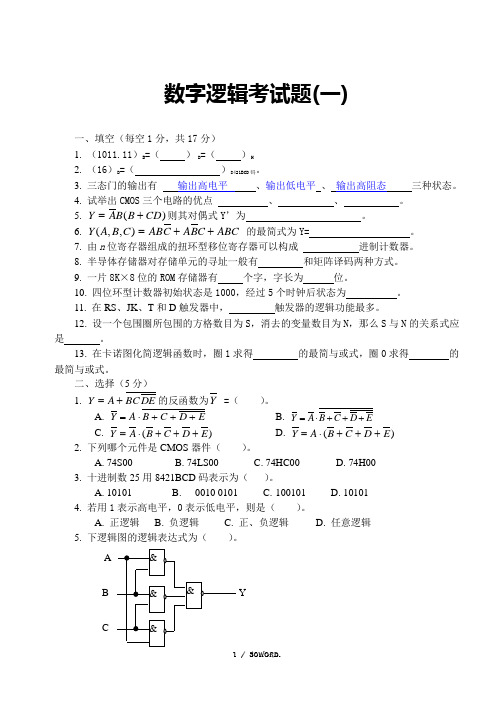

数字逻辑考试题.(优选)

数字逻辑考试题(一)一、填空(每空1分,共17分)1. (1011.11)B =( ) D =( )H2. (16)D =( )8421BCD 码。

3. 三态门的输出有 输出高电平 、输出低电平 、 输出高阻态 三种状态。

4. 试举出CMOS 三个电路的优点 、 、 。

5. )(CD B B A Y +=则其对偶式Y ’为 。

6. ABC C B A C AB C B A Y ++=),,( 的最简式为Y= 。

7. 由n 位寄存器组成的扭环型移位寄存器可以构成 进制计数器。

8. 半导体存储器对存储单元的寻址一般有 和矩阵译码两种方式。

9. 一片8K ×8位的ROM 存储器有 个字,字长为 位。

10. 四位环型计数器初始状态是1000,经过5个时钟后状态为 。

11. 在RS 、JK 、T 和D 触发器中, 触发器的逻辑功能最多。

12. 设一个包围圈所包围的方格数目为S ,消去的变量数目为N ,那么S 与N 的关系式应是 。

13. 在卡诺图化简逻辑函数时,圈1求得 的最简与或式,圈0求得 的最简与或式。

二、选择(5分) 1. DE BC A Y +=的反函数为Y =( )。

A. E D C B A Y +++⋅= B. E D C B A Y +++⋅=C. )(E D C B A Y +++⋅=D. )(E D C B A Y +++⋅=2. 下列哪个元件是CMOS 器件( )。

A. 74S00B. 74LS00C. 74HC00D. 74H003. 十进制数25用8421BCD 码表示为( )。

A. 10101B. 0010 0101C. 100101D. 101014. 若用1表示高电平,0表示低电平,则是( )。

A. 正逻辑B. 负逻辑C. 正、负逻辑D. 任意逻辑5. 下逻辑图的逻辑表达式为( )。

A. AC BC AB Y =B. BC AC AB Y ++=C. BC AC AB Y ++=D. BC AC AB Y =6. 三态门的逻辑值正确是指它有( )。

武汉大学计算机学院《外部设备》期末考试试卷.doc

武汉大学计算机学院《外部设备》期末考拭试卷(A卷)开卷2010—20"学年第一^期一.填空题(每空2分,共30分)1.第-•个采用LGA 775架构的CPU是拥有P赚ott核心的Pentium 4E ,这类CPU被称Pentium500 系列。

2.网络是多台计m几之闽通过M络协议和值u进行述接形成的互连关系,组逑网络的主要目的是实现资源共享o3.磁盘文件空间分配的最小单位是遮,磁盘文件读写的最小单位是扇界暈为512字节。

4.字符显示包括字符奶和W,各占据一个字甘的低7位,两个字节的最高位恒为0_。

5.早期为实现内存双通道技术,Intel公司在北桥芯八中设置两个内存控制器,AMD公司在CPU中设置两个内存控制器,通过这样的设置,使内存带宽增加-倍。

二词语解释(每小题3分,共15分,英文缩写应写出英文全称)1.REE: Rapid Execution Engine,快速执行引擎。

在ALU中添加REE,采用双沿触发方式,在时钟上升沿和下降沿都nJ•进行®本运算,使运行速度成倍增加。

2.前端总线:FSB (Front Side Bus), Pentium 4釆用多重数据速率QDR后,将CPU与主芯片组、内部存储器、主板髙速缓存的数掘传输通道独立出來,组成前端总线。

3.SIMD: Single Instruction, Multiple Data,单指令多数掘,足指-条指令可同吋对多个数据进行相同操作。

4.超标S:采用双流水线工作方式,在CPU内部设置两条流水线,采用并发机制,在一个时钟周期内可以执行两条指令、5.ADSL: Asymmetric Digital Subscriber Line,非对称数字用户线路,非对称是指上、下行速率不对称。

ADSL下行通道川于卜‘载信息,上行通道川于上传信息,电话服务通道用于普通电话服务,在一条电话线上三个通道可同时工作。

三.简答题(每小题5分,共25分)1.DVD与CD的主要区别是什么?(1)盘Ji•厚度:DVD盘R厚度为0.6毫米,CD为1.2毫米。

数字逻辑期末复习题(DOC)

CB AC B A ABC C B A C B A ABC ⋅⋅=++=一、选择题(每小题2分,共20分)1. 八进制(273)8中,它的第三位数2 的位权为___B___。

A .(128)10B .(64)10C .(256)10D .(8)102. 已知逻辑表达式C B C A AB F ++=,与它功能相等的函数表达式_____B____。

A .AB F = B . C AB F += C .C A AB F += D . C B AB F +=3. 数字系统中,采用____C____可以将减法运算转化为加法运算。

A . 原码B .ASCII 码C . 补码D . BCD 码4.对于如图所示波形,其反映的逻辑关系是___B_____。

A .与关系B . 异或关系C .同或关系D .无法判断 5. 连续异或1985个1的结果是____B_____。

A .0B .1C .不确定D .逻辑概念错误6. 与逻辑函数D C B A F +++= 功能相等的表达式为___C_____。

A . D C B A F +++= B . D C B A F +++=C .D C B A F = D .D C B A F ++=7.下列所给三态门中,能实现C=0时,F=AB ;C=1时,F 为高阻态的逻辑功能的是____A______。

8. 如图所示电路,若输入CP脉冲的频率为100KHZ,则输出Q的频率为_____D_____。

A. 500KHz B.200KHzC. 100KHz D.50KHz9.下列器件中,属于时序部件的是_____A_____。

A.计数器B.译码器C.加法器D.多路选择器10.下图是共阴极七段LED数码管显示译码器框图,若要显示字符“5”,则译码器输出a~g应为____C______。

A. 0100100 B.1100011 C. 1011011 D.0011011二、填空题(每小题2分,共20分)11.TTL电路的电源是__5__V,高电平1对应的电压范围是__2.4-5____V。

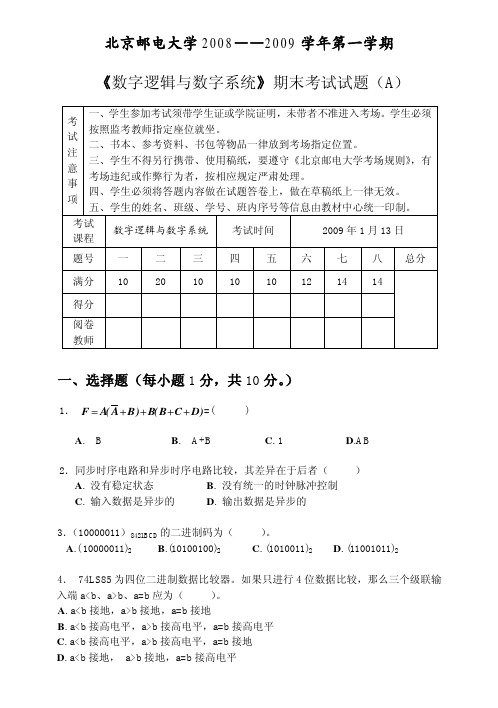

《数字逻辑与数字系统》期末考试试题(A)

北京邮电大学2008——2009学年第一学期《数字逻辑与数字系统》期末考试试题(A )考试注意事项一、学生参加考试须带学生证或学院证明,未带者不准进入考场。

学生必须按照监考教师指定座位就坐。

二、书本、参考资料、书包等物品一律放到考场指定位置。

三、学生不得另行携带、使用稿纸,要遵守《北京邮电大学考场规则》,有考场违纪或作弊行为者,按相应规定严肃处理。

四、学生必须将答题内容做在试题答卷上,做在草稿纸上一律无效。

五、学生的姓名、班级、学号、班内序号等信息由教材中心统一印制。

考试 课程 数字逻辑与数字系统 考试时间 2009年1月13日 题号 一 二 三 四 五 六 七 八 总分满分 10 20 10 10 10 12 14 14 得分 阅卷 教师一、选择题(每小题1分,共10分。

)1. )D C B (B )B A (A F ++++==( )A .B B . A+BC . 1D .AB2.同步时序电路和异步时序电路比较,其差异在于后者( ) A . 没有稳定状态 B . 没有统一的时钟脉冲控制 C . 输入数据是异步的 D . 输出数据是异步的 3.(10000011)8421BCD 的二进制码为( )。

A .( 10000011)2B .(10100100)2C . (1010011)2D . (11001011)24. 74LS85为四位二进制数据比较器。

如果只进行4位数据比较,那么三个级联输入端a<b 、a>b 、a=b 应为( )。

A . a<b 接地,a>b 接地,a=b 接地B . a<b 接高电平,a>b 接高电平,a=b 接高电平C . a<b 接高电平,a>b 接高电平,a=b 接地5. N 个触发器可以构成能寄存( )位二进制数码的寄存器。

A. NB. 2NC. 2ND. N 26.时序电路中对于自启动能力的描述是( )。

A . 无效状态自动进入有效循环,称为具有自启动能力。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

武汉大学计算机学院

2010~2011学年第二学期2010级《数字逻辑》

期未考试试卷(闭卷)A卷(A类)学号班级姓名成绩

全部答案均要求写在答题纸上,写在试卷上无效。

一、填空题(每空1分,共14分)

1.若x=-0.1011,则[x]补=()。

2.(10110.1)2=()10=()8=()16

3.8421BCD码100100010111对应的十进制数是()。

4.时序逻辑电路由()和()组成。

5.F(ABC)=AB+D

C的反函数是(),对偶函数是()。

6.欲使JK触发器在CP有效跳沿作用下的次态与现状相反,则JK的取值应为()。

7.一个矩形波信号从与非门输入端传到输出端所延迟的时间叫()。

8.消除组合逻辑电路竞争险象的常用方法有()、()、()。

二、单项选择题(每小题2分,共16分)

从下面每题的四个答案中,选择唯一正确的答案代号填入括号内。

1.在一个给定的数字波形中,其周期为脉冲宽度的两倍,则占空比为()。

A.100% B.200% C.50% D.150%

2.具有三种输出状态的门是()。

A.与门B.或门C.OC门D.三态门

3.维持阻塞D触发器是时钟的()触发的。

A.上升沿B.下降沿C.高电平D.低电平

4.电平异步时序逻辑电路的分析工具是()。

A.真值表、卡诺图B.状态表、状态图

C.功能表、波形图D.流程表、总态图

5.欲把正弦波变换为同频率的矩形波,应选择()。

A.多谐振荡器B.施密特触发器C.单稳态触发器D.J-K触发器6.对完全给定状态表中的7个状态A、B、C、D、E、F、G进行化简,若有(A、B),(B、C),(E、F)等效,则最简状态表中只有()个状态。

A.4 B.5 C.3 D.6

7.用PLA实现组合逻辑电路功能,通常要将函数表达式表示成()。

A.最小项表达式B.最简与一或式C.最大项表达式D.一般或一与式8.下列集成电路芯片中,()属于时序逻辑电路。

A.计数器74193 B.三-八译码器74138 C.多路选择器74153 D.优先编码器74148

三、化简题(8分)

用卡诺图把F(ABCD)=∑m(1,3,13,15)+∑d(6,9,11,14)化成最简与一或式。

四、分析题(每小题12分,共24分)

1.分析图示组合逻辑电路

(1)写出输出函数表达式

(2)列出真值表

(3)说明电路功能

2.分析图示同步时序逻辑电路

(1)写出激励函数表达式

(2)作状态表和状态图

(3)说明电路功能

五、设计题(14分)

用T触发器设计一个异步二位二进制(模四)加1计数器,该电路对输入端X出现的脉冲进行计数,当收到第4个脉冲时,输出Z产生进位(用Mealy模型)。

T触发器激励表如下:

六、综合应用题(每小题12分,共24分)

1.用三-八译码器74138和适当的逻辑门设计一个全加器电路(设被加数为A i,加数B i,低位进位C i-1,本位和S i,本位向高位进位C i)。

2.移位寄存器74194的引脚图和逻辑符号如下:

(1)说明它的引脚名称和功能。

(2)用74194和适当的逻辑门设计一个11101000(最先输出右边“0”位)序列发生器,循环产生该脉冲序列。

附图:。