基于FPGA的基带信号的位同步信号提取(附程序)【毕业设计论文】

一种基于FPGA的锁相环位同步提取电路设计

一种基于FPGA的锁相环位同步提取电路设计概述同步是通信系统中一个重要的问题。

在数字通信中,除了获取相干载波的载波同步外,位同步的提取是更为重要的一个环节。

因为只有确定了每一个码元的起始时刻,才能对数字信息作出正确的判决。

利用全数字锁相环可直接从接收到的单极性不归零码中提取位同步信号。

一般的位同步电路大多采用标准逻辑器件按传统数字系统设计方法构成,具有功耗大,可靠性低的缺点。

用FPGA设计电路具有很高的灵活性和可靠性,可以提高集成度和设计速度,增强系统的整体性能。

本文给出了一种基于fpga 的数字锁相环位同步提取电路。

数字锁相环位同步提取电路的原理数字锁相环位同步提取电路框本地时钟产生两路相位相差p的脉冲,其频率为fo=mrb,rb为输入单极性不归零码的速率。

输入信码的正、负跳变经过过零检测电路后变成了窄脉冲序列,它含有信码中的位同步信息,该位同步窄脉冲序列与分频器输出脉冲进行鉴相,分频比为m。

若分频后的脉冲相位超前于窄脉冲序列,则在1端有输出,并通过控制器将加到分频器的脉冲序列扣除一个脉冲,使分频后的脉冲相位退后;若分频后的脉冲相位滞后窄脉冲序列,则在2端有输出,并通过控制器将加到分频器的脉冲序列附加一个脉冲,使分频后的脉冲相位提前。

直到鉴相器的1、2端无输出,环路锁定。

基于fpga的锁相环位同步提取电路该电路如该电路由d触发器组成的二分频器和两个与门组成,它将fpga 的高频时钟信号clk_xm变换成两路相位相反的时钟信号,由e、f输出,然后送给控制电路的常开门g3和常闭门g4。

其中f路信号还作为控制器中的d1和。

基于FPGA的锁相环位同步提取电路设计

基于FPGA的锁相环位同步提取电路设计锁相环(Phase-Locked Loop,PLL)是一种广泛应用于通信、控制及信号处理等领域的电路,能够实现频率同步和相位同步。

在本文中,我们将讨论基于FPGA的锁相环位同步提取电路设计。

首先,我们将介绍锁相环的基本原理。

锁相环由相位比较器、低通滤波器、VCO(Voltage-Controlled Oscillator)和分频器组成。

相位比较器用于比较参考信号和反馈信号的相位差,将相位差转换为电压差。

低通滤波器将电压差平滑处理,得到控制电压,用于控制VCO的频率。

VCO产生与输入信号频率相同的输出信号,通过分频器将输出信号分频后与参考信号进行比较,实现频率同步。

在基于FPGA的锁相环位同步提取电路设计中,我们的目标是实现一个能够提取输入信号的位同步信息的电路,其中输入信号可能包含多个周期不同的位同步序列。

首先,我们需要设计一个相位比较器,用于比较参考信号和输入信号的相位差。

可以使用FPGA中的数字时钟管理模块来实现相位比较器,将输入信号与参考信号都映射到固定的时钟边沿上,并通过计数器测量输入信号和参考信号之间的相位差。

然后,我们需要设计一个低通滤波器,用于平滑处理相位差。

可以使用FPGA中的滑动平均滤波器来实现低通滤波器,通过对相位差进行滑动平均运算,得到平滑的控制电压。

接下来,我们需要设计一个VCO,用于产生与输入信号频率相同的输出信号。

可以使用FPGA中的数字控制模块来实现VCO,通过调节VCO的控制电压来控制输出频率。

最后,我们需要设计一个分频器,将VCO的输出信号分频后与参考信号进行比较。

可以使用FPGA中的计数器来实现分频器,通过设置分频器的计数值来实现对VCO输出信号的分频。

在整个电路设计过程中,我们需要注意以下几点:1.选择合适的时钟频率和分辨率。

时钟频率要足够高,以满足输入信号的高速采样需求。

分辨率要足够高,以保证位同步信息的精确提取。

2.选择合适的滤波器参数。

FPGA位同步信号的提取开题报告

生物医学信号的检测与处理的方法,包括在强噪声背景下对微弱生理信号的动态提取,多道生理信号的同步观察与处理,生理信号的时间―频率表示,自适应处理,医学专家系统等。另外,生物传感器输出的信号般十分微弱,需要放大。生物信号的特征部分才包含着生物信息,把这些信号的特征识别出来也是生物医学信号处理的主要任务。

制器,控制器再对分频值进行相应的调整,直到输入和输出同步为止。

2. 1m序列发生器

由于非归零码所占带宽要比归零码小一半,所以通常所使用的数据信号是非归零码。但非归零码中没有码元速率的谱线,不能直接提取出同步信号,而归零码中含有码元速率的频谱谱线,所以必须先对码序列进行非线性变换,以恢复其位同步信号之后才能用锁相环路来提取。m序列发生器就是完成非归零信号到归零信号的变换。

年月日

2012.5.1-2012.5.15完成毕业论文稿、

2012.5.16-2012.5.30修改毕业论文并稿

2012.6.1-2012.6.10准备毕业答辩的相关材料,完善毕业论文相关材料。

六、指导教师意见

1.对开题报告的评语

2.对开题报告的意见及建议

指导教师(签名):

年月日

所在院(系)审查意见:

负责人签字(盖公章)

(8)消费电子,如数字电视、高清晰度电视、数字电话、高保真音响、音乐合成等。

(9)工业控制与自动化,如油井压力测量与控制、温度控制、开关电源控制等。

其中,在通信领域的应用是十分宽广,尤其是当下移动通信技术发展,3G乃至4G技术的出现,使得数据的无线传递更加频繁,语音、图像的传输以及信息加密、信号复用等的作用也愈加显得突出。只有通过更加先进的信号分析处理技术才能使得移动通信可以以更快更安全的方式实现通信。

基于FPGA的GPS接收机位同步帧同步设计与实现

基于FPGA的GPS接收机位同步帧同步设计与实现刘成;魏可友;余金培;梁广【摘要】为了能在GPS接收端获取正确导航电文,研究了GPS接收机位同步、帧同步的基本原理和实现方式。

提出一种采用FPGA来实现位同步、帧同步系统的设计方案。

使用Xilinx开发软件,通过Verilog代码完成对位同步、帧同步的设计并在硬件平台上进行调试。

通过Chip Scope和逻辑分析仪进行验证,结果表明该设计方案正确可靠,满足设计要求。

%For obtain correct navigation message of the GPS receiver, the basic theory and implementation of GPS receiver was studied. Abit synchronization and frame synchronization is realized by using ingdevelopment software of Xilinx,by Verilog code to complete the bit synchronization and frame synchronization design and debug on the hardware platform. Validated by Chip Scope and logic analyzer, the results show that the design scheme is correct and reliable, meet the design requirement.【期刊名称】《电子设计工程》【年(卷),期】2016(000)001【总页数】3页(P156-158)【关键词】GPS接收机;位同步;帧同步;FPGA【作者】刘成;魏可友;余金培;梁广【作者单位】中国科学院上海微系统与信息技术研究所,上海 200050; 上海微小卫星工程中心,上海 201203;中国科学院上海微系统与信息技术研究所,上海200050; 上海微小卫星工程中心,上海 201203;中国科学院上海微系统与信息技术研究所,上海 200050; 上海微小卫星工程中心,上海 201203;中国科学院上海微系统与信息技术研究所,上海 200050; 上海微小卫星工程中心,上海 201203【正文语种】中文【中图分类】TN915随着空间技术的不断发展,星载GPS接收机已经逐渐发展成为航天器的一个重要平台载荷。

一种基于FPGA的位同步信号的实现

一种基于FPGA的位同步信号的实现

刘小群

【期刊名称】《新技术新工艺》

【年(卷),期】2011(000)005

【摘要】同步是通信系统中非常重要的一个实际问题,是保证整个通信系统进行有序而可靠工作的技术支撑.在数字通信系统中,除了载波同步外,还需要实现位同步.实现位同步的方法主要有滤波法和锁相法,位同步锁相法的基本原理和载波同步的原理基本类似.本文设计了一种数字锁相法位同步提取方案,分析了位同步提取原理,阐述了实现方案和模块设计的方法,在MaxplusⅡ下完成编译、综合、仿真、下载到FPGA芯片等功能.仿真及试验表明,设计稳定可靠,且能够满足要求.

【总页数】3页(P28-30)

【作者】刘小群

【作者单位】宝鸡文理学院,物理与信息技术系,陕西,宝鸡,721016

【正文语种】中文

【中图分类】TN911

【相关文献】

1.一种基于FPGA精确位同步的设计与实现 [J], 伍建辉

2.一种基于FPGA的硬件开环位同步电路设计与实现 [J], 秦文兵;罗来源;向闻

3.一种新的DTI位同步方法与FPGA实现 [J], 胡玉霞;杨志刚;胡墩

4.一种抗衰落的位同步设计和FPGA实现 [J], 刘丽哲;张德华

5.数字通信系统中位同步信号提取的FPGA实现 [J], 张礼勇;楚鹤

因版权原因,仅展示原文概要,查看原文内容请购买。

基于FPGA位同步时钟提取方案的设计

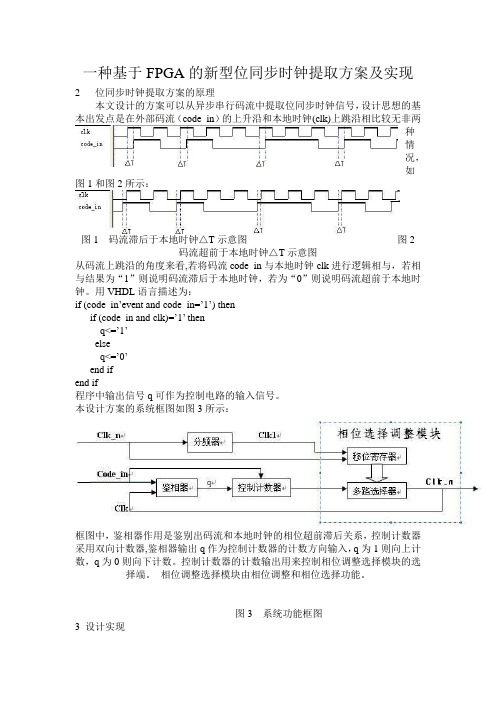

一种基于FPGA的新型位同步时钟提取方案及实现2 位同步时钟提取方案的原理本文设计的方案可以从异步串行码流中提取位同步时钟信号,设计思想的基本出发点是在外部码流(code_in)的上升沿和本地时钟(clk)上跳沿相比较无非两种情况,如图1和图2所示:图1 码流滞后于本地时钟△T示意图图2码流超前于本地时钟△T示意图从码流上跳沿的角度来看,若将码流code_in与本地时钟clk进行逻辑相与,若相与结果为“1”则说明码流滞后于本地时钟,若为“0”则说明码流超前于本地时钟。

用VHDL语言描述为:if (code_in’event and code_in=’1’) thenif (code_in and clk)=’1’ thenq<=’1’elseq<=’0’end ifend if程序中输出信号q可作为控制电路的输入信号。

本设计方案的系统框图如图3所示:框图中,鉴相器作用是鉴别出码流和本地时钟的相位超前滞后关系,控制计数器采用双向计数器,鉴相器输出q作为控制计数器的计数方向输入,q为1则向上计数,q为0则向下计数。

控制计数器的计数输出用来控制相位调整选择模块的选择端。

相位调整选择模块由相位调整和相位选择功能。

图3 系统功能框图3 设计实现依据图3系统功能框图,利用Altera 公司的Quartus II 设计软件,采用自顶向下的模块化设计方法,用VHDL 语言和电路原理图混合输入设计对位同步时钟提取电路的各个部件分别进行设计。

本设计方案的鉴相器原理相对简单,不需要用VHDL语言设计,仅用两个与门和一个D触发器就可以实现,如图4 所示。

图中的的第二个与门(inst23)是为了实现D触发器的时钟输入端与数据输入端同步。

控制计数器设计使用QuartusII的MegaWizard Plug_InManager工具来实现一个简单的双向数器,计数方向由鉴相器输出q控制,q为1则计数器向上计数,q为0则计数器向下计数,计数系数由Count Modulus设定,设定的数值要求等于分频器的分频系数N。

【开题报告】位同步技术的fpga实现开题报告

【关键字】开题报告位同步技术的fpga实现开题报告篇一:位同步的FPGA实现,论文完整打印版(XX届)本科毕业设计(论文)资料湖南工业大学教务处XX届(论文)第一部分资料毕业论文本科毕业设计(XX届)本科毕业设计(论文)XX年5月摘要同步是通信系统中很重要的一个过程,它可以使通信系统更稳定、更可靠、更准确,它是数字通信系统有顺序进行的技术支撑。

同步分为位同步、帧同步和载波同步,我们对数字通信信号的同步除了载波同步和帧同步之外,还要进行位同步。

位同步也就是保证接收端准确有效抽样判决数字基带信号序列的基础,一般位同步信号从解调后的基带信号中提取出来,同时也可以从已调频带信号当中直接提取位同步信号,一般可以进行一元中央位置采样的决定,最好是在接收元素结束时间采样的决定。

位同步有插入导频法(一种外同步法)和直接法(一种自同步法),本文运用了数字锁相法提取位同步电路的方案,以大规模可编程逻辑器件FPGA为主控制器,以VHDL硬件描述语言为主要语言对其进行在线编程,在QuartusⅡ软件工具中进行仿真和调试,以达到功耗低、成本低、效率高的技术要求。

关键词:位同步;数字锁相电路;FPGA;VHDL;QuartusⅡABSTRACTSynchronization is a very important process in communication system, it can make the system more stable, more reliable, more accurate, it is the digital communication system has the technical support of the order. Synchronization is divided into bit synchronization, frame synchronization and carrier synchronization, we on the digital communication signal in addition to frame and carrier synchronization and bit synchronization. Bit synchronization is the basis to ensure the correct and effective decision receiver sampling digital baseband signal sequence,general synchronization signal is extracted from the baseband demodulated signals, but also can directly extract bit synchronization signal from the frequency band signal has, in general can be a central position sampling decisions, preferably in the receiving elements in the end time sampling decision. Bit synchronization is the pilot insertion method (a kind of external synchronization method) and direct method (a self synchronizing method), this paper uses digital PLL method of bit synchronization circuit extraction, with the large-scale programmable logicdevice FPGA as the main controller, using the VHDL hardware description language is the main language of the online programming, simulation and debugging in QuartusⅡsoftware tools, to meet the requirements of low power consumption, low cost, high efficiency technology Keywords: Bit synchronization (symbol extraction process); digital phase locked loop circuit (bit synchronization circuit); FPGA; VHDL; QuartusⅡ篇二:FPGA位同步信号的提取开题报告本科毕业设计开题报告题目基于FPGA的基带信号的位同步电路的研究与实现学生姓名学号所在院(系)专业班级指导教师XX 年3 月18 日1234篇三:《基于FPGA的直接数字合成器设计》开题报告天津职业技术师范大学Tianjin University of Technology and Education毕业设计开题报告基于FPGA的直接数字合成器设计学院:电子工程学院班级:应电0711班学生姓名:牟玉龙指导教师:刘新月职称:讲师XX年11月22日开题报告填写要求1.开题报告作为毕业设计答辩委员会对学生答辩资格审查的依据材料之一,应在指导教师指导下,由学生在毕业设计工作前期完成,经指导教师签署意见、专家组及学院教学院长审查后生效;2.开题报告必须用黑墨水笔工整书写或按教务处统一设计的电子文档标准格式(可从教务处网页上下载)打印,禁止打印在其它纸上后剪贴;3.毕业设计开题报告应包括以下内容:(1)研究的目的;(2)主要研究内容;(3)课题的准备情况及进度计划;(4)参考文献。

基于FPGA的提取位同步时钟DPLL设计

基于FPGA的提取位同步时钟DPLL设计

叶怀胜;谭南林;苏树强;李国正

【期刊名称】《现代电子技术》

【年(卷),期】2009(32)23

【摘要】提出一种基于FPGA的用于提取位同步时钟的片内全数字锁相环电路设计方案.该方案具有同步速度快,结构简洁,失锁后自我调节性能好,即使码元消失或是码元相位出现抖动时,提取的同步时钟也不会有较大变化,仍可以稳定输出.此外,该方案可以稳定地从曼彻斯特码中提取出位时钟,指导编解码器可靠工作.采用Verilog HDL语言描述电路,给出了仿真结果,并对其稳定性和稳态误差进行了理论分析,以实际测验验证了仿真的正确性.

【总页数】4页(P43-46)

【作者】叶怀胜;谭南林;苏树强;李国正

【作者单位】北京交通大学,机电学院,北京,100044;北京交通大学,机电学院,北京,100044;北京交通大学,机电学院,北京,100044;北京交通大学,机电学院,北

京,100044

【正文语种】中文

【中图分类】TP274

【相关文献】

1.基于FPGA的人体通信中位同步提取电路的设计 [J], 王文;高跃明;陈艺东;潘少恒;麦炳源;韦孟宇;杜民

2.基于CPLD的位同步时钟提取电路设计 [J], 王志梁;刘笃仁

3.基于FPGA的锁相环位同步提取电路设计 [J], 周云水

4.基于FPGA+DDS的位同步时钟恢复设计与实现 [J], 苏淑靖;吴征

5.一种基于FPGA的位同步时钟提取电路 [J], 夏蒙;范龙飞;王富栋

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

xxxx学院毕业设计论文题目:基于单片机和FPGA的位同步信号提取专业班级:电子信息工程学生姓名:学号:完成日期:指导教师:评阅教师:2006 年6月湖南工程学院应用技术学院毕业设计(论文)诚信承诺书本人慎重承诺和声明:所撰写的《基于单片机和FPGA的位同步信号提取》是在指导老师的指导下自主完成,文中所有引文或引用数据、图表均已注解说明来源,本人愿意为由此引起的后果承担责任。

设计(论文)的研究成果归属学校所有。

学生(签名)年月日湖南工程学院应用技术学院毕业设计(论文)任务书设计(论文)题目:基于单片机和FPGA的位同步信号提取姓名专业电子信息工程班级 0281 学号 16指导老师刘正青职称实验师教研室主任刘望军一、基本任务及要求:本课题是设计一具有通用性的输入信号的位同步提取系统,系统可以实现10HZ~1MHZ的信号同步。

使用单片机进行实时控制现场可编程逻辑门阵列FPGA完成位同步信号提取,通过理论和实验研究,完成硬件电路和软件设计并试制样机,要求完成:1、单片机实时控制FPGA,完成实时频率跟踪测量和自动锁相;2、在FPGA 内部,设计完成以下部分:A、全数字锁相环DPLL,主要包含:数控振荡器、鉴相器、可控模分频器B、LED动态扫描电路、FPGA和单片机的数字接口,以完成两者之间的数字传递3、设计辅助电路:键盘、LED;二、进度安排及完成时间:(1)第二周至第四周:查阅资料、撰写文献综述和开题报告;(2)第五周至第六周:毕业实习;(3)第六周至第七周:项目设计的总体框架:各个模块以及各个模块之间的关系确定,各个模块的方案选择与各个模块的所用主要器件的确定;(4)第八周至第十三周:各个模块的主要器件熟悉及相关知识的熟悉;各个模块的具体任务实现:硬件电路、软件编程;(5)第十四周至第十五周:系统的总体仿真与调试(6)第十六周至第十七周:撰写设计说明书;(7)第十八周:毕业设计答辩;目录摘要........................................................................................................ 错误!未定义书签。

Abstract................................................................................................... 错误!未定义书签。

引言...................................................................................................... 错误!未定义书签。

第1章绪论........................................................................................ 错误!未定义书签。

1.1 位同步技术当前的发展........................................................... 错误!未定义书签。

1.2 EDA简介 (3)1.3 8051型单片机........................................................................ 错误!未定义书签。

1.4 FPGA器件简介...................................................................... 错误!未定义书签。

1.4.1 FPGA器件的发展....................................................... 错误!未定义书签。

1.4.2 FPGA器件的结构....................................................... 错误!未定义书签。

1.4.3 Altera器件及EPM7064 .............................................. 错误!未定义书签。

1.5 FPGA开发过程简介.............................................................. 错误!未定义书签。

1.6 C语言 ..................................................................................... 错误!未定义书签。

1.7 VerilogHDL ............................................................................. 错误!未定义书签。

1.8 MAX+PLUS II 概述.............................................................. 错误!未定义书签。

第2章系统组成结构.......................................................................... 错误!未定义书签。

2.1 单片机模块............................................................................... 错误!未定义书签。

2.2 键盘模块................................................................................... 错误!未定义书签。

2.3 测频、输出显示模块............................................................... 错误!未定义书签。

2.4 数字锁相环(DPLL)模块 .......................................................... 错误!未定义书签。

第3章各模块的具体设计及实现...................................................... 错误!未定义书签。

3.1 单片机模块的设计与实现....................................................... 错误!未定义书签。

3.2 键盘模块的设计与实现........................................................... 错误!未定义书签。

3.2.1 设计中问题和解决方法................................................ 错误!未定义书签。

3.2.2 键盘设计的软件设计.................................................... 错误!未定义书签。

3.3 测频、输出显示模块的设计与实现....................................... 错误!未定义书签。

3.3.1 测频部分........................................................................ 错误!未定义书签。

3.3.1.1 测频电路的设计实现......................................... 错误!未定义书签。

3.3.1.2 测频模块的软件设计......................................... 错误!未定义书签。

3.3.2 显示部分........................................................................ 错误!未定义书签。

3.3.2.1 7448芯片介绍..................................................... 错误!未定义书签。

3.4 锁相环模块的设计与实现............................................................... 错误!未定义书签。

3.4.1 鉴相器的选择................................................................ 错误!未定义书签。

3.4.2 可编程K可逆计数器的设计....................................... 错误!未定义书签。

3.4.3 I/D线路的设计............................................................ 错误!未定义书签。

3.4.4 可编程N分频器的设计............................................... 错误!未定义书签。

第4章位同步信号提取系统整体测试.............................................. 错误!未定义书签。

4.1 锁相环的仿真与测试............................................................... 错误!未定义书签。

4.2 单片机软件的测试................................................................... 错误!未定义书签。

4.3 系统的整体测试....................................................................... 错误!未定义书签。

参考文献.................................................................................................. 错误!未定义书签。

致谢...................................................................................................... 错误!未定义书签。