基于FPGA的实用多功能信号发生器的设计与制作

基于FPGA的信号发生器的设计与实现

基于FPGA的信号发生器的设计与实现作者:臧谱阳王正斌来源:《电脑知识与技术》2020年第27期摘要:该文详细介绍了一种通过DDS数字合成器技术,来实现一种频率,幅度,相位可调制的高精度信号发生器。

在FPGA中设计了串口模块和相应的解析模块向DDS发送指令,使其通过读取ROM内的波形数据存储器的数据进而实现对频率和相位的控制。

同时可以根据需要自行更换ROM内存储的波形数据,能够产生正弦波,方波,锯齿波和任意波形信号。

关键词:FPGA;DDS;信号发生器;串口;ROM中图分类号:TP311 文献标识码:A文章编号:1009-3044(2020)27-0220-02开放科学(资源服务)标识码(OSID):1 概述本系统以FPGA为核心控制器,相比于STM32系列单片机的顺序指令队列,FPGA强大的并行能力在处理模拟信号和拓展接口上效率会更高,读写速度也更快。

相比于传统C语言通过FLASH读取数组信息来获取波形数据,本系统通过读取片内ROM并结合DDS进行波形数据采集,设计方法更加简单灵活,波形的显示也会更流畅。

可以输出直流、交流等信号。

2 DDS技术原理与分析DDS(Direct Digital Synthesizer)是一种新型的频率合成技术,其主要组成部分有相位累加器,相位调制器,波形数据表和D/A转换器。

其广泛运用于通信领域,特点是波形选择范围大,可供选择带宽的范围大,可控制时间长,精度高等[1-2]。

对于信号的相位、频率、幅值均可以通过自制的波形编码生成,自由度大。

其基本结构见图1所示。

在每个时钟的上升沿时,加法器会将默认的频率控制字与同步寄存器中的相位值累加,得到的数值是由加法器和寄存器的位数决定的。

累加的值接着在第二个时钟上升沿时反馈至累加寄存器的输入端,重复与设定的频率控制字相加[3-5]。

这样,在每一个时钟周期,对设定的频率控制字不断进行线性累加,这时的累加值输出的数据就是最终处理信号的相位值,也是波形存储器的采样地址。

基于FPGA与单片机的多功能信号发生器的设计与实现

( 江西工业工程Βιβλιοθήκη 职业技术 学院, 江西超

萍乡 3 3 7 0 0 0 )

摘 要: 文章设计的多功能信号发生器> X F P G A芯片为系统核心, 利用单片机 进行系统控制, 采用液晶屏作为显示界 面, 设计的

信号发生器可以产生正弦波、 三角波、 矩形波及任意波形等信号, 并且 信号具有精度高、 频带宽、 稳定度高等特 占 ’ 。

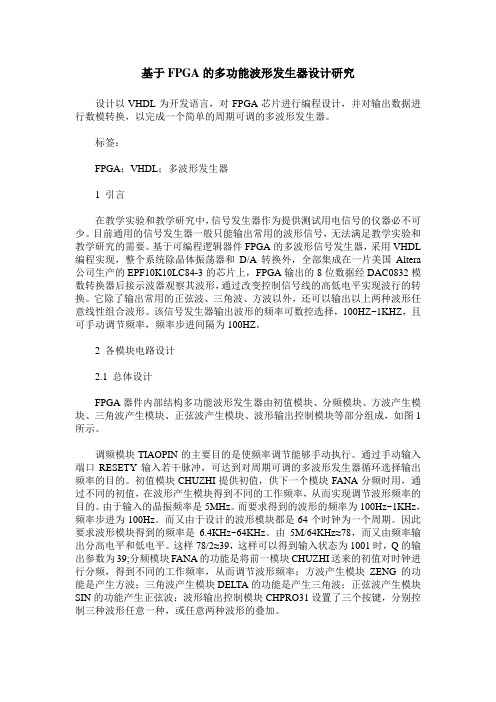

关键词 : 信号发生器; F P G A; 单片机 当前 的频率 、 波 形类 型及输入频 率、 预设波 形类 型显示 出 遥 感遥测等 众多场合 都有着广泛 的应用 , 是一种 为电子测 来 。 单片机要根据 输入 的频率值 , 计算 出相应 的频率控 制 量 工作提 供电信号的设备, 和示波器、 电压表、 频率计等仪 字, 计算的公式如下所示 : 器一样是 最基本也是应 用最广泛 的电子 仪器之一_ 】 ] 。 随着 M :盟 近 年来电子技术 的迅 猛发展 , 电子测量工作对 于包含 波形 { c 发生器在 内的电子测量 仪器 提 出了越来越 高的要求 。 为适 应 现代电子技 术的不断发展和市场需求 , 研究制作高性能 其中, 是 输出频 率 , 为F P G A,  ̄ u , 片的时钟信号, 频 率 的多功能波形发生器 十分必要。 为1 6 0 M, 相位累加器的宽度n 取值为4 0 。 1 方案比较及选择 矩阵式 键盘 l 信号发 生器主要 可 以采用两 种方案来 实现 。 一种 方案 电 源 模 块卜 _ 荜 片 机 控 制 轰 统 — 一 1 6 0 2 拉 示 是 以AD公司的直接 数字 频率合成 芯片为核心 , 通 过单片 I l 机 进 行控 制, 从而输 出信号波 形。 另一种 方案 是以现场可 F P G A核心 系统 — O A转换及放 犬 电路 编 程门阵列 ( F i e l d P r o g r a mma b l e Ga t e Ar r a y , F P G A) 芯片为核心, 采用直接 数字式频率合成器 ( Di r e c t Di g i t a l 图1 系统方块 S y n t h e s i z e r , DD S ) 技术 , 以单片机芯片为控 制器, 从而实 现波形 输出。 将 以上两 种方案 进行 比较 , 方案一 的特点是 3 . 2 基于 F P G A 的D DS 电路 频 率范 围宽、 频率 稳定 度高 、 编程 工作量较 少, 但 是只能 DDS 以高精度 时钟信号作为参 考, 经 由相位累加 器及 在正弦查找表 中找到相应的幅值信息, 通 过D / A 变 输 出正弦波和方 波且成本 较高; 方案二 的特点是频率范 围 寄存器, 再选用 低通滤 波器 , 最后输 出正 宽、 频率稳定度 较高, 不仅可输 出正弦波和 方波这两 种常 换 得到相应 的数字 信号, 用波形 , 同时还可以输 出三角波、 锯齿波及任意波形 , 且成 弦信号 。 本设计选用F P G A芯片E P 4 C 6 E 2 2 C 8 作为系 统的 核心, 该芯片的功能分成3 个模 块 : 控制逻 辑模块 、 I P 核模 本 较低 。 故本设计采用方案二来实现 。 2 系统总体设计 块及信号生成模块 。 控 制逻辑模 块主 要实现 与单片机 的通 信, 接 受单片机 本设 计 以F P G A芯片E P 4 C6 E 2 2 C8 为 核心,以单片机 传送 过 来 的4 8 位频 率控 制字 ,同时为 了增 强 系统 的稳 定 A T 8 9 S 5 1 为控制器, 通过矩 阵式键 盘进行输入输 出控制 , 在本模块采取了相应措施解决了亚稳态问题。 液 晶屏1 6 0 2 为显示界面 , 可实现 正弦波、 方 波、 三角波、 锯 性 , 齿波 及任 意波等波 形的输出, 如 图1 所 示。 本设计输 出频率 为了提高系统 的设计效率和稳定性 , 本系统选用Al t e r a P 核, 分别来产生正弦信号、 三角波信号 以及 范围为0 . 1 Hz ~ 1 0 MHz , 频率分辨率为0 . 1 Hz , 频率稳定度 公司定制好的I 任意波形信号。 方波信号通过 生产一个比较器来产生。 较高。 信 号生 产模 块是 F P G A芯片的顶 层模 块 , 在 编写代码 3 系统主要模块 电路 3 . 1单片机控制电路 的过程 中, 需将 以上 两个 模 块 例化 , 同时 该模 块 有 两 个 单片机芯片在 整个系统 中起 到控制协调 作用。 该 电路 引脚 与单 片机相 连 , 由单 片机 来控 制 最终 输 出的数 字 波 包 ̄ ' 4 X 4 矩 阵式键盘 , 通过键盘可 以输入各种频率值 , 同时 形信号。 - 3 D / A 车 等 换 电路 及 放 大电路 通 过键盘 中的控制键可 以实现整个系统的复位、 频率数 据 3 为了将F P G A 输 出的数字信号转换为模拟信号, 本 设计 的发送等操作。 单片机外围连接 了1 6 0 2 液 晶显示屏, 可以将

基于FPGA的多功能波形发生器设计研究

基于FPGA的多功能波形发生器设计研究设计以VHDL为开发语言,对FPGA芯片进行编程设计,并对输出数据进行数模转换,以完成一个简单的周期可调的多波形发生器。

标签:FPGA;VHDL;多波形发生器1 引言在教学实验和教学研究中,信号发生器作为提供测试用电信号的仪器必不可少。

目前通用的信号发生器一般只能输出常用的波形信号,无法满足教学实验和教学研究的需要。

基于可编程逻辑器件FPGA的多波形信号发生器,采用VHDL 编程实现,整个系统除晶体振荡器和D/A转换外,全部集成在一片美国Altera 公司生产的EPF10K10LC84-3的芯片上,FPGA输出的8位数据经DAC0832模数转换器后接示波器观察其波形,通过改变控制信号线的高低电平实现波行的转换。

它除了输出常用的正弦波、三角波、方波以外,还可以输出以上两种波形任意线性组合波形。

该信号发生器输出波形的频率可数控选择,100HZ~1KHZ,且可手动调节频率,频率步进间隔为100HZ。

2 各模块电路设计2.1 总体设计FPGA器件内部结构多功能波形发生器由初值模块、分频模块、方波产生模块、三角波产生模块、正弦波产生模块、波形输出控制模块等部分组成,如图1所示。

调频模块TIAOPIN的主要目的是使频率调节能够手动执行。

通过手动输入端口RESETY输入若干脉冲,可达到对周期可调的多波形发生器循环选择输出频率的目的。

初值模块CHUZHI提供初值,供下一个模块FANA分频时用,通过不同的初值,在波形产生模块得到不同的工作频率,从而实现调节波形频率的目的。

由于输入的晶振频率是5MHz。

而要求得到的波形的频率为100Hz~1KHz,频率步进为100Hz。

而又由于设计的波形模块都是64个时钟为一个周期。

因此要求波形模块得到的频率是6.4KHz~64KHz。

由5M/64KHz≈78,而又由频率输出分高电平和低电平。

这样78/2≈39,这样可以得到输入状态为1001时,Q的输出参数为39;分频模块FANA的功能是将前一模块CHUZHI送来的初值对时钟进行分频,得到不同的工作频率,从而调节波形频率;方波产生模块ZENG的功能是产生方波;三角波产生模块DELTA的功能是产生三角波;正弦波产生模块SIN的功能产生正弦波;波形输出控制模块CHPRO31设置了三个按键,分别控制三种波形任意一种,或任意两种波形的叠加。

基于FPGA的信号发生器设计

基于FPGA的信号发生器设计1 引言电子产业瞬息万变,越来越多的设计开始以ASIC转向FPGA(现场可编程门阵列),FPGA正以各种电子产品的形式进入了我们日常生活的各个角落。

随着新一代FPGA芯片工艺和设计方法的进步及新的应用领域和市场需求的变化, EDA技术有了突飞猛进的发展,数字系统设计也有了革命性的变化。

芯片的复杂程度越来越高,人们对数万门乃至数百万门设计的需求也越来越多,采用硬件描述语言VHDL的设计方式就应运而生,设计工作从行为、功能级开始,并向着设计的高层次发展。

VHDL具有多层次描述系统硬件功能的能力,支持自顶向下和基于库的设计的特点,从系统设计入手,在顶层进行系统方框图的划分和结构设计,在方框图一级用VHDL对电路的行为进行描述,并进行仿真,然后在系统一级进行验证,最后再用逻辑综合优化工具生成具体的门级逻辑电路的网表,下载到具体的FPGA器件中去,可以实现可编程的专用集成电路(ASIC)的设计。

在电子技术飞速发展的今天,信号发生器在工业、农业、生物医学等领域内,如高频感应加热、熔炼、淬火、超声诊断、核磁共振成像等,或者电路实验和设备检测中具有十分广泛的用途。

基于FPGA的信号发生器的设计,以简单、廉价的元器件构筑,能够产生高精度的正弦波、方波、三角波、锯齿波,同时可以实现波形自由选择。

本设计以花费小、集成度高、性能稳定、使用方便为指导,在功能上力求完善实用,同时兼顾商业价值与应用价值的体现。

2 设计方案2.1 方案介绍正弦波和方波使用MegaWizard Plug-In Manager定制宏功能模块,然后在顶层文件中例化。

锯齿波和三角波采用VHDL语言编程的文本输入方式。

使用分频器将输入的高频脉冲降频得到各模块所需的低频脉冲,使用四选一数据选择器选择波形的输出。

对程序进行编译仿真,成功后下载文件到FPGA实验箱来测试。

通过FPGA软件扫描方式将波形数据读出传输给DAC0832,通过外接示波器显示波形输出。

基于FPGA的多功能信号发生器的设计

电子电路设计与方案0 前言现场可编程门阵列具有运行速度快,修改灵活方便,并自带大量的输入输出端口等优点,通过FPGA实现该信号发生器的核心部件DDS模块,可以灵活地对信号发生器的参数进行调整,另外通过单片机的配合实现对其他外设电路的控制,实现信号发生器显示、参数调节等辅助的功能,通过数模转换电路和波形处理电路实现所需信号波形的输出。

本设计的主要指标为:(1)频率范围:0~1MHz,可通过键盘任意设置频率,步进1Hz。

(2)频率精度:±1%。

(3)幅值范围:±5V,可通过键盘任意设置幅度,步进100mV。

(4)幅值精度:±5%。

(5)用液晶显示所选波形名称,频率,幅值。

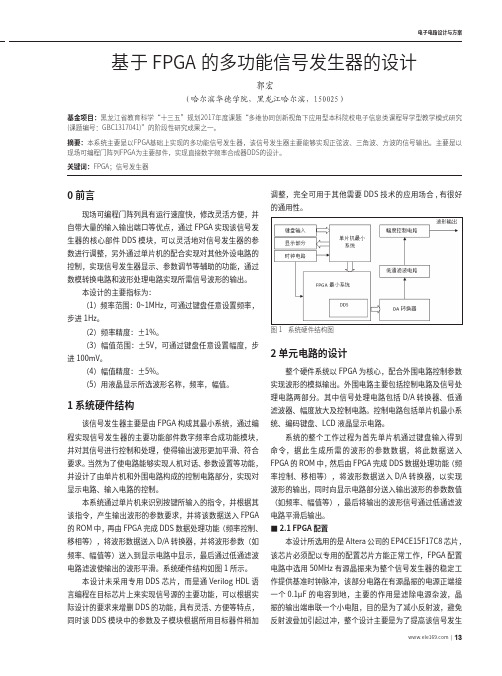

1 系统硬件结构该信号发生器主要是由FPGA构成其最小系统,通过编程实现信号发生器的主要功能部件数字频率合成功能模块,并对其信号进行控制和处理,使得输出波形更加平滑、符合要求。

当然为了使电路能够实现人机对话、参数设置等功能,并设计了由单片机和外围电路构成的控制电路部分,实现对显示电路、输入电路的控制。

本系统通过单片机来识别按键所输入的指令,并根据其该指令,产生输出波形的参数要求,并将该数据送入FPGA 的ROM中,再由FPGA完成DDS数据处理功能(频率控制、移相等),将波形数据送入D/A转换器,并将波形参数(如频率、幅值等)送入到显示电路中显示,最后通过低通滤波电路滤波使输出的波形平滑。

系统硬件结构如图1所示。

本设计未采用专用DDS芯片,而是通Verilog HDL语言编程在目标芯片上来实现信号源的主要功能,可以根据实际设计的要求来增删DDS的功能,具有灵活、方便等特点,同时该DDS模块中的参数及子模块根据所用目标器件稍加调整,完全可用于其他需要DDS技术的应用场合,有很好的通用性。

图1 系统硬件结构图2 单元电路的设计整个硬件系统以FPGA为核心,配合外围电路控制参数实现波形的模拟输出。

外围电路主要包括控制电路及信号处理电路两部分。

基于FPGA的多功能信号发生器设计与实现

基于FPGA的多功能信号发生器设计与实现刘艳昌;左现刚;李国厚【摘要】针对传统采用单片机和DDS芯片设计信号发生器的方法具有可移植性差、硬件结构和编写DDS源程序复杂等问题,提出了基于FPGA的多功能信号发生器设计方法。

采用MATLAB/Simulink和DSP Builder对DDS系统模型进行建模和仿真,并用Signal Compiler工具对模型进行编译,产生Quartus I能够识别的VHDL源程序,并在Quartus I环境中生成硬件符号,最终将顶层文件编译、综合后下载到FPGA器件中,可产生频率、幅度相位均可调的基本波、AM调制波和数字调制波。

测试结果表明,该系统具有设计灵活、实现简单、参数易调整、可移植性好、输出波形性能稳定和精度高等优点。

【期刊名称】《制造业自动化》【年(卷),期】2014(000)020【总页数】6页(P100-104,108)【关键词】FPGA;多功能信号发生器;DDS;MATLAB/DSP Builder【作者】刘艳昌;左现刚;李国厚【作者单位】河南科技学院信息工程学院,新乡453003;河南科技学院信息工程学院,新乡453003;河南科技学院信息工程学院,新乡453003【正文语种】中文【中图分类】TN91;TP3350 引言信号发生器在工业、科技、教学等领域中已得到广泛应用,通常情况下使用较多的设计方案是利用FPGA、单片机等处理器芯片来控制专用信号发生芯片,这种设计方案与传统采用模拟分立器件来设计信号发生器的方法相比,具有信号频率更稳定、精度更高、信号参数易调节等优点,但存在电路设计复杂,成本较高等问题。

随着电子技术和EDA技术的快速发展和深入研究,DDS技术得到飞速发展[1],使得信号发生器的设计和实现更加容易和灵活。

DDS即直接频率合成器,与传统频率合成技术相比,具有频率分辨率高、频率切换速度快、频率改变时相位连续性保持不变和频率稳定度高等优点,因此极易实现信号的频率、相位和幅度控制。

基于FPGA的信号发生器的设计_课程设计

郑州轻工业学院电子技术课程设计题目基于FPGA的信号发生器设计基于FPGA的函数发生器设计主要内容、基本要求、主要参考资料等:主要内容:要求学生使用硬件描述语言设计信号发生器的FPGA源程序,实现如下功能:设计智能信号发生器,要求实现正弦波、方波、三角波、递增、递减斜波和阶梯波六种波形。

基本要求:1、掌握FPGA 的程序设计方法。

2、掌握硬件描述语言语法。

3、程序设计完成后要求在软件中实现功能仿真。

主要参考资料:1、姜雪松,吴钰淳.VHDL设计实例与仿真.机械工业出版社, 2007.2、黄志伟.FPGA系统设计与实践[M].北京:电子工业出版社,2005.完成期限:2013.6.21—2013.6.25指导教师签名:课程负责人签名:2013年6月18日目录摘要 (I)1 题目分析 (1)2 方案选择 (2)2.1 波形函数发生方案对比选择 (2)2.2 波形函数输出控制方式选择 (2)3 系统细化框图 (4)4 各模块程序设计及仿真 (5)4.1 递增斜波模块 (5)4.2 递减斜波模块 (6)4.3 三角波模块 (7)4.4 阶梯波模块 (8)4.5 正弦波模块 (10)4.6 方波模块 (11)4.7 输出波形选择模块 (12)5 系统联调测试分析 (14)6 设计总结 (16)参考文献 (17)附录 (1)基于FPGA的函数发生器设计摘要随着基于CPLD的EDA技术的发展和应用领域的扩大与深入,EDA技术在电子信息、通信、自动控制及计算机等领域的重要性日益突出。

作为一个学电子信息专业的学生,我们必须不断地去了解更多的新产品信息,这就更加要求我们对EDA有个全面的认识。

信号发生器在我们的日常中有很重要的应用,用VHDL语言去实现设计将会使我们对本学科知识可以更好地掌握。

函数发生器是一种多波形的信号源,它可以产生方波、三角波、锯齿波,甚至任意波形。

本设计是一个基于VHDL的采用自顶向下设计方法实现的信号发生器,该设计方法具有外围电路简单,程序修改灵活和调试容易等特点,并通过计算机仿真和实验证明了设计的正确性。

基于FPGA的信号发生器设计

基于FPGA的信号发生器设计 以FPGA 芯片为载体,通过QuartusII 的LPM_ROM 模块和VHDL 语言为核心设计一个多功能信号发生器,根据输入信号的选择可以输出递增锯齿波、递减锯齿波、三角波、阶梯波和方波等5 种信号,通过QuartusII 软件进行波形仿真、定时分析,仿真正确后,利用实验板提供的资源,下载到芯片中实现预定功能。

信号发生器又称为波形发生器,是一种常用的信号源,广泛应用于电子电路、通信、控制和教学实验等领域。

它是科研及工程实践中最重要的仪器之一,以往多用硬件组成,系统结构比较复杂,可维护性和可操作性不佳。

随着计算机技术的发展,信号发生器的设计制作越来越多的是用计算机技术,种类繁多,价格、性能差异很大。

用FPGA 或CPLD 来实现,它的优点是可以进行功能仿真,而且FPGA 和CPLD 的片内资源丰富,设计的流程简单。

用FPGA 所构成的系统来产生波形信号,这个系统既能和主机系统相连,用相应的上层软件展示波形信号,又方便程序的编写,而且还有A/D0809接口可以产生模拟信号的输出和外面的示波器相连。

1 正弦信号发生器的LPM 定制 正弦信号发生器由计数器或地址发生器(6 位)、正弦信号数据ROM (6 位地址线,8 位数据线,含有64 个8 位数据,一个周期)、原理图顶层设计和8 位D/A (实验中用DAC0832 代替)。

其框图如图1 所示。

其中信号产生模块将产生所需的各种信号,这些信号的产生可以有多种方式,如用计数器直接产生信号输出,或者用计数器产生存储器的地址,在存储器中存放信号输出的数据。

信号发生器的控制模块可以用数据选择器实现,用8 选1 数据选择器实现对5 种信号的选择。

图1 信号发生器结构框图 最后将波形数据送入D/A 转换器,将数字信号转换为模拟信号输出。

用示波器测试D/A 转换器的输出,可以观测到5 种信号的输出。

1.1 定制初始化数据文件 QuartusII 能接受的LPM_ROM 模块中的初始化数据文件的格式有两种:。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于FPGA的实用多功能信号发生器的设计与制作基于FPGA的实用多功能信号发生器的设计与制作摘要多功能信号发生器已成为现代测试领域应用最为广泛的通用仪器之一,代表了信号源的发展方向。

直接数字频率合成(DDS)是二十世纪七十年代初提出的一种全数字的频率合成技术,其查表合成波形的方法可以满足产生任意波形的要求。

由于现场可编程门阵列(FPGA)具有高集成度、高速度、可实现大容量存储器功能的特性,能有效地实现DDS技术,极大的提高函数发生器的性能,降低生产成本。

本文首先介绍了函数信号发生器的研究背景和DDS的理论。

然后详尽地叙述了利用Verilog HDL描述DDS模块的设计过程,以及设计过程中应注意的问题。

文中详细地介绍了多种信号的发生理论、实现方法、实现过程、部分Verilog HDL代码以及利用Modelsim仿真的结果。

文中还介绍了Altera公司的DE2多媒体开发平台的部分功能及使用,并最终利用DE2平台完成了多功能信号发生器的大部分功能。

包括由LCD显示和按键输入构成的人机界面和多种信号的发生。

数字模拟转换器是BURR-BROWN 公司生产的DAC902。

该信号发生器能输出8种不同的信号,并且能对输出信号的频率、相位以及调制信号的频率进行修改设定。

关键词:信号发生器;DDS;FPGA;DE2Practical FPGA-based multi function signal generatordesign and productionAbstractMulti function signal generator has become the most widely used in modern testing field of general instrument, and has represented one of the development direction of the source. Direct digital frequency synthesis (DDS) is a totaly digital frequency synthesis technology, which been put forward in the early 1970s. Using a look-up table method to synthetic waveform, it can satisfy any requirement of waveform produce. Due to the field programmable gates array (FPGA) with high integrity, high speed, and large storage properties, it can realize the DDS technology effectively, increase signal generator’s performance and reduce production costs.Firstly, this article introduced the function signal generator of the research background and DDS theory. Then, it described how to design a DDS module by Verilog HDL, and introduced various signal occurs theory, method and the implementation process, Verilog HDL code and simulation results.This paper also introduces the function of DE2 multimedia development platform, and completed most of the functions of multi-function signal generator on DE2 platform finally. Including the occurrence of multiple signal and the man-machine interface which composed by LCD display and key input. Digital-to-analog converters is DAC902, which produced by company BURR-BROWN.This signal generator can output eight different kinds of signals, and the frequency of the output signal, phase and modulation frequency signal also can be modifyed.Key Words: Signal generator; DDS; FPGA; DE2目录论文总页数:34页1 引言 (1)1.1课题背景 (1)1.2国内外波形发生器的发展现状 (1)1.3本文研究的主要内容 (2)2 信号发生器原理 (2)2.1直接数字频率合成技术的基本原理 (2)2.2相位偏移控制 (3)2.3多种信号的发生 (3)2.3.1方波的发生 (3)2.3.2三角波发生 (4)2.2.3锯齿波发生 (4)2.3.4 PWM信号发生 (4)2.3.5 SPWM信号发生 (5)2.3.6 AM信号发生 (5)2.3.7 FM信号发生 (6)2.4DDS的特点 (7)2.4.1 DDS 的优点 (7)2.4.2 DDS 系统的缺点 (7)3 系统整体设计 (8)3.1硬件部分 (8)3.1.1 DE2实验板 (8)3.1.2 LCD模块 (9)3.1.2 DAC902 (11)3.2基于VERILOG的FPGA设计 (12)3.3软件工具 (12)3.3.1 Modelsim (12)3.3.2 Quartus (12)3.4系统设计 (13)3.4.1 系统初始化模块 (13)3.4.2按键模块和LCD模块 (13)3.4.3 RAM模块 (14)3.4.4数据转换模块 (15)3.4.5 DAC驱动模块 (15)3.4.6系统的运行 (15)4 VERILOG HDL代码实现与仿真 (15)4.1信号发生器模块 (15)4.1.1频率控制字和相位累加器 (15)4.1.2 相位偏移控制 (16)4.1.3正弦波发生模块 (17)4.1.4 方波发生模块 (17)4.1.5 三角波发生模块 (18)4.1.6 锯齿波发生模块 (18)4.1.7 PWM信号发生模块 (19)4.1.8 SPWM信号发生模块 (19)4.1.9 AM信号发生模块 (20)4.1.10 FM信号发生模块 (21)4.2按键输入模块 (22)4.3LCD显示模块 (23)4.4RAM模块 (24)4.5数据转换模块 (25)5 系统测试 (26)5.1控制及显示部分测试 (27)5.2输出频率测试 (27)5.3信号发生测试 (28)5.3.1 正弦波、方波、三角波、锯齿波测试 (28)5.3.2 PWM信号测试 (29)5.3.3 SPWM信号测试 (29)5.3.4 AM信号测试 (29)5.3.5 FM信号测试 (30)结论 (31)参考文献 (32)致谢...................................................... 错误!未定义书签。

声明...................................................... 错误!未定义书签。

1 引言1.1课题背景传统的信号发生器主要有两类:正弦波和脉冲波,而函数发生器介于两类之间。

它能够提供正弦波、余弦波、方波、三角波等几种常用标准波形,产生其它波形时,需要采用较复杂的电路和机电结合的方法。

这个时期的波形发生器多采用模拟电子技术,但是模拟器件构成的电路存在着尺寸大、价格贵、功耗大等缺点。

而且要产生的信号波形越复杂,则电路结构也会越复杂。

同时还有两个突出问题,一是通过电位器的调节来实现输出频率的调节,因此很难将频率调到某一固定值;二是脉冲的占空比不可调节。

现代科学技术的飞速发展对信号源提出了越来越高的要求。

这些要求主要表现在高分辨率、高输出频率、任意波形等方面。

此时传统的信号发生器已经无法满足要求。

直接数字频率合成[1](Direct Digital Synthesizer简称DDS)技术是一种新的全数字的频率合成原理,它从相位的角度出发直接合成所需波形。

这种技术由美国学者J.Tiercy,M.Rader和B.Gold于1971年首次提出,但限于当时的技术和工艺水平,DDS技术仅仅在理论上进行了一些探讨,而没有应用到实际中去。

但是随着电子技术的飞速发展,微处理器性能大幅提高,高速的DA以及随机存储器大量涌现,DDS技术已经变得很容易实现。

它已广泛应用于通讯、雷达、遥控测试、电子对抗以及现代化的仪器仪表工业[2]等许多领域。

将其与简单电路相结合就可以精确模拟仿真各种信号。

不论是在生产、实验还是在科研与教学上,多功能信号发生器都是用于仿真实验的最佳工具。

随着我国经济和科技的发展,对相应的测试仪器和测试手段也提出了更高的要求,多功能信号生器己成为测试仪器中至关重要的一类,因此开发多功能信号发生器具有重大意义。

1.2国内外波形发生器的发展现状早在1978年,由美国Wavetek公司和日本东亚电波工业公司公布了最高取样频率为5MHz,可以形成256点波形数据,垂直分辨率为8bit,主要用于振动、医疗、材料等领域的第一代高性能信号源。

经过将近30年的发展,伴随着电子元器件、电路、及生产设备的高速化、高集成化,信号发生器的性能有了飞速的提高。

信号发生器变得操作越来越简单而输出波形的能力越来越强。

90年代末,出现几种真正高性能、高价格的函数发生器,如HP公司推出了型号为HP770S的信号模拟装置系统。

它由HP9770A任意波形数字化和HPl776A 波形发生软件组成。

HP8770A实际上也只能产生8种波形,而且价格昂贵。

不久以后,Analogie公司推出了型号为Data-2020的多波形合成器,Lecroy公司生产的型号为9100的任意波形发生器等。

到了二十一世纪,随着集成电路技术的高速发展,出现了多种工作频率可达到GHz水平的DDS芯片,同时也推动了函数波形发生器的发展。