2选1数据选择器的VHDL描述

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

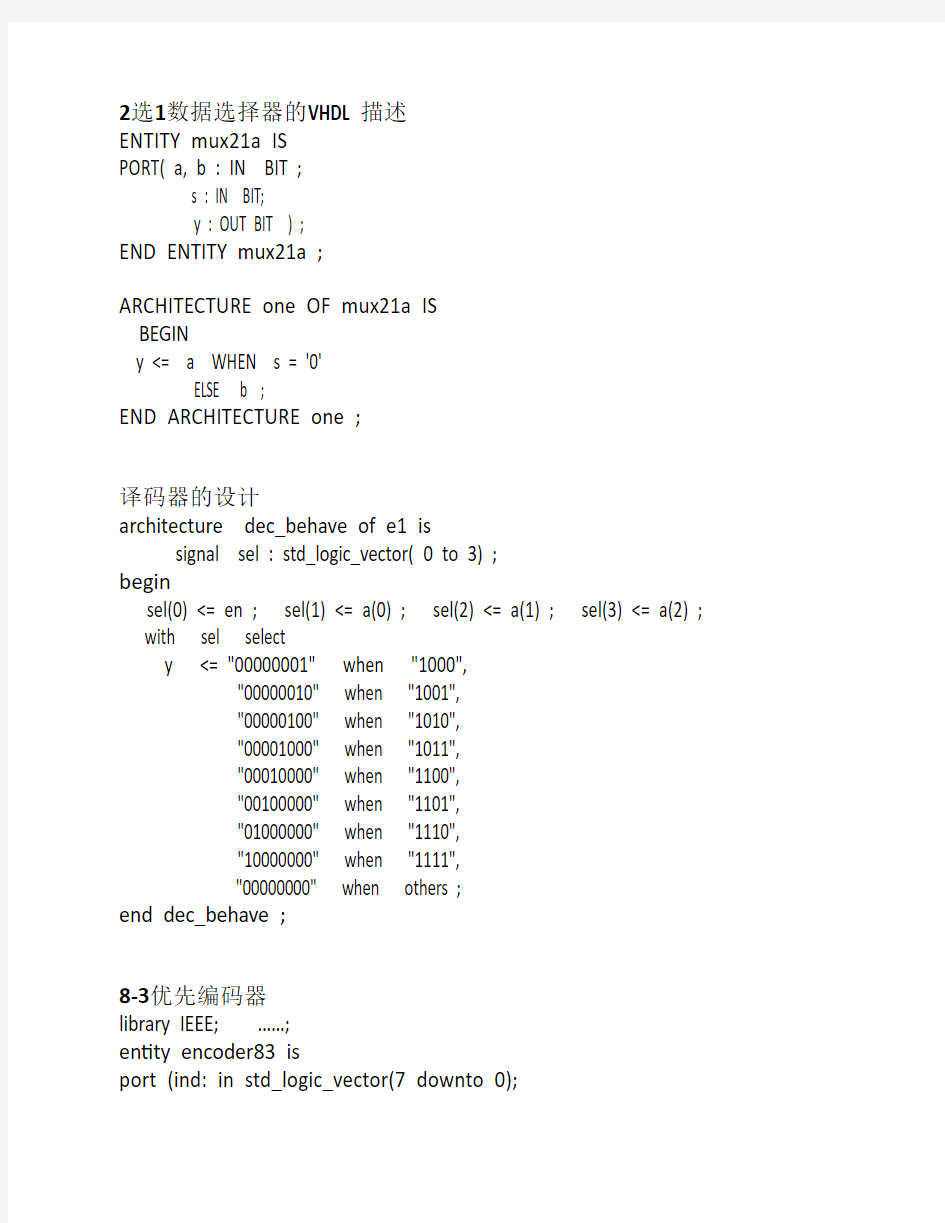

2选1数据选择器的VHDL描述

ENTITY mux21a IS

PORT( a, b : IN BIT ;

s : IN BIT;

y : OUT BIT ) ;

END ENTITY mux21a ;

ARCHITECTURE one OF mux21a IS

BEGIN

y <= a WHEN s = '0'

ELSE b ;

END ARCHITECTURE one ;

译码器的设计

architecture dec_behave of e1 is

signal sel : std_logic_vector( 0 to 3) ;

begin

sel(0) <= en ; sel(1) <= a(0) ; sel(2) <= a(1) ; sel(3) <= a(2) ; with sel select

y <= "00000001" when "1000",

"00000010" when "1001",

"00000100" when "1010",

"00001000" when "1011",

"00010000" when "1100",

"00100000" when "1101",

"01000000" when "1110",

"10000000" when "1111",

"00000000" when others ;

end dec_behave ;

8-3优先编码器

library IEEE; ……;

entity encoder83 is

port (ind: in std_logic_vector(7 downto 0);

outd: out std_logic_vector(2 downto 0)); end ;

architecture behave of encoder83 is

begin

process (ind)

begin

if ind (7) = ‘1' then outd<= "111";

elsif ind (6) = ‘1' then outd<= "110";

elsif ind (5) = ‘1' then outd<= "101";

elsif ind (4) = ‘1' then outd<= "100";

elsif ind (3 )= ‘1' then outd<= "011";

elsif ind (2) = ‘1' then outd<= "010";

elsif ind (1) = ‘1' then outd<= "001";

elsif ind (0) = ‘1' then outd<= "000";

else outd<= "000";

end if;

end process; end behave;