简易数字式频率计仿真设计

数字频率计的课设报告以及仿真电路

河北联合大学2011级本科课程设计简易数字频率计的设计姓名: 张如林学号: 201114050113班级: 11电气1班2013年12月18摘要 (1)一,概述 (2)二,方案设计 (2)1.设计题目 (2)2.设计任务和要求 (2)3.程序设计思路 (2)三,单元电路设计与Multisim仿真分析 (3)1.1Hz时基电路 (4)2.六进制计数器门控电路 (4)3.NE555施密特整形电路 (7)4.计数、锁存、驱动、显示电路 (7)5.整体仿真电路 (7)四,总原理图及元器件清单 (8)1.总原理图 (8)2.元器件清单 (9)五.结论 (10)六.心得体会 (10)七.参考文献 (11)八.附录 (12)在数字电路中,数字频率计属于时序电路,它主要由具有记忆功能的触发器构成。

在计算机及各种数字仪表中,都得到了广泛的应用。

在CMOS电路系列产品中,数字频率计是用量最大、品种很多的产品,是计算机、通讯设备、音频视频等科研生产领域不可缺少的测量仪器,并且与许多电参量的测量方案、测量结果都有十分密切的关系,在电子技术中,频率是最基本的参数之一,并且与许多电参量的测量方案、测量结果都有十分密切的关系,因此频率的测量就显得更为重要。

测量频率的方法有多种,其中电子计数器测量频率具有精度高、使用方便、测量迅速,以及便于实现测量过程自动化等优点,是频率测量的重要手段之一。

常用的频率测量方法有测频法、测周法、测周期/频率法、F/V与A/D法。

1一、概述频率是周期信号每秒钟内所含的周期数值。

输入电路:由于输入的信号可以是正弦波,方波。

而后面的闸门或计数电路要求被测信号为矩形波,所以需要设计一个整形电路则在测量的时候,首先通过整形电路将正弦波或者三角波转化成矩形波。

在整形之前由于不清楚被测信号的强弱的情况。

所以在通过整形之前通过放大衰减处理。

当输入信号电压幅度较大时,通过输入衰减电路将电压幅度降低。

当输入信号电压幅度较小时,前级输入衰减为零时若不能驱动后面的整形电路,则调节输入放大的增益时,被测信号得以放大。

简易数字频率计设计 完整版

河南科技大学课程设计说明书课程名称现代电子系统设计题目简易数字频率计设计学院__电信学院_____班级_______学生姓名____________________指导教师_________日期__2010-01-10______课程设计任务书(指导教师填写)课程设计名称现代电子系统课程设计学生姓名刘轮辉专业班级电信科071 设计题目简易数字频率计设计一、课程设计目的掌握高速AD的使用方法;掌握频率计的工作原理;掌握GW48_SOPC实验箱的使用方法;了解基于FPGA的电子系统的设计方法。

二、设计内容、技术条件和要求设计一个具有如下功能的简易频率计。

(1)基本要求:a.被测信号的频率范围为1~20kHz,用4位数码管显示数据。

b.测量结果直接用十进制数值显示。

c.被测信号可以是正弦波、三角波、方波,幅值1~3V不等。

d.具有超量程警告(可以用LED灯显示,也可以用蜂鸣器报警)。

e.当测量脉冲信号时,能显示其占空比(精度误差不大于1%)。

(2)发挥部分a.修改设计,实现自动切换量程。

b.构思方案,使整形时,以实现扩宽被测信号的幅值范围。

三、时间进度安排布置课题和讲解:1天查阅资料、设计:4天实验:3天撰写报告:2天四、主要参考文献何小艇《电子系统设计》浙江大学出版社2008.1潘松黄继业《EDA技术实用教程》科学出版社2006.10指导教师签字:2009年12月14日目录一、摘要 (4)二、系统方案论证 (4)2.1频率测量方案 (5)三、数字频率频率计的基本原理 (6)四、各个模块设计 (7)4、1 A/D模数转换模块 (8)4、2 比较模块 (9)4、3 频率和占空比测量模块 (10)五、各个模块仿真波形 (12)六、心得体会 (14)七、参考文献 (15)附录一 (16)附录二 (22)一.摘要频率计是数字电路中的一个典型应用,是计算机、通讯设备、音频视频等科研生产领域不可缺少的测量仪器,频率测量在科技研究和实际应用中的作用日益重要。

简易数字频率计设计报告

简易数字频率计设计报告目录一.设计任务和要求 (2)二.设计的方案的选择与论证 (2)三.电路设计计算与分析 (4)四.总结与心得..................................... 错误!未定义书签。

2五.附录........................................... 错误!未定义书签。

3六.参考文献....................................... 错误!未定义书签。

8一、 设计任务与要求1.1位数:计4位十进制数。

1.2.量程第一档 最小量程档,最大读数是9.999KHZ ,闸门信号的采样时间为1S. 第二档 最大读数是99.99KHZ ,闸门信号采样时间为0.1S.第三档 最大读数是999.9KHZ ,闸门信号采样时间为10mS.第四档 最大读数是9999KHZ ,闸门信号采样时间为1mS.1.3 显示方式(1)用七段LED 数码管显示读数,做到能显示稳定,不跳变。

(2)小数点的位置随量程的变更而自动移动(3)为了便于读数,要求数据显示时间在0.5-5s 内连续可调1.4具有自检功能。

1.5被测信号为方=方波信号二、设计方案的选择与论证2.1 算法设计频率是周期信号每秒钟内所含的周期数值。

可根据这一定义采用如图 2-1所示的算法。

图2-2是根据算法构建的方框图。

被测信号图2-2 频率测量算法对应的方框图 输入电路 闸门 计数电路 显示电路闸门产生整体方框图及原理频率测量:测量频率的原理框图如图2-3.测量频率共有3个档位。

被测信号经整形后变为脉冲信号(矩形波或者方波),送入闸门电路,等待时基信号的到来。

时基信号有555定时器构成一个较稳定的多谐振荡器,经整形分频后,产生一个标准的时基信号,作为闸门开通的基准时间。

被测信号通过闸门,作为计数器的时钟信号,计数器即开始记录时钟的个数,这样就达到了测量频率的目的。

周期测量:测量周期的原理框图2-4.测量周期的方法与测量频率的方法相反,即将被测信号经整形、二分频电路后转变为方波信号。

multisim简易数字频率计

m u l t i s i m简易数字频率计Company Document number:WTUT-WT88Y-W8BBGB-BWYTT-19998哈尔滨工业大学简易频率计的仿真设计目录3.电路组成介绍1.设计要求本次设计任务是要求设计一个简易的数字频率计,即用数字显示被测信号频率的仪器,数字频率计的设计指标有:1. 测量信号:正弦信号、方波信号等周期变化的物理信号;2. 测量频率范围:0Hz~9999Hz ;3. 显示方式:4位十进制数显示。

2.电路工作原理频率计总电路图如下所示:频率计的基本原理:通过将被测周期信号整形为同频率的方波信号后,利用555定时器组成的振荡电路所产生的频率为1Hz 的标准方波,作为基准时钟,与被整形后的方波信号一起经过闸门电路处理输入计数电路,再利用74LS90N 的十进制计数功能进行级联计数,计数后输入8位数据/地址锁存器74LS273N 以实现锁存和清零功能,最后输入到译码显示电路中,用BCD7段译码器显示出来,这样就实现了对被测周期信号的频率测量并显示的功能。

频率计的工作原理流程图如下所示:3.电路组成介绍脉冲形成电路脉冲形成电路由信号发生器与整形电路组成,输入信号先经过限幅器,再经过施密特触发器整形,当输入信号幅度较小时,限幅器的二极管均截止,不起限副作用。

由555组成的施密特触发器对经过限幅器的信号进行整形得到标准的方波信号。

线路图如下所示: 闸门电路闸门电路的作用是控制计数器的输入脉冲,在电路中用一个与非门来实现(如下图所标注)。

当标准信号(正脉冲)来到时闸门开通,被侧信号的脉冲通过闸门进入计时器计数;正脉冲结束时闸门关闭,计数器无时钟脉冲输入。

闸门电路时基电路时基电路是由555定时器构成的振荡器组成,其功能为产生标准时间为1秒的脉冲,=0.8Hz,其中高电平的时间为t1=1秒,低电平时间为秒。

利选取振荡器的频率f0=1t1+t2用t1=(R1+R4)C2,t2=。

简易数字频率计(数字电路课程设计)

数字电路课程设计报告1)设计题目简易数字频率计2)设计任务和要求要求设计一个简易的数字频率计,测量给定信号的频率,并用十进制数字显示,具体指标为:1)测量范围:1H Z—9.999K H Z,闸门时间1s;10 H Z—99.99K H Z,闸门时间0.1s;100 H Z—999.9K H Z,闸门时间10ms;1 K H Z—9999K H Z,闸门时间1ms;2)显示方式:四位十进制数3)当被测信号的频率超出测量范围时,报警.3)原理电路和程序设计:(1)整体电路数显式频率计电路(2)单元电路设计;(a)时基电路信号号(b)放大逻辑电路信号通信号(c)计数、译码、驱动电路号(3)说明电路工作原理;四位数字式频率计是由一个CD4017(包含一个计数器和一个译码器)组成逻辑电路,一个555组成时基电路,一个9014形成放大电路,四个CD40110(在图中是由四个74LS48、四个74LS194、四个74LS90组成)及数码管组成。

两个CD40110串联成一个四位数的十进制计数器,与非门U1A、U1B构成计数脉冲输入电路。

当被测信号从U1A输入,经过U1A、U1B两级反相和整形后加至计数器U13的CP+,通过计数器的运算转换,将输入脉冲数转换为相应的数码显示笔段,通过数码管显示出来,范围是1—9。

当输入第十个脉冲,就通过CO输入下一个CD40110的CP+,所以此四位计数器范围为1—9999。

其中U1A与非门是一个能够控制信号是否输入的计数电路闸门,当一个输入端输入的时基信号为高电平的时候,闸门打开,信号能够通过;否则不能通过。

时基电路555与R2、R3,R4、C3组成低频多谐振荡器,产生1HZ的秒时基脉冲,作为闸门控制信号。

计数公式:]3)2243[(443.1CRRRf++=来确定。

与非门U2A与CD4017组成门控电路,在测量时,当时基电路输出第一个时基脉冲并通过U2A反相后加至CD4017的CP,CD4017的2脚输出高电平从而使得闸门打开。

数字频率计设计与仿真

数字频率计设计一、实验目的1、了解等精度测频的方法和原理。

2、掌握如何在FPGA 内部设计多种功能模块。

3、掌握VHDL 在测量模块设计方面的技巧。

二、实验原理所谓频率就是周期性信号在单位时间(1s)内变化的次数。

若在一定时间间隔T(也称闸门时间)内测得这个周期性信号的重复变化次数为N,则其频率可表示为f=N/T由上面的表示式可以看到,若时间间隔T 取1s,则f=N。

由于闸门的起始和结束的时刻对于信号来说是随机的,将会有一个脉冲周期的量化误差。

进一步分析测量准确度:设待测信号脉冲周期为Tx,频率为Fx,当测量时间为T=1s时,测量准确度为δ=Tx/T=1/Fx。

由此可知这种直接测频法的测量准确度与被测信号的频率有关,当待测信号频率较高时,测量准确度也较高,反之测量准确度较低。

因此,这种直接测频法只适合测量频率较高的信号,不能满足在整个测量频段内的测量精度保持不变的要求。

若要得到在整个测量频段内的测量精度保持不变的要求,应该考虑待精度频率测量等其它方法。

等精度频率测频的实现方法,可以用图23-1 所示的框图来实现。

三、实验内容本实验要完成的任务就是设计一个频率计,系统时钟选择核心板上的20M 的时钟,闸门时间为1s(通过对系统时钟进行分频得到),在闸门为高电平期间,对输入的频率进行计数,当闸门变低的时候,记录当前的频率值,并将频率计数器清零,频率的显示每过2 秒刷新一次。

被测频率通过一个拨动开关来选择是使用系统中的数字时钟源模块的时钟信号还是从外部通过系统的输入输出模块的输入端输入一个数字信号进行频率测量。

当拨动开关为高电平时,测量从外部输入的数字信号,否则测量系统数字时钟信号模块的数字信号。

其实现框图如下图在本实验中,用到的模块有数字信号源模块、拨动开关模块、20M 系统时钟源模块、数码管显示模块等。

其中数码管、数字信号源、拨动开关与FPGA的连接电路和管脚连接在以前的实验中都做了详细说明,这里不在赘述。

简易数字频率计设计报告

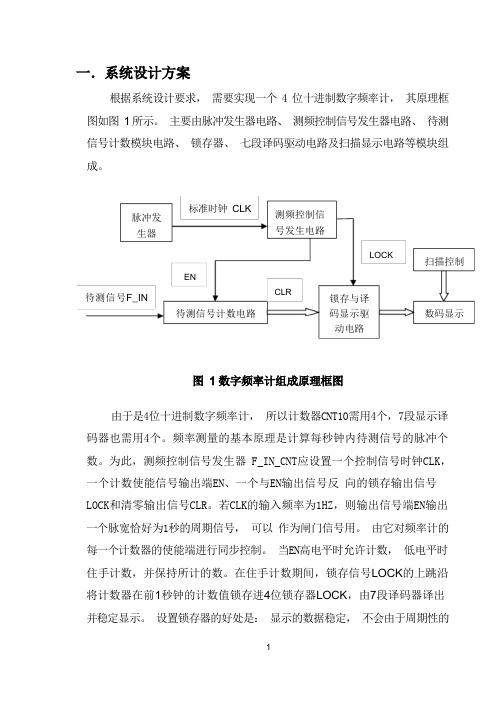

根据系统设计要求, 需要实现一个 4 位十进制数字频率计, 其原理框 图如图 1 所示。

主要由脉冲发生器电路、 测频控制信号发生器电路、 待测 信号计数模块电路、 锁存器、 七段译码驱动电路及扫描显示电路等模块组 成。

由于是4位十进制数字频率计, 所以计数器CNT10需用4个,7段显示译 码器也需用4个。

频率测量的基本原理是计算每秒钟内待测信号的脉冲个 数。

为此,测频控制信号发生器 F_IN_CNT 应设置一个控制信号时钟CLK , 一个计数使能信号输出端EN 、一个与EN 输出信号反 向的锁存输出信号 LOCK 和清零输出信号CLR 。

若CLK 的输入频率为1HZ ,则输出信号端EN 输出 一个脉宽恰好为1秒的周期信号, 可以 作为闸门信号用。

由它对频率计的 每一个计数器的使能端进行同步控制。

当EN 高电平时允许计数, 低电平时 住手计数,并保持所计的数。

在住手计数期间,锁存信号LOCK 的上跳沿 将计数器在前1秒钟的计数值锁存进4位锁存器LOCK ,由7段译码器译出 并稳定显示。

设置锁存器的好处是: 显示的数据稳定, 不会由于周期性的标准时钟 CLKEN待测信号计数电路脉冲发 生器待测信号F_INLOCK锁存与译 码显示驱 动电路测频控制信 号发生电路CLR扫描控制数码显示清零信号而不断闪烁。

锁存信号之后,清零信号CLR对计数器进行清零,为下1秒钟的计数操作作准备。

时基产生与测频时序控制电路主要产生计数允许信号EN、清零信号CLR 和锁存信号LOCK。

其VHDL 程序清单如下:--CLK_SX_CTRLLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CLK_SX_CTRL ISPORT(CLK: IN STD_LOGIC;LOCK: OUT STD_LOGIC;EN: OUT STD_LOGIC;CLR: OUT STD_LOGIC);END;ARCHITECTURE ART OF CLK_SX_CTRL ISSIGNAL Q: STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(CLK)BEGINIF(CLK'EVENT AND CLK='1')THENIF Q="1111"THENQ<="0000";ELSEQ<=Q+'1';END IF;END IF;EN<=NOT Q(3);LOCK<=Q(3)AND NOT(Q(2))AND Q(1);CLR<=Q(3)AND Q(2)AND NOT(Q(1));END PROCESS;END ART;测频时序控制电路:为实现系统功能,控制电路模块需输出三个信号:一是控制计数器允许对被测信号计数的信号EN;二是将前一秒计数器的计数值存入锁存的锁存信号LOCK;三是为下一个周期计数做准备的计数器清零信号CLR。

数字显示频率计的设计1

模拟电子技术电路设计仿真作业简易数字频率计1.问题的重述数字频率既是一种十进制数字显示被测信号频率的数字测量仪器,它的基本功能是测量正弦信号、方波信号、尖脉冲信号以及其他各种单位时间内变化的物理量,因此,它的用途十分广泛。

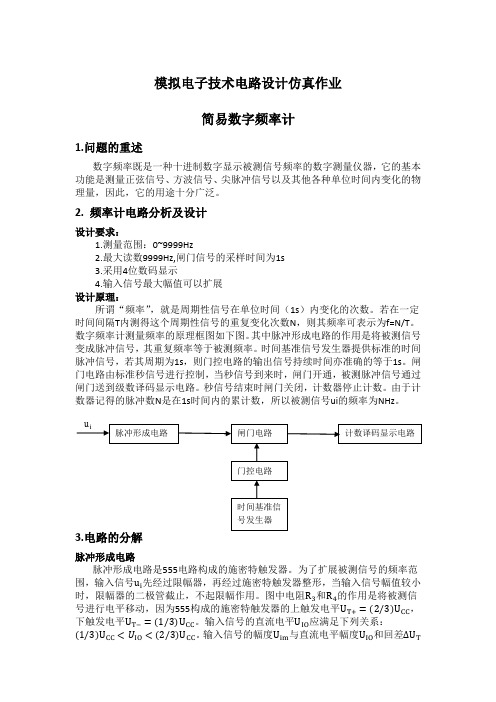

2. 频率计电路分析及设计设计要求:1.测量范围:0~9999Hz2.最大读数9999Hz,闸门信号的采样时间为1s3.采用4位数码显示4.输入信号最大幅值可以扩展设计原理:所谓“频率”,就是周期性信号在单位时间(1s)内变化的次数。

若在一定时间间隔T内测得这个周期性信号的重复变化次数N,则其频率可表示为f=N/T。

数字频率计测量频率的原理框图如下图。

其中脉冲形成电路的作用是将被测信号变成脉冲信号,其重复频率等于被测频率。

时间基准信号发生器提供标准的时间脉冲信号,若其周期为1s,则门控电路的输出信号持续时间亦准确的等于1s。

闸门电路由标准秒信号进行控制,当秒信号到来时,闸门开通,被测脉冲信号通过闸门送到级数译码显示电路。

秒信号结束时闸门关闭,计数器停止计数。

由于计数器记得的脉冲数N是在1s时间内的累计数,所以被测信号ui的频率为NHz。

脉冲形成电路脉冲形成电路是555电路构成的施密特触发器。

为了扩展被测信号的频率范围,输入信号u i先经过限幅器,再经过施密特触发器整形,当输入信号幅值较小时,限幅器的二极管截止,不起限幅作用。

图中电阻R3和R4的作用是将被测信号进行电平移动,因为555构成的施密特触发器的上触发电平U T+=(2/3)U CC,下触发电平U T−=(1/3)U CC。

输入信号的直流电平U IO应满足下列关系:(1/3)U CC<U IO<(2/3)U CC。

输入信号的幅度U im与直流电平幅度U IO和回差∆U T有关,一般来说,∆U T越小,对输入信号的幅度U im要求越小。

若取+U CC=+5V,则回差∆U T=1.67V。

若取U IO=2.5V,则取R3=R4=10kΩ,则输入信号的幅度U im=0.83V。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

简易数字频率计仿真设计报告

班级学号姓名平时成绩答辩成绩报告成绩总分122039304 杨现涛30

122039310 郭慧泽30

目录

一、设计要求 (2)

二、设计过程 (2)

三、元器件清单 (3)

四、电路连线图 (4)

放大整形电路图 (4)

单脉冲发生器电路图 (4)

闸门电路电路图 (5)

计数部分电路图 (5)

译码显示电路图 (6)

整体电路图 (7)

五、实验(仿真结果) (8)

六、出现的问题及解决方法 (8)

一)设计要求

1)设计一个单脉冲发生器,其脉冲宽度t 与手动按钮时间长短无关,与两次按钮的时间间隔无关,仅与时钟脉冲频率有关,且有下列关系:

t=1/f1

2)设计一个四位十进制计数器,实现0000-9999计数。

3)将上述两种电路图组成一个简易数字式频率计。

实现如图效果: F2 F1 0-1 1清零信号1清

11111清零清零信号

二、设计过程

根据实验要求,要完成数字式频率计的设计任务就要了解其中包含的电路以及用到的知识及元器件。

首先经过查阅资料了解数字是频率计的原理和工作过程,下面简单介绍一下数字是频率计。

数字式频率计是一种用数字显示的频率测量仪表,它不仅可以测量正弦信号、方波信号和尖脉冲信号的频率,而且还能对其他多种物频率进行测 量,诸如机械振动次数,物体转动速度,明暗变化的闪光次数,单位时间里经 过传送带的产品数量等等,这些物理量的变化情况可以有关传感器先转变成周 期变化的信号,然后用数字频率计测量单位时间内变化次数,再用数码显示出 来。

闸门电路

译码显示电路

闸门控制信号产生的电路(t )

计数电路

其次是了解本次试验设计的频率计的工作原理和具体工作过程,本次的频率计基本上与以往的频率计大同小异,首先要设计的是一个放大整形电路,通过采用555多谐振荡器件把输入到频率计的各种波形整形成标准的方波以便进行取样计数。

然后设计的是一个闸门控制信号产生电路,使其输入1hz基准频率能够产生一个脉冲宽度为1s的单脉冲,同时该电路接上一个0-1手动按钮,按下按钮该电路能够发出两种信号,一种为宽度为1s的单脉冲控制闸门的开启,开启时间为1s,另一种为清零信号,输入到计数器中,使计数器清零。

接着设计的是一个闸门电路,该闸门电路采用的是与非门,主要起到控制信号输入技术部分的作用,总体来说较为简单。

再然后设计的是计数部分,该部分采用的是4位十进制计数的方法,计数范围从0000-9999。

最后设计的是译码显示部分,该部分主要起显示频率的作用,采用的是74ls47共阴极译码器。

以上介绍的是本次设计的简要电路部分,具体电路设计以及电路图后面都有涉及到。

最后,把电路图设计出来后,就要对电路图进行接线仿真与调试过程,本次采用的仿真软件为multisim12.0,该仿真软件很好的实现了频率计的演示与仿真。

我们在此次仿真调试过程中也遇到了跟种各样的麻烦与困惑,最显著的麻烦是该软件的仿真时间与现实时间误差极大,严重影响了此次实验的进程,最后经过上网查找资料和与同学研究讨论把这个问题降到了最小程度。

后来经过了一系列的演示与调试,该频率计的功能得到了很好的实现。

三、元器件清单

七段共阴极数码管作用数量74LS47D 显示 4

74LS90D 译码 4

74LS04D 反相器 1

74LS00D 与非门 1

74LS74D D触发器 2

555 多谐振荡器 1 函数发生器产生频率 2

电容 1

电源 4

接地 3 双刀开关 1

导线若干

四、电路连线图

1、放大整形电路

该电路采用的是555多谐振荡器,并连接了电容,主要作用是整形波形,使进来的各种波形整形成标准的方波,以便计数器计数,具体图形如下图:

2、单脉冲发生器电路图

该部分电路图主要是采用了两片74LS74D系列的D触发器,将其两侧串联起来,从一个CP端输入f1=1hz的基准信号,另一CP端接0-1按钮,按下按钮,输出两种信号,一种为宽度为1s的单脉冲信号,用于开启闸门,另一种为清零信号,使计数器清零,具体电路图如下:

3、闸门电路图

该闸门电路采用的是74LS00D系列的与非门,一端接入待测信号,一段接入1s的单脉冲,主要作用是控制待测信号输入计数器。

工作原理:当1s单脉冲信号输入闸门电路时闸门打开,待测信号通过闸门进入计数器,闸门开启的时间为1s,1s过后闸门自动关闭,待测信号被阻断,计数器停止计数工作,其电路图如

下:

4、计数电路图

该部分电路图主要采用4片74LS90D系列的十进制计数器,四片十进制计数

器之间通过彼此连接,每一片的输出端都与另一片的输入端口有所连接,同时保留出清零信号端口和一个输入信号端口,以便可以输入待测信号和清零信号,主要作用是实现了4位十进制计数,计数范围从0000-9999,电路图如下:

5、译码显示电路

该部分主要采用了74LS47D共阴极译码器和七段共阴极数码管各4片,通过相互连接使晶体数码管可以显示数字,主要作用是把计数器输出的信号经过译码器译码在数码管上显示出来,显示的数字就是待测信号的频率,其电路图如下:

6、整体电路图

五、实验(仿真结果)

仿真过程中两次按下0-1手动按钮可以实现频率计的开始和清零两种功能,以待测信号f2=10hz为例,具体仿真结果见下图:

六、仿真中出现的问题及解决方法

该仿真过程中出现的问题共有三个,分别是:待测信号波形比较单一,只能是标准的方波;单脉冲发生器始终发出清零信号,造成计数器无法计数;仿真时间与现实中时间相差较大,造成个人认为仿真失败。

具体解决方法如下:为了解决待测信号波形比较单一的问题,我们小组采用了设计一种放大整形电路,即采用555多谐振荡器,把简谐波和三角波等非标准

方波的波形整形成方波波形,解决了待测信号波形单一的问题。

为了解决单脉冲发生器始终发出清零信号的问题,我们小组采用了加一组反相器的方法,把发出来的清零信号变成非清零信号,从而很好地实现了频率计的计数和清零功能。

为了解决仿真时间与现实时间差距太大的问题,我们首先通过网上查找资料,把仿真软件中的交互仿真设置中最大时间步长进行了设置,并把电压大小进行了调整,选择合适的待测频率,最终把这种差距减小到最小,以至于不会影响仿真进行的地步。