最新数字电路触发器试卷练习题

数电实验考试题及答案

数电实验考试题及答案一、选择题(每题2分,共20分)1. 在数字电路中,一个触发器的状态由其输入端的信号决定,而不受输出端的影响。

这个触发器是()。

A. RS触发器B. D触发器C. JK触发器D. T触发器答案:B2. 以下哪个不是组合逻辑电路的特点?()A. 输出只依赖于当前输入B. 输出与输入之间存在时间延迟C. 输出与输入之间没有记忆功能D. 输出状态随输入状态的变化而变化答案:B3. 在一个4位二进制计数器中,当计数器从0计数到15时,输出端Q3Q2Q1Q0的状态变化顺序是()。

A. 0000 -> 0001 -> 0010 -> 0011 -> 0100 -> 0101 -> 0110 -> 0111 -> 1000 -> 1001 -> 1010 -> 1011 -> 1100 -> 1101 -> 1110 -> 1111 -> 0000B. 0000 -> 0001 -> 0010 -> 0011 -> 0100 -> 0101 -> 0110 -> 0111 -> 1000 -> 1001 -> 1010 -> 1011 -> 1111 -> 1110 -> 1101 -> 0000C. 0000 -> 0001 -> 0010 -> 0011 -> 0100 -> 0101 -> 0110 ->0111 -> 1000 -> 1001 -> 1010 -> 1011 -> 1110 -> 1101 -> 1111 -> 0000D. 0000 -> 0001 -> 0010 -> 0011 -> 0100 -> 0101 -> 0110 -> 0111 -> 1000 -> 1001 -> 1010 -> 1011 -> 1100 -> 1101 -> 1110 -> 1111答案:A4. 以下哪个逻辑门电路可以实现异或(XOR)功能?()A. 与非门B. 或非门C. 与门D. 异或门答案:D5. 在数字电路中,一个D触发器的输出Q与输入D的关系是()。

数字电路试题及答案

数字电路试题及答案一、选择题1. 数字电路中,下列哪种逻辑门属于非门?A. 与门B. 或门C. 非门D. 异或门答案:C2. 下列哪种编码方式是唯一的一种无歧义性编码?A. 8421编码B. 2421编码C. 余3码D. 灰码答案:D3. 数字电路中,下列哪种触发器具有置位和复位功能?A. D触发器B.JK触发器C. RS触发器D. T触发器答案:C4. 数字电路中,下列哪种寄存器可以实现串行输入、串行输出?A. 移位寄存器B. 计数器C. 锁存器D. 寄存器答案:A5. 下列哪种数字电路可以实现数据的并行输入、串行输出?A. 并行输入/并行输出寄存器B. 串行输入/串行输出寄存器C. 并行输入/串行输出寄存器D. 串行输入/并行输出寄存器答案:C二、填空题6. 数字电路中的基本逻辑门有______、______、______。

答案:与门、或门、非门7. 数字电路中的组合逻辑电路有______、______、______等。

答案:编码器、译码器、多路选择器8. 数字电路中的时序逻辑电路有______、______、______等。

答案:触发器、计数器、寄存器9. 数字电路中的触发器按功能可分为______、______、______、______。

答案:RS触发器、D触发器、JK触发器、T触发器10. 数字电路中的计数器按计数方式可分为______、______。

答案:同步计数器、异步计数器三、判断题11. 逻辑门电路的输出与输入之间具有一一对应关系。

()答案:√12. 组合逻辑电路在任何时刻的输出仅取决于当时的输入信号。

()答案:√13. 时序逻辑电路的输出不仅取决于当前的输入信号,还与电路的前一个状态有关。

()答案:√14. 触发器具有记忆功能,可以存储一位二进制信息。

()答案:√15. 计数器可以用来计算输入脉冲的个数,但不能用于分频。

()答案:×(计数器也可以用于分频)四、简答题16. 简述组合逻辑电路与时序逻辑电路的区别。

触发器及时序逻辑电路考试试题(电工电子技术大学专业试卷)

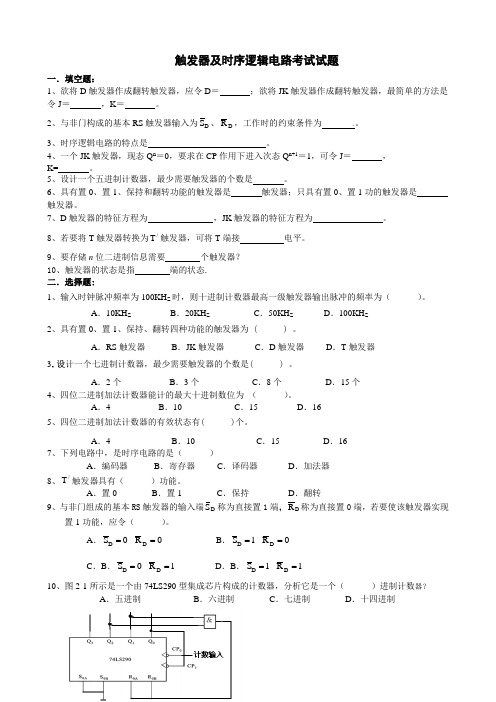

触发器及时序逻辑电路考试试题一.填空题:1、欲将D 触发器作成翻转触发器,应令D = ;欲将JK 触发器作成翻转触发器,最简单的方法是 令J = ,K = 。

2、与非门构成的基本RS 触发器输入为D S 、D R ,工作时的约束条件为 。

3、时序逻辑电路的特点是 。

4、一个JK 触发器,现态Q n =0,要求在CP 作用下进入次态Q n+1=1,可令J = , K= 。

5、设计一个五进制计数器,最少需要触发器的个数是 。

6、具有置0、置1、保持和翻转功能的触发器是 触发器;只具有置0、置1功的触发器是 触发器。

7、D 触发器的特征方程为 ,JK 触发器的特征方程为 。

8、若要将T 触发器转换为/T 触发器,可将T 端接 电平。

9、要存储n 位二进制信息需要 个触发器? 10、触发器的状态是指 端的状态. 二.选择题:1、输入时钟脉冲频率为100KH Z 时,则十进制计数器最高一级触发器输出脉冲的频率为( )。

A .10KH ZB .20KH ZC .50KH ZD .100KH Z2、具有置0、置1、保持、翻转四种功能的触发器为 ( ) 。

A .RS 触发器B .JK 触发器C .D 触发器 D .T 触发器3.设计一个七进制计数器,最少需要触发器的个数是( ) 。

A .2个B .3个C .8个D .15个 4、四位二进制加法计数器能计的最大十进制数位为 ( )。

A .4B .10C .15D .16 5、四位二进制加法计数器的有效状态有( )个。

A .4B .10C .15D .167、下列电路中,是时序电路的是( )A .编码器B .寄存器C .译码器D .加法器 8、/T 触发器具有( )功能。

A .置0B .置1C .保持D .翻转9、与非门组成的基本RS 触发器的输入端D S 称为直接置1端,D R 称为直接置0端,若要使该触发器实现置1功能,应令( )。

A .0S D = 0R D =B .1S D = 0R D =C .B .0SD = 1R D = D .B .1S D = 1R D =10、图2-1所示是一个由74LS290型集成芯片构成的计数器,分析它是一个( )进制计数器?A .五进制B .六进制C .七进制D .十四进制三、判断题:( )1、一个十进制计数器可以作为十分频器使用。

数字电路(触发器)单元测试与答案

一、单选题1、输入高有效的基本RS锁存器在使用时要尽量避免R、S输入同时为高电平(逻辑1)的组合,否则输出()。

A.状态不确定B.全1C.全0D.0态正确答案:C解析:A、只是在高电平同时撤销后的状态无法确定,因为门电路的延迟等因素。

B、基本RS锁存器由两个输入输出交叉耦合的或非门构成,输入高有效。

或非门的特性是有1出02、双稳态电路有()个稳态,可用于存储一位二进制数码。

A.0B.1C.2D.3正确答案:C3、使用基本RS锁存器(或非门构成的)时必须遵循的约束条件是(),否则会输出非法状态。

A.R+S≠2B.R+S=0C.RS=0D.R+S=2正确答案:C4、初态为1态的R̅S基本锁存器(复位、置数信号低有效),若锁存器要输出0态,输入的R̅、S可以是()。

A.R̅=0,S̅=0B. R̅=0,S̅=1C. R̅=1,S̅=0D. R̅=1,S̅=1正确答案:B解析:B、复位低有效5、基本RS锁存器加一个同步信号CP和两个()门可以实现同步信号高有效的同步RS锁存器。

A.与非B.与C.或D.或非正确答案:B6、D触发器具有数据锁存功能,如果将输入D与Q̅端相连,也可以实现()触发器的功能。

A.RSB.TC.T'D.JK正确答案:C二、多选题1、使用基本R̅S锁存器时(与非门构成的),必须遵循的约束条件是(),否则会输出非法状态。

A.输入不可以同时有效B.输入不能同时为1C.输入不能同时为0D. R̅+S̅=1正确答案:A、C、D2、初态为0态的基本RS锁存器(或非门构成的),若锁存器要继续保持0态输出,输入R、S可以是()。

A.R=0,S=0B. R=0,S=1C. R=1,S=0D. R=1,S=1正确答案:A、C3、同步D锁存器()。

A.没有复位与置数功能B.使用时没有约束条件C.对电平敏感D.有数据锁存功能正确答案:B、C、D4、4个()加一个反相器可以构成同步信号()电平有效的同步D锁存器。

数电-触发器练习题

D 翻转

单项选择题 ( )。

× √

分析提示

由JK触发器的特性方程 Qn1JQnKQn

J = 0,K = 0 时,Qn1 Qn ─ 保持功能

J = 0,K = 1 时,Qn1 0 ─ 置 0 功能

J = 1,K = 0 时,Qn1 1 ─ 置 1 功能

J

=

1,K

=

1

时,Qn1

n

Q

─ 翻转功能

第 11 页

第4页

精选2021版课件

数字电子技术

第 4 章 触发器

单项选择题

4、用与非门构成的基本RS触发器,当输入信号 S = 0、R = 1

时,其逻辑功能为

( )。

A 置1

√

B 置0

×

C 保持

×

D 不定

×

分析提示

_

Q

Q

&

&

_

_

S

R

与非门构成的 基本RS触发器

0 输入有效; R 为置 0 输入端 ,R0、 S1时,使 Qn1 0; S 为置 1 输入端 ,S0、 R1时,使 Qn1 1。

第 14 页

精选2021版课件

数字电子技术

第 4 章 触发器

2、双稳态触发器有两个基本性质,一是 。

填空题 ,二是

参考答案

有两个稳定状态 根据不同的输入信号置1或置0状态

分析提示

触发器用正反馈维持 2个稳定的输出状态0和1;在外部输入 信号作用下可置于1状态或 0状态。

第 15 页

精选2021版课件

第5页

精选2021版课件

数字电子技术

第 4 章 触发器

5、下列触发器中,输入信号直接控制输出状态的是

最新触发器练习题

触发器练习题一、填空题1、触发器具有 个稳定状态,在输入信号消失后,它能保持 。

2、在基本RS 触发器中,输入端D R 或D R 能使触发器处于 状态,输入端D S 或D S 能使触发器处于 状态。

3、同步RS 触发器状态的改变是与 信号同步的。

4、在CP 脉冲和输入信号作用下,JK 触发器能够具有 、 、 、和 的逻辑功能。

5、对于JK 触发器,当CP 脉冲有效期间,若J=K=0时,触发器状态 ;若K J =时,触发器 或 ;若J=K=1时,触发器状态 。

6、与主从触发器相比, 触发器的抗干扰能力较强。

7、对于JK 触发器,若J=K ,则可完成 触发器的逻辑功能。

8、对于JK 触发器,若K J =,则可完成 触发器的逻辑功能。

二、判断题1、触发器有两个稳定状态,一个是现态,一个是次态。

( )2、触发器有两个稳定状态,在外界输入信号的作用下,可以从一个稳定状态转变为另一个稳定状态。

( )4、同步D 触发器的Q 端和D 端的状态在任何时刻都是相同的。

( )5、同一逻辑功能的触发器,其电路结构一定相同。

( )6、仅具有反正功能的触发器是T 触发器。

( )三、选择题1、对于触发器和组合逻辑电路,以下( )的说法是正确的。

A 、两者都有记忆能力B 、两者都无记忆能力C 、只有组合逻辑电路有记忆能力D 、只有触发器有记忆能力2、对于JK 触发器,输入J=0、K=1,CP 脉冲作用后,触发器的1+n Q 应为( )。

A 、0B 、1C 、可能是0,也可能是1D 、与n Q 有关3、JK 触发器在CP 脉冲作用下,若使n n Q Q =+1,则输入信号应为( )。

A 、1==K JB 、Q K Q J ==,C 、Q K Q J ==,D 、0==K J4、具有“置0” “置1” “保持” “翻转”功能的触发器叫( )。

A 、JK 触发器B 、基本RS 触发器C 、同步D 触发器 D 、同步RS 触发器5、边沿控制触发的触发器的触发方式为( )。

触发器练习

触发器练习(一)1、画出图题5-1所示的RS 触发器输出端Q 、Q 端的波形,输入端S 与R 的波形如图所示。

(设Q 初始状态为0)S RSRSRQQ....图题5-12、画出图题5-2所示的RS 触发器输出端Q 、Q 端的波形,输入端S 与R 的波形如图所示。

(设Q 初始状态为0)S RS RQQ...SR....图题5-23、画出图题5-3所示的同步RS 触发器输出端Q 、Q 端的波形,输入端S 、R 与CLK 的波形如图所示。

(设Q 初始状态为0)C1S RS RQQ....CLKS RCLK...图题5-34、画出图题5-4所示的同步D 触发器输出Q 端的波形,输入端D 与CLK 的波形如图所示。

(设Q 初始状态为0)C1DDQQ....CLKDCLK..图题5-45、若在图5-5电路中的CP 、S 、R 输入端,加入如图4.27所示波形的信号,试画出其 Q 和Q端波形,设初态Q =0。

SRCP触发器练习(二)1、画出图题5-6所示的同步JK 触发器输出Q 端的波形,输入端J 、K 与CLK 的波形如图所示。

(设Q 初始状态为0)J KQQ..CLKJKCLK ......C11J 1K..图题5-62、画出图题5-6所示的边沿触发D 触发器输出端Q 端的波形,输入端D 与CLK的波形如图所示。

(设Q 初始状态为0)C11D D QQ....CLKDCLK...D QQ....CLKDCLK...C11D (1)(2)3、画出图题5-7所示的边沿D 触发器输出Q 端的波形,CLK 的波形如图所示。

(设Q 初始状态为0)C11D Q 1CLK....CLK.1C11D Q 2CLK .CLK .图题5-74、画出图题5-8所示的JK 触发器输出Q 端的波形,输入端J 、K 与CLK 的波形如图所示。

(设Q 初始状态为0)J KQQ....CLKJ KCLK ...C11J 1KJ KCLK ......图题5-85、试画出图题5-9所示T 触发器输出Q 端的波形,输入端CLK 的波形如图所示。

数电考试题及答案

数电考试题及答案一、单项选择题(每题2分,共20分)1. 在数字电路中,逻辑“与”运算通常使用哪种逻辑门来实现?A. 非门B. 或门C. 与门D. 异或门答案:C2. 一个触发器可以存储多少位二进制信息?A. 1位B. 2位C. 3位D. 4位答案:A3. 下列哪种类型的门电路可以实现逻辑“或非”运算?A. 与门B. 或门C. 非门D. 异或门答案:B4. 在数字电路中,一个D触发器的输出Q在时钟脉冲的上升沿时如何变化?A. 保持不变B. 翻转状态C. 变为0D. 变为1答案:B5. 一个4位二进制计数器可以计数到的最大数值是多少?A. 15B. 16C. 255D. 256答案:B6. 在数字电路中,逻辑“异或”运算通常使用哪种逻辑门来实现?A. 与门B. 或门C. 异或门D. 与非门答案:C7. 一个JK触发器在J=0,K=1时的输出Q的状态是什么?A. 保持不变B. 翻转状态C. 变为0D. 变为1答案:B8. 一个3线到8线译码器可以产生多少个不同的输出?A. 3B. 8C. 27D. 64答案:B9. 在数字电路中,一个锁存器和一个触发器的主要区别是什么?A. 锁存器可以同步操作,触发器不能B. 触发器可以同步操作,锁存器不能C. 锁存器和触发器没有区别D. 锁存器和触发器都可以异步操作答案:B10. 一个8位寄存器可以存储的最大数值是多少?A. 255B. 256C. 511D. 512答案:A二、填空题(每空1分,共10分)1. 在数字电路中,逻辑“非”运算通常使用______门来实现。

答案:非2. 一个2位二进制计数器可以计数到的最大数值是______。

答案:33. 如果一个触发器的当前状态是1,并且接收到一个时钟脉冲,那么在没有其他输入的情况下,触发器的下一个状态将是______。

答案:14. 一个4线到16线译码器的输出线数量是______。

答案:165. 在数字电路中,一个D触发器的输出Q在时钟脉冲的下降沿时______。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第一学期德清职业中专《数字电路》第二次月考试卷

(适用15计网3+2)

班级:姓名:得分:

一、填空题:(30分)

1. 触发器有两个输出端________ 和________ ,正常工作时两端的状态互补,以 ________ 的状态表示触发器的状态。

2. 按结构形式的不同,RS触发器可分为两大类:一类是没有时钟控

制的 ____________ 虫发器,另一类是具有时钟控制端的 __________ 触发器。

3. 按逻辑功能划分,触发器可以分为___________________ 触发器、

___________ 虫发器、 _________ 虫发器禾廿_______ 虫发器四种类型。

4. 钟控触发器也称同步触发器,其状态的变化不仅取决于

___________ 信号的变化,还取决于 ___________ 信号的作用。

5. 钟控触发器按结构和触发方式分,有电位触发器、___________ 虫发器、 _________ 虫发器和主从触发器四种类型。

6. 各种时钟控触发器中不需具备时钟条件的输入信号是___________ 和。

二、选择题:(20分)

1. 能够存储0、1二进制信息的器件是()

A.TTL门

B.CMOS 门

C.触发器

D. 译码器

2. 触发器是一种()

A.单稳态电路B .无稳态电路C .双稳态电路D.三稳态电路

3. 用与非门构成的基本RS触发器处于置1状态时,其输入信号

RS应为()

A. RS=OO B .RS=01 C. RS = 10 D. RS = 11

4. 用与非门构成的基本RS触发器,当输入信号S= 0、R = 1

时,其逻辑功能为()

A.置1

B. 置0

C. 保持

D. 不定

5.下列触发器中,输入信号直接控制输出状态的是()

A.基本RS触发器

B. 钟控RS触发器

C.主从JK触发器

D. 维持阻塞D触发器

6.具有直接复位端R d和置位端S d的触发器,当触发器处于受

CP 脉冲控制的情况下工作时,这两端所加的信号为()

A. R d S d =00

B. R d S d =01

C. R d S d =10

D. R d S d =11

7. 输入信号高电平有效的RS触发器中,不允许的输入是

A.RS=00

B.RS=01

C.RS=10

D.RS=11

8. 下列触发器中,具有置0、置1、保持、翻转功能的是

A. RS触发器

B. D触发器

C.JK 触发器

D. T 触发器

9. 时钟触发器产生空翻现象的原因是因为采用了(

A.主从触发方式

B. 上升沿触发方式

C.下降沿触发方式

D. 点位触发方式

10.当输入J = K = 1 时, JK触发器所具有的功能是(

A.置0

B. 置1

C. 保持

D.翻转

三、画图题:(40分)

1.如图,设Q初始状态为0, 画出Q的波形(5分)

CP 1D 、C1

2.如图,设Q初始状态为0,

CP -01J

>C1

1K

Q

3.如图,设Q初始状态为0,画出Q的波形(10分)

CP

Q

4.在虚线区域内画出RS主从触发器电路,设其输入信号CR R、S如图,触发器初始状态Q为0,试画出Q的波形图。

(20分)

四、设计题:(10分)

如图1J 、1K V D D 端接电源+V D D , R )、S D > V SS 端接地,输入CP 如下 1•试画出1Q 的波形图。

2.若要得到2Q 的输出波形,试设计合适逻辑电路,画在虚线区域内

V +V DD 1J 1Q 1K 1CP 1CP 1Q —S

R D V SS 2Q

CP

S。