ARM内存管理单元

ARM MMU L1 L2页表计算说明剖析

ARM的存储管理单元MMU知识点介绍 (1)ARM MMU 页表设置计算 (9)ARM的存储管理单元MMU知识点介绍由于ARM的MMU知识体系比较庞大,只总结必须知道了解的MMU知识点。

(一)MMU内存管理单元的作用(1)虚拟存储空间到物理存储空间的映射(2)存储器访问权限控制(3)设置虚拟存储空间的缓冲特性(二)MMU的地址变换的内存块单元(1)段单元:按大小为1M的内存块单元为单位进行的虚拟地址物理地址之间的变换。

第 1 页共47 页(2)大页单元:按大小为64K的内存块单元为单位进行的虚拟地址物理地址之间的变换。

(3)小页单元:按大小为4K的内存块单元为单位进行的虚拟地址物理地址之间的变换。

(4)极小页单元:按大小为1K的内存块单元为单位进行的虚拟地址物理地址之间的变换。

Linux在最初的汇编代码中使用段单元的映射机制来实现MMU的开启。

当Linux系统启动之后采用的是小页单元的映射机制,因为我们知道Linux把物理内存和虚拟内存的管理是按页来管理的,每个页大小为4k字节。

(三)MMU的地址变换方式(1)一级页表地址映射第 2 页共47 页一级页表地址段映射,是指按1M大小的内存块单元进行的地址映射,查找的过程就是找到页表基地址和当前需要转化的虚拟地址的高12位为索引的页目录项,由于每个目录项都是4字节对齐的,所以应该为:页表基地址+虚拟地址高12位X 4,从上图中可看出第 3 页共47 页一级描述符的地址总是4字节对齐的,即后两位为0.一级描述符地址中存放的是一级描述符,一级描述符的格式定义如下:映射实例:题目:把内存的地址从0x100000-0x200000空间映射成虚拟地址0xc0100000-0xc0200000的地址空间.(第一步)根据图1的介绍,我们先把内存虚拟地址右移20位:Table index = (0xc0100000>> 20) = 0xc01(第二步)我们打算用内存地址0x4000-0x8000的内存空间内作为存放页表的内存地址。

ARM技术概述

ARM11系列

ARM11系列处理器是针对低成本 、低功耗设备设计的,具有高性 能和出色的能效。

A系列

ARM A系列是针对高性能、低功 耗设备设计的,是大多数移动设备 的首选处理器系列。

arm编程模型

指令集架构

寄存器架构

内存管理

异常处理

ARM采用了指令集架构,将复 杂的计算机操作划分为简单、清 晰的指令,方便编程人员操作。

统的稳定性和可靠性。

04

arm技术优化与发展趋势

arm技术优化

ARMv8-A架构

采用轻量级虚拟化、多核处理器设计,支持高效的多任务处理。

内存优化

采用高速缓存、大内存等技术,提升内存读写速度,同时支持内存扩展和共享。

能源效率

采用低功耗处理器设计、能源感知技术,实现更长的电池寿命和更高效的能源利用。

05

arm技术应用案例分析

arm技术在智能手机领域的应用

智能手机市场份额

ARM在智能手机处理器市场 的份额超过90%,为全球众 多知名品牌提供技术支持和解

决方案。

高性能低功耗

ARM架构的处理器具有高性能和 低功耗的特点,使得智能手机能 够拥有更长的待机时间和更流畅 的用户体验。

异构计算

ARM通过异构计算技术,将CPU 、GPU、DSP等不同类型处理器集 成在一起,实现更高效的任务处理 。

用率和灵活性。

arm技术在物联网领域的应用

01

02

03

嵌入式系统

ARM的嵌入式系统为物 联网设备提供了稳定可靠 、低功耗、高性能的计算 平台。

低功耗设计

ARM的处理器在低功耗 设计方面具有优势,能够 满足物联网设备的长时间 运行需求。

软考中级嵌入式系统需掌握的英语词汇

软考中级嵌入式系统需掌握的英语词汇一、嵌入式系统基础1. 嵌入式系统:Embedded System2. 硬件:Hardware3. 软件:Software4. 固件:Firmware5. 系统软件:System Software6. 应用软件:Application Software7. 实时操作系统:Real-Time Operating System (RTOS)二、微控制器原理1. 微控制器:Microcontroller2. 中央处理器:Central Processing Unit (CPU)3. 存储器:Memory4. 输入/输出接口:Input/Output Interface5. 时钟系统:Clock System6. 中断:Interrupt7. 外设:Peripheral三、ARM架构与编程1. ARM架构:ARM Architecture2. ARM指令集:ARM Instruction Set3. ARM汇编语言:ARM Assembly Language4. ARM链接器:ARM Linker5. ARM工具链:ARM Toolchain6. ARM Cortex系列:ARM Cortex Series7. ARM内存管理单元:ARM Memory Management Unit (MMU)四、实时操作系统1. 实时操作系统:Real-Time Operating System (RTOS)2. 任务调度:Task Scheduling3. 信号量:Semaphore4. 消息队列:Message Queue5. 内存管理:Memory Management6. 中断处理:Interrupt Handling7. 时间管理:Time Management五、低功耗设计1. 低功耗设计:Low Power Design2. 待机模式:Standby Mode3. 休眠模式:Sleep Mode4. 唤醒机制:Wake-up Mechanism5. 能效比:Energy Efficiency Ratio6. 功率优化:Power Optimization7. 低功耗电路设计:Low Power Circuit Design六、传感器与信号处理1. 传感器:Sensor2. 模拟信号:Analog Signal3. 数字信号:Digital Signal4. 信号调理:Signal Conditioning5. 采样率:Sampling Rate6. 滤波器:Filter7. 数据转换器:Data Converter8. 信号处理算法:Signal Processing Algorithm9. 特征提取:Feature Extraction10. 信号分析:Signal Analysis11. 噪声抑制:Noise Suppression12. 数据融合:Data Fusion13. 动态范围:Dynamic Range14. 量程:Range of Measurement。

ARM处理器内核介绍

52v07 ARM普通处理器内核

TM

23

23

2.6 ARM片上总线

AMBA-Advanced Microcontroller Bus Architecture(先进 的微控制器总线体系结构)

AMBA总线定义3种规范

TM

测试芯片 ARM10200E

2

2

IP核、软核、硬核、固核

IP(Intellectual Property)就是常说的知识产权。IP定义为 用于ASIC、ASSP和PLD等当中,并且是预先设计好的电路模块。

IP核模块有行为(Behavior)、结构(Structure)和物理( Physical)三级不同程度的设计,对应描述功能行为的不同分 为三类,即软核(Soft IP Core)、完成结构描述的固核 ( Firm IP Core)和基于物理描述并经过工艺验证的硬核( Hard IP Core)。

52v07 ARM普通处理器内核

TM

18

18

ARM9TDMI 数据通道 (2)

结果 DINFWD

MU 逻辑

B 寄存器 Bank Imm BDATA 移位器

A

乘法器

ALU

PSR

ADATA

锁存

锁存

MU逻辑单元包含有:多路复用器,乘法器和桶形移位器

52v07 ARM普通处理器内核

TM

19

19

ARM9TDMI流水线的变化

52v07 ARM普通处理器内核

TM

16

16

ARM9TDMI

ARM中的一些名词

IIS(Inter-IC Sound bus)又称I2S,是菲利浦公司提出的串行数字音频总线协议。

目前很多音频芯片和MCU都提供了对IIS的支持。

IIS总线只处理声音数据。

Internet Information Services(IIS,互联网信息服务),是由微软公司提供的基于运行Microsoft Windows的互联网基本服务。

IIC是作为英特尔IC的互补,这种总线类型是由菲利浦半导体公司在八十年代初设计出来的,主要是用来连接整体电路(ICS) ,IIC是一种多向控制总线,也就是说多个芯片可以连接到同一总线结构下,同时每个芯片都可以作为实施数据传输的控制源。

这种方式简化了信号传输总线。

MCU(Micro Control Unit)中文名称为微控制单元,又称单片微型计算机(Single Chip Microcomputer)或者单片机,是指随着大规模集成电路的出现及其发展,将计算机的CPU、RAM、ROM、定时计数器和多种I/O接口集成在一片芯片上,形成芯片级的计算机,为不同的应用场合做不同组合控制。

SDRAM是Synchronous Dynamic Random Access Memory(同步动态随机存储器)的简称,SDRAM采用3.3v工作电压,带宽64位,SDRAM 将CPU与RAM通过一个相同的时钟锁在一起,使RAM和CPU能够共享一个时钟周期,以相同的速度同步工作,与EDO内存相比速度能提高50%。

SDRAM基于双存储体结构,内含两个交错的存储阵列,当CPU从一个存储体或阵列访问数据时,另一个就已为读写数据做好了准备,通过这两个存储阵列的紧密切换,读取效率就能得到成倍的提高。

SDRAM不仅可用作主存,在显示卡上的显存方面也有广泛应用。

SDRAM曾经是长时间使用的主流内存,从430TX芯片组到845芯片组都支持SDRAM。

但随着DDR SDRAM的普及,SDRAM也正在慢慢退出主流市场。

ARM 基础知识

ARM 课程考试相关知识点主要:●嵌入式系统的五个特性包括:专用性,可剪裁性,可靠性,低功耗性和实时性。

●嵌入式系统的特点:专用性强,可剪裁性好,实时性和可靠性好,功耗低●嵌入式操作系统的特点:微型化,可裁剪性,实时性,高可靠性,易移植性●嵌入式系统设计过程的主要步骤(5个):⏹1、系统需求分析⏹2、体系结构设计⏹3、硬件/软件设计⏹4、系统集成⏹5、系统测试●ARM处理器的五个系列:(体系架构是否是冯诺依曼)ARM7和ARM9的体系架构?⏹ARM7(冯诺依曼结构)⏹ARM9(哈佛体系结构)⏹ARM9E(哈佛体系结构)⏹ARM10E⏹SecurCore冯诺依曼结构指数据空间和地址空间不分开;哈佛结构数据空间和地址空间是分开的●操作系统指令执行的三个阶段⏹1、获得指令⏹2、分析指令⏹3、执行指令●代码密度:就是处理完成一个完整的操作,需要的指令条数,按字节计算越少效率越高●MMU(Memory Management Unit):存储器管理单元。

P176存储器管理单元MMU主要完成以下工作:虚拟存储空间到物理存储空间的映射;存储器访问权限的控制;设置虚拟存储空间的缓冲的特征。

MMU可以将某些地址变换条目锁定在快表【TLB(translation lookasidebuffer)】中,从而使得进行与该地址变换条目相关的地址变换速度保持很快。

MMU可以将整个存储空间分为最多16个域。

功能:将虚拟地址映射为物理地址;提供硬件机制的内存访问授权。

●ARM的寻址方式⏹立即数寻址⏹寄存器寻址⏹寄存器移位寻址⏹寄存器间接寻址⏹多寄存器寻址⏹基址变址寻址⏹相对寻址⏹堆栈寻址⏹块拷贝寻址●嵌入式系统/操作系统?主要由哪几部分组成嵌入式系统的组成部分:⏹嵌入式处理器(ARM,MIPS,PowerPC)⏹外围设备(存储器接口)⏹嵌入式操作系统⏹应用软件●ARM的最小系统,画出框图,并说明。

1. ARM芯片。

2. 电源电路、复位电路,晶振电路。

arm相关概念

arm相关概念ARM相关概念1. ARM架构简介•ARM架构是一种低功耗、高性能的处理器架构。

•ARM架构广泛应用于移动设备、嵌入式系统和智能硬件等领域。

•ARM架构采用精简指令集(RISC)的设计,具有较高的能效比和较低的功耗。

2. ARM处理器•ARM处理器是基于ARM架构设计的中央处理器(CPU)。

•ARM处理器具有多种系列和型号,包括Cortex-A系列、Cortex-R 系列和Cortex-M系列等。

•Cortex-A系列适用于高性能应用,如智能手机和平板电脑。

•Cortex-R系列适用于实时应用,如汽车电子系统和工业控制。

•Cortex-M系列适用于低功耗应用,如物联网设备和传感器。

3. ARM指令集•ARM指令集是ARM处理器所支持的指令集合。

•ARM指令集分为ARM指令集和Thumb指令集两种。

•ARM指令集提供32位的指令,适用于高性能应用。

•Thumb指令集提供16位的指令,适用于低功耗应用。

•ARM处理器可以在ARM指令集和Thumb指令集之间进行切换,以提高能效和节省存储空间。

4. ARM体系结构•ARM体系结构是指ARM处理器的整体结构和设计。

•ARM体系结构包括核心处理单元(CPU)、内存管理单元(MMU)、缓存等组件。

•ARM体系结构面向各种应用需求,提供不同级别的性能和功能选择。

•ARM体系结构允许系统设计者根据实际需求进行定制和优化。

5. ARM开发工具和平台•ARM开发工具和平台是用于开发和调试ARM架构软件的工具和环境。

•ARM开发工具包括编译器、调试器和仿真器等。

•ARM开发平台包括开发板、集成开发环境(IDE)和软件开发工具包(SDK)等。

•ARM开发工具和平台提供了丰富的开发资源,帮助开发者快速构建和优化ARM架构的应用程序。

6. ARM生态系统•ARM生态系统是指围绕ARM架构建立起来的全球化合作伙伴网络。

•ARM生态系统包括芯片厂商、设备制造商、软件开发商和解决方案提供商等。

ARM存储系统MMU

编码 0b00 0b01

访问类型 没有访问权限 客户类型

0b10 保留 0b11 管理者权限

含义 这时访问域将产生访问失效

根据页表中地址变换条目的访问权限控制位决定是否 允许特定的存储访问。 将产生不可预知的结果 不会产生访问失效

23

关于快表的操作

1. 使无效快表的内容(由CP15中的C8控制)

指令 MCR p15,0,Rd,c8,c7,0 MCR p15,0,Rd,c8,c7,1 MCR p15,0,Rd,c8,c5,0 MCR p15,0,Rd,c8,c5,1 MCR p15,0,Rd,c8,c6,0 MCR p15,0,Rd,c8,c6,1

不能访问

0b00 0 1 只读

只读

0b00 1 1 不可预测 不可预测

0b01 X X 读/写 不能访问

0b10 X X 读/写 只读

0b11 X X 读/写 读/写

22

MMU中的域

域是段、大页和小页的集合。ARM 结构支持16 个域。

对域的访问由域访问控制寄存器( CP15的寄存器C3 )的两 个位字段控制。即,C3中的每2位控制一个域的访问控制特 性。其编码及含义如下表:

Rd 0 虚拟地址 0 虚拟地址 0 虚拟地址

含义 使无效指令和数据Cache 使无效整个Cache中的单个地址变换条目 使无效指令Cache 使无效指令Cache中的单个地址变换条目 使无效数据Cache 使无效数据Cache中的单个地址变换条目

2. 锁定快表的内容(由CP15中的C10控制)

24

CP15中的寄存器C1

F(bit[10]): 由生产商定义。 Z(bit[11]): 使能跳转预测, 0 = 禁止, 1 = 使能。 I(bit[12]): 当数据和指令cache分开时,使能指令cache。 0 = 禁

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1.2.5 ARM内存管理单元

MMU是存储器管理单元的缩写,是用来管理虚拟内存系统的器件。

MMU通常是CPU 的一部分,本身有少量存储空间存放从虚拟地址到物理地址的匹配表,此表称作TLB(转换旁置缓冲区)。

所有数据请求都送往MMU,由MMU决定数据是在RAM中还是在大容量存储器设备中。

如果数据不在RAM中,MMU将产生缺页中断。

MMU的两个主要功能如下:

1.将虚地址转换成物理地址。

2.控制存储器存取允许。

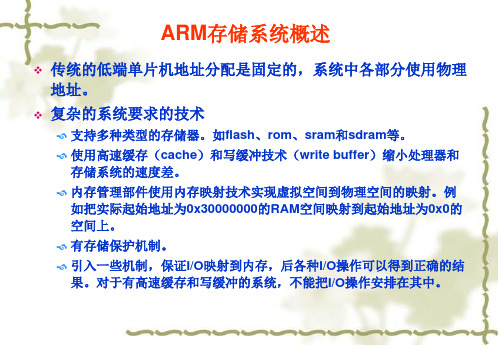

嵌入式系统中,存储系统差别很大,可包含多种类型的存储器件,如FLASH、SRAM、SDRAM、ROM等,这些不同类型的存储器件速度和宽度等各不相同;在访问存储单元时,可能采取平板式的地址映射机制对其操作,或需要使用虚拟地址对其进行读写;系统中,需引入存储保护机制,增强系统的安全性。

为适应如此复杂的存储体系要求,ARM处理器中引入了存储管理单元来管理存储系统。

在实践中,使用MMU解决了如下几个问题:

1.使用DRAM作为大容量存储器时,如果DRAM的物理地址不连续,这将给程序的编写调试造成极大不便,而适当配置MMU可将其转换成虚拟地址连续的空间。

2.ARM内核的中断向量表要求放在0地址,对于ROM在0地址的情况,无法调试中断服务程序,所以在调试阶段有必要将可读写的存储器空间映射到0地址。

3.系统的某些地址段是不允许被访问的,否则会产生不可预料的后果,为了避免这类错误,可以通过MMU匹配表的设置,将这些地址段设为用户不可存取类型。

启动程序时生成的匹配表中包含地址映射,存储页大小(1M、64K、4K)以及是否允许存取等信息。

MMU通过虚拟地址和页面表位置信息,按照转换逻辑获得对应物理地址,输出到地址总线上。

MMU的作用有两个:地址翻译和地址保护。

软件的职责是配置页表,硬件的职责是根据页表完成地址翻译和保护工作。

如果CPU没有硬件MMU,那么这张表将毫无意义。

必须从CPU的角度去理解内存映射这个概念,内存映射是CPU通过MMU把一条指令中要访问的地址转换为物理地址,然后发送到总线上的过程。

在实际的应用中,可能会把两片不连续的物理地址空间分配给SDRAM。

而在操作系统中,习惯于把SDRAM的空间连续起来,方便内存管理,且应用程序申请大块的内存时,操作系统内核也可方便地分配。

通过MMU可实现不连续的物理地址空间映射为连续的虚拟地址空间。

操作系统内核或者一些比较关键的代码,一般是不希望被用户应用程序所访问的。

通过MMU可以控制地址空间的访问权限,从而保护这些代码不被破坏。

MMU的实现过程,实际上就是一个查表映射的过程。

建立页表(translate table)是实现MMU功能不可缺少的一步。

页表位于系统的内存中,页表的每一项对应于一个虚拟地址到物理地址的映射。

每一项的长度即是一个字的长度(在ARM中,一个字的长度被定义为4字节)。

页表项除完成虚拟地址到物理地址的映射功能之外,还定义了访问权限和缓冲特性等。

MMU的映射分为两种,一级页表的变换和二级页表变换。

两者的不同之处就是所实现的变换地址空间大小不同。

一级页表变换支持1M大小的存储空间的映射,而二级可以支持64KB、4KB和1KB大小地址空间的映射。

要实现从虚拟地址到物理地址的映射,必然会遇到一个问题,如何找到这个页表。

对于

表的查找,要知道这个表的基地址和偏移地址,在具有MMU功能的处理器中,集成了一个被称为CP15的协处理器,该协处理器的C2寄存器中用于保存页表的基地址,ARM MMU执行以下一些功能,将虚拟地址转换成物理地址;控制存储访问权限;决定存储器中每一页的Cache和写缓冲器的行为。

当禁用MMU时,所有的虚拟地址一一映射到与其相同的物理地址。

如果MMU在转换一个地址时失败,就会产生一个中止异常。

MMU只有在转换失败、权限错误和域(domain)错误时,才会中止。

MMU的主要配置和控制模块如下:页表、转换旁路缓冲器、域和访问权限、Cache和写缓冲器、CP15、快速上下文切换扩展。