指令集结构及其设计

原题目:指令集体系结构的分类与比较

原题目:指令集体系结构的分类与比较引言指令集体系结构指的是计算机中用于执行指令的硬件和软件的组合方式。

不同的指令集体系结构对计算机程序的编写、执行和性能都有着不同的影响。

本文将对指令集体系结构进行分类,并对各种指令集体系结构进行比较。

指令集体系结构的分类常见的指令集体系结构主要有以下几类:1. 精简指令集(RISC)体系结构:RISC体系结构以简化指令为特点,将指令集精简为少量、固定长度的指令。

它注重简化指令的执行时间,减少指令的执行周期,以提高指令的执行效率。

常见的RISC体系结构有ARM和PowerPC等。

2. 复杂指令集(CISC)体系结构:CISC体系结构以实现复杂指令为特点,将指令集设计为丰富多样、灵活可变的指令。

它注重减少指令数量,提高编写程序的便利性,但由于指令复杂,执行时间会相对较长。

常见的CISC体系结构有x86和MIPS等。

3. 超长指令字(VLIW)体系结构:VLIW体系结构在指令流水线的基础上,通过编译器将多个指令捆绑为一条宽指令,以提高指令级并行度。

它注重编译器的优化和指令的同时执行,以提高程序的性能。

常见的VLIW体系结构有Itanium和EPIC等。

4. 特定领域指令集(DSP)体系结构:DSP体系结构主要针对数字信号处理领域的需求,将指令集设计为高度优化的专用指令,以提高数字信号处理的效率。

常见的DSP体系结构有TI TMS320和Motorola DSP等。

指令集体系结构的比较不同的指令集体系结构在性能、功耗、编程模型、兼容性等方面存在差异。

1. 性能:RISC体系结构在指令执行速度方面相对较快,适合于需要较高计算能力的应用;CISC体系结构则在编写程序的便利性和指令数量方面相对优势,适合于需要灵活指令和多功能性的应用。

2. 功耗:RISC体系结构通常具有较低的功耗,适合于功耗敏感的移动设备;CISC体系结构由于指令复杂,功耗相对较高,适合于高性能计算机系统。

3. 编程模型:RISC体系结构通常采用Load/Store指令模型,需要通过专门的Load/Store指令对寄存器和内存进行数据传输;CISC体系结构采用的是内存-寄存器指令模型,可以直接对内存进行操作。

计算机组成原理指令集体系结构的设计与优化

计算机组成原理指令集体系结构的设计与优化计算机组成原理是计算机科学中的重要理论课程之一,它对于了解计算机的基本原理和内部结构起着重要的指导作用。

其中,指令集体系结构是计算机的核心组成部分之一,它决定了计算机能够执行的操作和运算方式。

本文将探讨指令集体系结构的设计与优化方法,以及其对计算机性能的影响。

一、指令集体系结构的定义与分类指令集体系结构是计算机硬件与软件之间的接口,它定义了计算机能够执行的指令和数据格式。

根据指令和数据的操作类型,指令集体系结构可以分为以下几类:1. 精简指令集(RISC)体系结构精简指令集体系结构采用简单的指令格式和操作方式,指令集的种类较少,每条指令的执行时间相对较短。

精简指令集体系结构的设计目标是提高指令执行速度和功耗效率,适用于大部分应用场景。

2. 复杂指令集(CISC)体系结构复杂指令集体系结构采用复杂的指令格式和操作方式,指令集的种类繁多,每条指令的执行时间相对较长。

复杂指令集体系结构的设计目标是提供更丰富的指令功能和编程灵活性,适用于特定应用场景。

3. 隐式数据流(VLIW)体系结构隐式数据流体系结构将多条指令捆绑在一起,共同操作一组数据,以提高指令级并行性。

隐式数据流体系结构的设计目标是充分利用硬件资源,提高指令的并行度和执行效率,适用于科学计算和嵌入式系统等领域。

二、指令集体系结构的设计原则指令集体系结构的设计涉及到多个方面的考虑,以下是一些常见的设计原则:1. 简洁性指令集应该尽量简洁,避免冗余和重复的操作。

简洁的指令集可以提高指令的执行效率和编程的方便性。

2. 完整性指令集应该具备足够的操作功能,能够满足各类应用的需求。

完整的指令集可以提高程序的编写效率和计算机的应用范围。

3. 兼容性指令集应该具备一定的兼容性,能够支持历史上的指令集和软件。

兼容的指令集可以方便用户迁移和使用已有的软件资源。

4. 可扩展性指令集应该具备一定的扩展性,能够支持后续的技术发展和硬件升级。

三章指令集结构 PPT资料共77页

指令集表征着计算机的基本功能和使用属性,是计 算机系统设计中的核心向题。是表征一台计算机性能的 重要因素,它的格式与功能不仅直接影响到机器的硬件 结构,而且也直接影响到系统软件,影响到机器的适用 范围。

2. 指令的组成

◆ 一条指令一般应包含如下信息:

(1) 操作码

(2) 操作数的地址

(3) 操作结果的地址

二、指令的操作码

指令系统中的每一条指令都有唯一确定的操作码。 操作码位数取决于机器指令系统的规模。 1.固定长度操作码

操作码的长度固定,且集中放在指令字的一 个字段中,其余部分全部用于地址码。 此方式有利于简化硬件设计和减少指令译码 时间,用于字长较长的大、中型及超级小型机中。

2.可变长度操作码 操作码的长度允许有几种不同的选择,对地址

量不断扩大,要寻址整个主存空间,将造成指令长度 加长。另外程序位置受到限制。

3.2.3.2 间接寻址 指令中指定的是含有操作数地址的内存单元的地址。 至少要进行两次内存访问。

…

例如:LDAC 5 或 LDAC (5) IR OP … 5

5 操作数的地址10

10 操作数35

◆ 间接寻址的特点 ① 间接寻址比直接寻址灵活,可扩大寻址范围,以短

例如: Intel 8086指令 MOV AL,[BX+4]

设 BX=2000H,BX+4=2019H (2019H)=82H,则 AL←82H

例如: LDAC 5(X) ;变址寄存器X:数值10,则 5+10=15 ;读取15号单元中的数据并且把它存储在累加器中。

◆ 变址寻址可用于数组、向量、字符串等数据的处理 例: Intel 8086指令 LODS ;AL←(SI),SI←SI+1

(4) 下一条指令地址

海思架构指令集-概述说明以及解释

海思架构指令集-概述说明以及解释1.引言1.1 概述海思架构指令集是一种针对海思(Hisilicon)处理器设计的指令集架构,旨在提高处理器性能和能效。

在当今信息技术快速发展的时代,处理器性能和能效是物联网、人工智能、云计算等领域不可或缺的关键因素。

因此,海思架构指令集的设计在当前技术环境中具有重要意义。

本文将介绍海思架构指令集的简介、特点以及应用领域,通过对其优势的总结和未来发展的展望,希望可以为读者们更全面地了解海思架构指令集,同时为该领域的前沿技术发展提供一定的参考和启发。

1.2 文章结构文章结构部分主要是为了引导读者对整篇文章有一个清晰的了解,为他们提供一个阅读指南。

本文的结构主要分为引言、正文和结论三个部分。

在引言部分,将介绍文章的背景和目的,让读者对海思架构指令集有一个整体的认识。

在正文部分,将分为三个子部分进行详细介绍,包括海思架构的简介、指令集特点以及应用领域。

在结论部分,将总结海思架构的优势、展望未来发展,并进行结语。

通过以上结构的设计,希望读者能够清晰地了解海思架构指令集的相关内容,从而更好地理解和了解这一领域的知识。

1.3 目的本文旨在深入探讨海思架构指令集,探究其特点及应用领域,帮助读者更加全面地了解海思架构在计算机领域的重要性和价值。

通过对海思架构的介绍和分析,读者可以更好地理解其优势和特点,为海思架构的应用提供一定的参考和指导。

同时,本文还旨在展望海思架构未来的发展方向,探讨其在未来的应用前景和潜力,为相关从业者和研究人员提供有益的参考和借鉴。

希望通过本文的阐述,读者可以对海思架构有一个更加深刻的认识,进一步推动海思架构在计算机领域的发展和应用。

2.正文2.1 海思架构简介海思架构是由华为海思半导体有限公司设计的一种高性能处理器架构,主要用于移动通信领域。

海思架构采用了先进的多核技术和高效能的指令集,使其在处理复杂计算任务时具有出色的性能表现。

海思架构在设计上充分考虑了功耗和性能的平衡,采用了节能技术和高效的数据处理方式,使得其在移动设备上运行时能够提供较低的功耗和较高的性能。

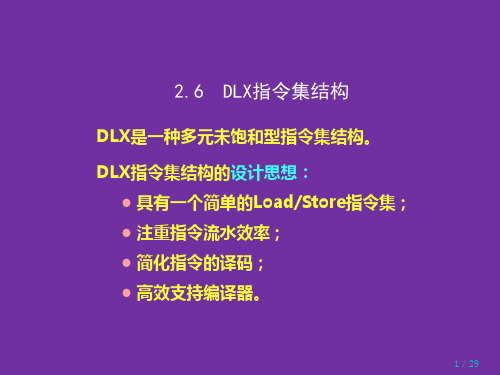

DLX指令集结构

0.1%

8.3% 1.3%

12.4% 6.8%

li 31.3% 16.7% 11.1%

5.4% 2.4%

整型平均 26% 9% 14% 0% 0% 0% 13% 3%

21/29

指令

compress eqntott Espresso gcc(cc1)

条件分支

17.4%

24.0%

15.0%

11.5%

无条件分支

含义 载入字节,载入无符号字节,储存字节

LH,LHU,SH

载入半字,载入无符号半字,储存半字

LW,SW

载入字,储存字

LF,LD,SF,SD MOVI2S,MOVS2I MOVF,MOVD MOVFP2I,MOVI2FP

载入单精度浮点,载入双精度浮点,储存单 精度浮点,储存双精度浮点

将通用寄存器中的内容移入特殊寄存器,将 特殊寄存器中的内容移入通用寄存器

2/29

◆ 64位双精度浮点数 相邻两个浮点寄存器奇偶对FiFi+1 (i = 0,2,4,,30) 命名: F0、F2、、F28、F30

(3) 一些特殊的寄存器 (比如用来保存浮点操作结果信息的浮点状态寄存器)

可以和通用寄存器相互进行数据传送。

3/29

2. DLX的数据类型 DLX提供了多种长度的整型数据和浮点数据。

(1) 整型数据 有8位、16位和32位多种长度。 (当8位和16位整型数据载入到寄存器中时, 用0或数据的符号位来填充32位通用寄存器 中的剩余位。)

(2) 浮点数据 有32位单精度浮点数和64位双精度浮点数。 浮点数据表示采用的是IEEE 754标准。

4/29

3. DLX的寻址方式和数据传送 (1) 寻址方式 寄存器寻址 立即值寻址 偏移寻址 寄存器间接寻址 (2) 寄存器寻址字段的大小为5位,用来表示32个 通用寄存器或浮点寄存器。 (3) 存储器地址采用的是高端字节表示顺序,存 储器按字节寻址,其地址宽度为32位。

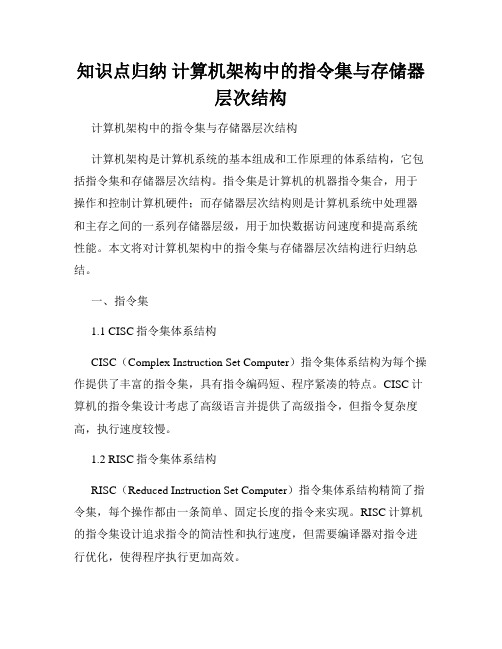

知识点归纳 计算机架构中的指令集与存储器层次结构

知识点归纳计算机架构中的指令集与存储器层次结构计算机架构中的指令集与存储器层次结构计算机架构是计算机系统的基本组成和工作原理的体系结构,它包括指令集和存储器层次结构。

指令集是计算机的机器指令集合,用于操作和控制计算机硬件;而存储器层次结构则是计算机系统中处理器和主存之间的一系列存储器层级,用于加快数据访问速度和提高系统性能。

本文将对计算机架构中的指令集与存储器层次结构进行归纳总结。

一、指令集1.1 CISC指令集体系结构CISC(Complex Instruction Set Computer)指令集体系结构为每个操作提供了丰富的指令集,具有指令编码短、程序紧凑的特点。

CISC计算机的指令集设计考虑了高级语言并提供了高级指令,但指令复杂度高,执行速度较慢。

1.2 RISC指令集体系结构RISC(Reduced Instruction Set Computer)指令集体系结构精简了指令集,每个操作都由一条简单、固定长度的指令来实现。

RISC计算机的指令集设计追求指令的简洁性和执行速度,但需要编译器对指令进行优化,使得程序执行更加高效。

1.3 x86指令集x86指令集是当前主流的个人计算机指令集,其结构可以看作是CISC和RISC的混合形式。

x86指令集保留了一部分CISC指令,同时加入了一些RISC特性,以提高指令执行的效率。

二、存储器层次结构2.1 高速缓存(Cache)高速缓存是存储器层次结构中最接近处理器的一级缓存,用于存放处理器频繁访问的数据和指令。

高速缓存分为L1缓存和L2缓存,其中L1缓存位于处理器内部,速度最快,容量较小;L2缓存位于处理器外部,速度较慢,容量较大。

2.2 主存(Main Memory)主存是计算机中用于存储程序和数据的主要存储器,也是计算机存储器层次结构中相对较慢的部分。

主存的存取速度相对较慢,但容量较大。

2.3 辅助存储器辅助存储器用于存储程序和数据的永久性存储,通常采用磁盘、固态硬盘或者磁带等形式。

指令系统结构设计

指令系统结构设计一、引言现代科技的发展使得人与机器之间的交流变得越来越频繁,指令系统作为人与机器之间的桥梁,起着至关重要的作用。

本文将从指令系统的定义、结构和设计原则等方面进行论述,旨在探讨如何设计一个高效、可靠的指令系统。

二、指令系统的定义指令系统是计算机硬件和软件之间的接口,它规定了计算机处理器执行的指令的格式、操作码和操作数的含义以及执行指令的控制流程。

指令系统可以看作是计算机的"语言",它通过指令的组合和执行来完成各种任务。

三、指令系统的结构指令系统的结构包括指令的分类、指令的格式和指令的执行方式。

1. 指令的分类指令可以分为数据传输指令、算术运算指令、逻辑运算指令、控制转移指令等。

数据传输指令用于在寄存器和内存之间传输数据;算术运算指令用于进行数值计算;逻辑运算指令用于进行逻辑运算(如与、或、非等);控制转移指令用于改变程序的执行顺序。

2. 指令的格式指令的格式包括操作码、操作数和寻址方式等。

操作码用于指定指令的类型,操作数用于指定指令的操作对象,寻址方式用于指定操作数的地址计算方式。

3. 指令的执行方式指令的执行方式包括顺序执行、条件执行和并行执行等。

顺序执行是指按照指令的顺序依次执行;条件执行是指根据条件判断是否执行某条指令;并行执行是指同时执行多条指令。

四、指令系统的设计原则1. 简洁性指令系统应该尽量简洁,避免不必要的复杂性。

简洁的指令系统可以提高程序的执行效率,减少硬件成本。

2. 完备性指令系统应该具备足够的功能,能够支持各种常见的操作。

完备的指令系统可以满足用户的各种需求,提高计算机的通用性。

3. 易于理解和使用指令系统应该易于理解和使用,用户可以通过简单的指令就能完成复杂的操作。

易于理解和使用的指令系统可以降低用户的学习成本,提高用户的工作效率。

4. 高效性指令系统应该尽量提高程序的执行效率,减少指令的执行时间和资源的消耗。

高效的指令系统可以提高计算机的运行速度,提高计算机的工作效率。

复杂指令集和精简指令集

复杂指令集和精简指令集指令集是计算机体系结构的重要组成部分,它是计算机执行程序的指令集合,包括操作码和操作数等元素。

指令集的设计和选择对计算机的性能、成本和可移植性等方面有很大的影响。

主要有两种指令集架构:复杂指令集(Complex Instruction Set Architecture,CISC)和精简指令集(Reduced Instruction Set Architecture,RISC)。

下面我们将详细介绍这两种架构的特点以及各自的优缺点。

一、复杂指令集(CISC)复杂指令集计算机体系结构最早出现在20世纪70年代,其最初的设想是将多条简单的指令合并成一条复杂的指令,以提高指令集的设计效率和程序的执行速度。

复杂指令集计算机单条指令可以针对一个任务执行多个操作,包括算术运算、逻辑运算、存储等操作。

它具有以下特点:1. 指令集较为复杂:CISC体系结构中的指令集合较为庞大,涵盖了多种算术运算、逻辑运算、访问存储器等操作,每条指令执行的操作数目较多。

2. 可以降低程序员的工作量:它具有很强的程序兼容性,程序员可以使用语义丰富、操作多样的指令来编写程序,编程较为简便。

3. 数据传输能力较强:CISC指令集支持多种地址寻址方式,可以通过一条指令传输大块数据,节省了时间和空间。

4. 代码密度较高:CISC指令具有较长的字长和高代码密度,可以使程序占用的内存较小。

5. 对内存的使用相对较少:由于CISC指令集中包含了很多常用的命令,所以相对于RISC指令集,CISC指令可以使程序的执行速度更快,CPU可以少使用内存。

不过随着时间的推移,CISC体系结构逐渐暴露出了一些问题。

CISC指令集架构虽然功能强大,但每条指令的执行时间较长,开销很高,导致处理器需要消耗更多的内存和时间来执行指令。

精简指令集计算机体系结构是20世纪80年代提出的一种新型的计算机架构,它的设计思想是通过增加寄存器数量和减少指令集的复杂程度,减少单条指令的执行时间,从而提高处理器的性能和效率。

c-sky指令集体系结构

c-sky指令集体系结构什么是csky指令集体系结构?C-SKY指令集体系结构(简称csky)是一种面向嵌入式系统设计的指令集体系结构框架。

它由中国科学院计算机技术研究所于2001年提出,以满足中国国内市场对高性价比、低功耗、可靠性强的嵌入式处理器的需求。

csky指令集体系结构兼容MIPS(微处理器无限公司,Microprocessor without Interlocked Piped Stages)指令集结构,并进行了一些优化和扩展。

1. csky指令集体系结构的设计理念:csky指令集体系结构的设计理念是在能够满足常见应用程序需求的基础上,尽可能简化指令集的结构,以提高处理器的执行效率和性能。

它追求高性价比和低功耗,适合用于大规模生产的嵌入式系统。

2. csky指令集体系结构的特点:- 中等长度的指令,32位的指令宽度,指令格式简单,指令集体积小。

这样能够减少实现复杂度和功耗。

- 16个通用寄存器,提供更高的寄存器容量,能够支持更大规模的程序。

- 支持单精度和双精度浮点运算,提高了计算能力。

- 适应不同层次的流水线设计,从单周期执行到多周期和超流水线执行,以满足不同应用场景的需求。

- 支持标准异常和跳转指令,提供了较好的异常处理能力。

3. csky指令集的分类和功能:csky指令集可以分为以下几类:- 数据传送类指令:包括load、store、move等指令,用于数据的读取和存储。

- 算术运算类指令:包括加减乘除、移位、逻辑运算等指令,用于完成常用算术和逻辑运算。

- 控制流类指令:包括无条件跳转、条件分支、函数调用等指令,用于控制程序的跳转和执行流程。

- 异常处理类指令:包括中断、异常、陷阱等指令,用于处理程序中的异常情况。

- 浮点运算类指令:包括浮点加减乘除、浮点比较等指令,用于高精度的浮点运算。

4. csky指令集的应用领域:csky指令集主要被应用在嵌入式系统领域,如工业控制、汽车电子、智能终端等。

计算机体系结构实验CPU设计与指令集实现

计算机体系结构实验CPU设计与指令集实现在计算机科学领域中,计算机体系结构是指计算机硬件和软件之间的接口规范,决定了计算机的性能和功能。

CPU作为计算机体系结构的核心组件之一,负责执行计算机指令和处理数据。

本文将介绍计算机体系结构实验中CPU的设计与指令集的实现。

一、CPU设计CPU设计是计算机体系结构实验的重要内容之一,它包括了处理器的内部结构、寄存器的设计和控制逻辑的实现等多个方面。

1. 内部结构CPU的内部结构一般包括运算器(ALU)、控制器、寄存器组和数据通路等部件。

其中,运算器负责进行算术和逻辑运算,控制器负责解码指令和控制CPU的操作,寄存器组用于存储临时数据和结果,数据通路则负责将数据在各个部件之间传递。

在CPU设计过程中,需要根据实验要求和设计目标,合理选择这些部件的结构和功能,并进行适当的组合和优化。

2. 寄存器设计寄存器是CPU中用于存储和操作数据的重要部件,常见的寄存器有通用寄存器、程序计数器(PC)、指令寄存器(IR)等。

在CPU设计中,需要确定寄存器的位数和数量,并根据需求设计合适的读写接口。

同时,寄存器的位宽和数量也决定了CPU的数据处理能力和存储容量。

3. 控制逻辑实现控制逻辑是CPU中决定指令执行流程和控制信号传递的关键部分。

它通过解码指令,生成相应的控制信号,控制数据通路的运行和寄存器的读写。

在CPU设计中,需要实现与指令集对应的控制逻辑,并确保指令的执行顺序和操作正确无误。

二、指令集实现指令集是计算机体系结构中的重要组成部分,它决定了计算机的操作方式和可执行的指令。

在计算机体系结构实验中,实现一个类似于RISC指令集的简化指令集是常见的任务。

1. 指令格式指令格式是指令在计算机中的二进制表示形式,通常由操作码(Opcode)、寄存器编号和立即数等字段组成。

在指令集实现中,需要确定指令格式的结构和位数,并考虑操作码和操作数的编码方式,以便正确解码和执行指令。

2. 指令执行指令执行是指计算机按照指令进行相应的操作,包括算术运算、逻辑运算、存储器读写等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

指令集作用和设计考量

• 重要作用: 反映计算机的基本功能,软件设计与硬件设计的 主要分界,影响程序执行的时间和效率 • 设计准则: •正交性:指令中不同含义字段之间编码时应互相独立 •规整性:对相似的操作有相同的规定 •可扩充性:保留一定的操作码空间,供以后扩展 •对称性:为编译方便,使操作有对称性 R1←R1-R2,则有R1←R2-R1 D←A+B×C 则有D←(A+B)×C

10

Computer Architecture Spring 2016

三种类型指令集结构的优缺点

指令集结构类型 优点 是一种表示计算的简 堆栈型 单模型;指令短小 缺点 不能随机访问堆栈,从而很难生成有效代码。 同时,由于堆栈是瓶颈,所以很难被高效地 实现 累加器型 减少了机器的内部 状态;指令短小 寄存器型 是代码生成的最一般 的模型 由于累加器是唯一的暂存器,这种机器的存储 器通信开销最大 所有操作数均需命名,且要显式表示,因而 指令较长

Mixed CISC & RISC? (IA-64. . .1999)

5

Computer Architecture Spring 2016

累加器型

6

Computer Architecture Spring 2016

堆栈型

7

Computer Architecture Spring 2016

8

Computer Architecture Spring 2016

• 寄存器可以保存变量 - 减少了存储器访问,从而提高了系统性能 -

代码密度得以提高,因为与存储器相比寄存器可以用 较少的比特进行索引或表征

21

Computer Architecture Spring 2016

MIPS的寄存器

• 可编程的存储机制

– 2^32 x bytes 存储空间 – 31 x 32-bit GPRs (R0 = 0) – 32 x 32-bit FP regs – HI, LO, PC – HI, LO是用于存储乘法和除 法运算结果的寄存器 – PC (Program Counter) 程序计数器,指令的地址或 指针

General Purpose Register Machines Complex Instruction Sets (Vax, Intel 432 1977-80) CISC (Intel x86 1980-199x) Load/Store Architecture (CDC 6600, Cray 1 1963-76) RISC (Mips,Sparc,HP-PA,IBM RS6000,PowerPC 1987)

16

Computer Architecture Spring 2016

用(面向累加器)一地址指令编写的程序: LOAD E ;先计算分母, ;取一个操作数到累加器中 ADD F ;分母运算结果在累加器中 STORE X ;保存分母运算结果到X中 LOAD A ;开始计算分子 MUL B ADD C SUB D ;累加器中是分子运算结果 DIV X ;最后运算结果在累加器中 STORE X ;保存最后运算结果到X中

Computer Architecture Spring 2016

计算机体系结构

Lesson 2. 指令集结构及其设计

讲课教师:周晓方/韩军 复旦大学微电子学院

1

Computer Architecture Spring 2016

内容提要

1. 指令集的作用与基本类别 2. 指令的寻址(Addressing) 3. 指令的格式(Format) 4. 指令的数据类型与大小( Type & Size ) 5. 指令操作(Operation) 6. 指令的后继(jumps, conditions, branchs)

17

用(面向堆栈)0地址指令编写程序: ab*c+d-ef+/ PUSH A ;操作数a压入堆栈 PUSH B ;操作数b压入堆栈 MUL ;栈顶两数相乘,结果压回堆顶 PUSH C ADD PUSH D SUB ;栈顶是分子运算的结果 PUSH E PUSH F ADD DIV ;栈顶是最后运算的结果 POP X ;保存最后运算结果

P 表示操作码长度,A 表示地址码长度,D 表示数据长度,R 表示通用 寄存器的地址码长度,B 表示字节数。并取:D=2A=8P=16R=8B

课后有习题

19

Computer Architecture Spring 2016

不同地址个数指令的特点及适用场合

程序 程序 程序执 地址数目 的长度 存储量 行速度 三地址 最短 最大 一般 二地址 一地址 零地址 较短 较长 最长 很大 较大 最小 最小 很低 最低 适用场合 向量,矩阵运算为主 一般不宜采用 嵌套,递归,变量较多

执行速度(访存信息量)

5P+15A=65B 5P+15A+15D=185B 7P+14A=63B 7P+14A+19D=215B 9P+ 9A=45B 9P+ 9A + 9D=117B 12P+7A=40B 12P+7A+29D=272B 8P+7A+9R=40B 8 P + 7 A + 9 R + 7 D = 96B

4

Computer Architecture Spring 2016

指令集设计的演进

Single Accumulator (EDSAC 1950) Accumulator + Index Registers (Manchester Mark I, IBM 700 series 1953) Separation of Programming Model from Implementation High-level Language Based (B5000 1963) Concept of a Family (IBM 360 1964)

22

r0 r1 ° ° ° r31 PC lo hi

0

Computer Architecture Spring 2016

MIPS的通用寄存器$0-$31

0 1 2 3 4 5 6 7 8 ... 15 t7 zero constant 0 at reserved for assembler v0 expression evaluation & v1 function results a0 arguments a1 a2 a3 t0 temporary: caller saves (callee can clobber) 16 s0 callee saves . . . (callee must save) 23 s7 24 t8 25 t9 26 k0 reserved for OS kernel 27 k1 28 gp Pointer to global area 29 sp Stack pointer 30 fp 31 ra frame pointer Return Address (HW)

13

Computer Architecture Spring 2016

例如:计算一个典型的算术表达式:

ab cd x e f

用三地址指令编写的程序如下: MUL X, A, B ;X←(A)×(B) ADD X, X, C ;X←(X)+(C) SUB X, X, D ;分子的计算结果在中 ADD Y, E, F ;计算分母,存入Y DIV X, X, Y ;最后结果在X单元中

18

Computer Architecture Spring 2016

Computer Architecture Spring 2016

用不同地址个数指令编写的程序 的存储容量和执行速度

地址数目 指令条数 访存次数 程序存储量 三地址 二地址 一地址 零地址 二地址 寄存器型 5 7 9 12 8 20 26 18 41 15

11

Computer Architecture Spring 2016

指令数量比较

• 分别采用四种指令集实现同样的功能 (C = A + B),其指令代码序 列的比较

Register (register-memory)

Load R1,A Add R1,B Store C, R1

Stack

Push A Push B Add Pop C

23

temporary (cont’d)

较快 连续运算,硬件结构简单 最快 多累加器,数据传送较多

二地址 一般 寄存器型

20

Computer Architecture Spring 2016

通用寄存器指令集的主导地位

° 1975-2000

大多数处理器采用了GPR指令集

° 寄存器的优势 • 寄存器比存储器快 • 寄存器便于程序编译 e.g., (A*B) – (C*D) – (E*F) 可以任意顺序完成3个乘法, 但堆栈就不可以

9

Computer Architecture Spring 2016

四种典型指令集

Accumulator-累加器 (1 register): 1 address add A acc acc + mem[A] 1+x address addx A acc acc + mem[A + x] Stack-堆栈: 0 address add tos tos + next General Purpose Register - 通用寄存器(can be memory/memory): 2 address add A B EA[A] EA[A] + EA[B] EA[A] EA[B] + EA[C] Ra Rb + Rc Ra mem[Rb] mem[Rb] Ra 3 address add A B C Load/Store( aslo GPR): 3 address add Ra Rb Rc load Ra Rb store Ra Rb