2014-2015学年第一学期北京交通大学数电数字电子与技术期中考试试题

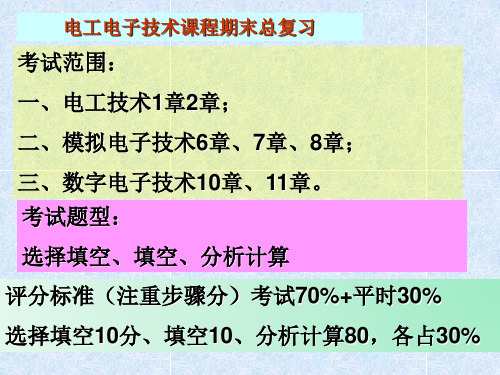

北交大2014-2015电工电子技术期末复习

I A

+ U A –

N

I N

– – U B + U C

I a

ZC

ZA N'

I B

I C

ZB

I A

–

+

U AB

U CA –

+ U BC – + C

I CA

I B

I C

ZCA Z ZAB

BC

I AB

负载的星形连接

B

I BC

负载的三角形连接 上页 下页

3、功率放大器的工作状态分类222页,乙类存在交越 失真,甲乙类改善交越失真。 4、负反馈对放大器的影响245页(1)到(6) 分析计算: 整流滤波、单管放大、运放线性应用。

上页

下页

二、模拟电子技术总复习 第 2章

分析计算: 1、整流滤波

(1)、电路功能、输出波形;

(2)电路正常工作输出电压Uo;

分析计算:

1、组合电路分析、

2、组合电路设计。

上页

下页

三、数字电子技术总复习 第 2章

分析计算:

1、组合电路分析 要求:表达式、真值表、逻辑功能。

。

2、组合电路设计 三台电机工作控制电路305页例11.1.3 三人表决电路 要求:真值表、表达式、电路图。 上页

下页结束语感谢全源自同学对教学工作的理解与支持(3)一个二极管有故障Uo;

(4)负载断开Uo。183页6.3.1、6.3.2 上页

下页

二、模拟电子技术总复习 第 2章

2、单管放大198页、207页

(1)、电路名称、功能、工作点计算;

(2)画微变等效电路;

(3)求放大倍数208页;

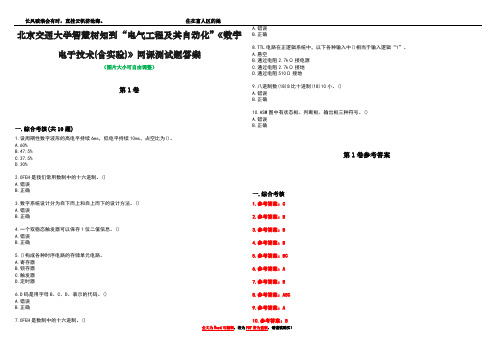

北京交通大学智慧树知到“电气工程及其自动化”《数字电子技术(含实验)》网课测试题答案_2

北京交通大学智慧树知到“电气工程及其自动化”《数字电子技术(含实验)》网课测试题答案(图片大小可自由调整)第1卷一.综合考核(共10题)1.设周期性数字波形的高电平持续6ms,低电平持续10ms,占空比为()。

A.60%B.47.5%C.37.5%D.30%2.0FEH是我们常用数制中的十六进制。

()A.错误B.正确3.数字系统设计分为自下而上和自上而下的设计方法。

()A.错误B.正确4.一个双稳态触发器可以保存1位二值信息。

()A.错误B.正确5.()构成各种时序电路的存储单元电路。

A.寄存器B.锁存器C.触发器D.定时器6.D码是用字母B、C、D、表示的代码。

()A.错误B.正确7.0FEH是数制中的十六进制。

() A.错误B.正确8.TTL电路在正逻辑系统中,以下各种输入中()相当于输入逻辑“1”。

A.悬空B.通过电阻2.7kΩ接电源C.通过电阻2.7kΩ接地D.通过电阻510Ω接地9.八进制数(18)8比十进制(18)10小。

()A.错误B.正确10.ASM图中有状态框、判断框、输出框三种符号。

()A.错误B.正确第1卷参考答案一.综合考核1.参考答案:C2.参考答案:B3.参考答案:B4.参考答案:B5.参考答案:BC6.参考答案:A7.参考答案:B8.参考答案:ABC9.参考答案:A10.参考答案:B。

15秋北交《数字电子技术(含实验)》在线作业二满分答案

15秋北交《数字电子技术(含实验)》在线作业二满分答案15秋北交《数字电子技术(含实验)》在线作业二满分答案一、多选题(共 10 道试题,共 40 分。

)1. 分析同步时序逻辑电路的一般步骤是()。

A. 列出逻辑方程组B. 列出状体表、画状态图或时序图C. 确定电路逻辑功能D. 列出时序逻辑电路功能正确答案:ABC2. CMOS数字集成电路与TTL数字集成电路相比突出的优点是( )。

A. 微功耗B. 高速度C. 高抗干扰能力D. 电源范围宽正确答案:ACD3. 卡诺图化简画包围圈时应遵循的原则是()。

A. 包围圈内的方格数必定是2n个,n等于0、1、2、3、...B. 相邻方格包括上下相邻、左右相邻和四角相邻C. 同一个方格可以被不同的包围圈重复包围,但新增包围圈中一定要有新的方则该包围圈为多余D. 包围圈内的方格数要尽可能多,包围圈的数目尽可能少正确答案:ABCD4. 卡诺图化简的步骤是()。

A. 将逻辑函数写成最小项表达式B. 按最小项表达式填写卡诺图C. 合并最小项D. 将包围圈对于的乘积项相加正确答案:ABCD5. 构成移位寄存器可以采用的触发器为()。

A. R-S型B. J-K型C. 主从型D. 同步型正确答案:ABC6. 与十进制相比二进制的优点是()。

A. 数字装置简单可靠、所有元件少B. 运算规则简单、运算操作方便C. 运算速度快D. 数值表达清晰、便于观察正确答案:AB7. 目前使用的两种双极型数字集成电路是()。

A. TTLB. PLDC. COMSD. ECL正确答案:AD8. 时序逻辑电路可分为()时序电路。

A. 触发B. 定时C. 异步D. 同步正确答案:CD9. 设计同步时序逻辑电路的一般步骤()和确定激励方程组、输出方程组、辑图、检查自启功能。

A. 建立原始状态图和原始状态表B. 状态化简C. 状态分配D. 选择出发器类型正确答案:ABCD10. TTL逻辑电路包括()。

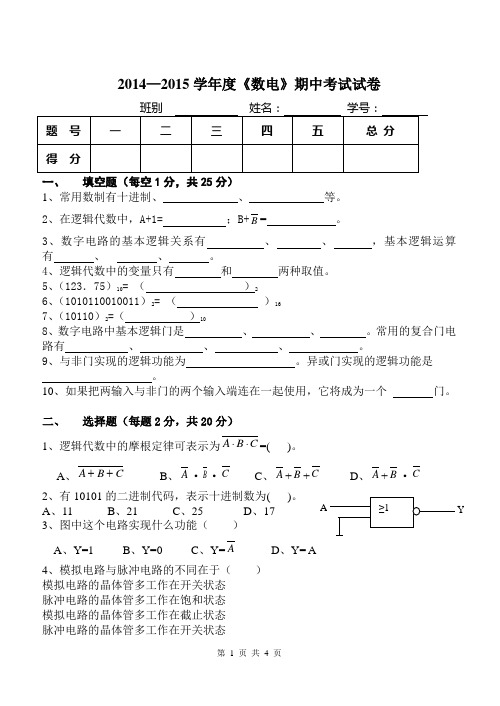

数字电路期中考试试卷167101

2014—2015学年度《数电》期中考试试卷班别 姓名: 学号:题 号 一 二 三 四 五 总 分 得 分一、 填空题(每空1分,共25分)1、常用数制有十进制、 、 等。

2、在逻辑代数中,A+1= ;B+B = 。

3、数字电路的基本逻辑关系有 、 、 ,基本逻辑运算有 、 、 。

4、逻辑代数中的变量只有 和 两种取值。

5、(123.75)10= ( )26、(1010110010011)2= ( )167、(10110)2=( )108、数字电路中基本逻辑门是 、 、 。

常用的复合门电路有 、 、 、 。

9、与非门实现的逻辑功能为 。

异或门实现的逻辑功能是 。

10、如果把两输入与非门的两个输入端连在一起使用,它将成为一个 门。

二、 选择题(每题2分,共20分)1、逻辑代数中的摩根定律可表示为C B A ⋅⋅=( )。

A 、CB A ++ B 、A ·B ·C C 、A +B +CD 、A +B ·C 2、有10101的二进制代码,表示十进制数为( )。

A 、11B 、21C 、25D 、17 —3、图中这个电路实现什么功能( )A 、Y=1B 、Y=0C 、Y=AD 、Y= A 4、模拟电路与脉冲电路的不同在于( ) 模拟电路的晶体管多工作在开关状态 脉冲电路的晶体管多工作在饱和状态 模拟电路的晶体管多工作在截止状态 脉冲电路的晶体管多工作在开关状态≥1 A Y5、若逻辑函数L=A+ABC+BC+B C,则L可化简为()A、L=A+BCB、L=A+CC、L=AB+B CD、L=A6、在何种输入情况下,“或非”运算的结果是逻辑0,不正确的是( )A.全部输入是0 B.全部输入是1 C.任一输入为0,其他输入为1 D.任一输入为1,其他输入为0。

7、.一位十六进制数可以用多少位二进制数来表示?()A.1B.2C.4D. 168、以下表达式中符合逻辑运算法则的是()A.C·C=C2B.1+1=10C.0<1D.A+1=19、四位16进制数最大的数是()A.1111 B .7777 C. FFFF D 都不是10、以下表达式中符合逻辑运算法则的是()四、化简与计算(25分)1、B A B A B A AB Y +++=2、BD C A AB D A AD Y ++++=3、C B A ABC Y +++=4、计算下列用补码表示的二进制数的代数和。

北京交通大学电气工程学院数字电子技术

下图是将 2片2716扩展成2048×16的数据的连接示意图。

例2:试用适当容量的PROM 实现两个两位二进制数比较的比较器。

N

A1 A0 B1 B0

0

0000

1

0001

2

0010

3

0011

4

0100

5

0101

6

0110

EPROM有各种类型的产品,下图是紫外线擦除、电可编程 的EPROM2716 器件逻辑框图和引脚图。

EPROM2716是211×8位可 改写存储器,有 11位地址线A0~ A10,产生字线为 2048条,D7~ D0是8位数据输出 /输入线,编程 或读操作时,数据由此输入或输 出。

CS为片选控制信号,是低电 平有效。

第六章 可编程逻辑器件PLD

可编程逻辑器件 PLD概述 可编程逻辑器件 PLD的基本单元 可编程只读存储器 PROM和可编程逻辑阵列PLA 可编程阵列逻辑 PAL和通用阵列逻辑GAL 高密度可编程逻辑器件 HDPLD 原理及应用 现场可编程门阵列 FPGA 随机存取存储器 RAM 小结

第一节 可编程逻辑器件 PLD概述

(一)叠栅型( SIMOS )存储单元

问题 :浮栅上的电荷无放电通路,没法泄漏。 在70o环境中,全部电荷放完需 100年。

用紫外线照射 芯片上的玻璃窗,则形成光电电流。

UV EPROM 芯片上开有 一个石英玻璃窗口

FLOTOX )储存单元 电可改写只读存储器 E2PROM ,即电擦除、电 编程的只读存储器。

E2PROM 以及闪速(Flash )存储器等。

编程单元采用 的是浮栅技术 。

(完整版)西交大14秋《数字电子技术》网上作业及参考答案

西交《数字电子技术》在线作业试卷总分:100 测试时间:--单选题一、单选题(共 50 道试题,共 100 分。

)V1. 处理______的电子电路是数字电路。

A. 交流电压信号B. 直流信号C. 模拟信号D. 数字信号满分:2 分2. 用卡诺图化简具有无关项的逻辑函数时,若用圈1法,在包围圈内的´是按处理;在包围圈外的´是按______处理。

A. 1,1B. 1,0C. 0,0D. 不确定。

满分:2 分3.A. 变为0B. 保持1不变C. 保持0不变D. 无法确定满分:2 分4. 10- 4线优先编码器允许同时输入__________路编码信号。

A. 1B. 9C. 10D. 多满分:2 分5. 标准TTL门关门电平Uoff之值为_________。

A. 0.3VB. 0.5VC. 0.8VD. 1.2V满分:2 分6. 数字电路中,晶体管的工作于_______状态。

A. 放大B. 饱和C. 截止D. 开关满分:2 分7. TTL与非门输出低电平的参数规范值是_______。

A. UOL≤0.3VB. UOL≥0.3VC. UOL≤0.4VD. UOL= 0.8V满分:2 分8. 三极管开关电路中,影响开关速度的主要因素是_______。

A. tdB. trC. tsD. tf满分:2 分9. TTL与非门输出高电平的参数规范值是_______。

A. UOH≥1.4VB. UOH≥2.4VC. UOH≥3.3VD. UOH= 3.6V满分:2 分10. 利用2个74LS138和1个非门,可以扩展得到1个______线译码器。

A. 2-4B. 3-8C. 4-16D. 无法确定。

满分:2 分11. 当________时,增强型NMOS管相当于开关接通。

A.B.C.D.满分:2 分12.A.B.C.D.满分:2 分13. 门电路输入端对地所接电阻R≤ROFF时,相当于此端_______。

电子信息工程数字电子技术专业第一学期期中考试题试卷及答案

XXX 学年第一学期期中考试试卷专业: 电子信息工程 课程:数字电子技术 年级:XX 级一、单项选择题(本大题共10小题,每小题1分,共10分)在每小题列出的四个备用选项中只有一个符合题目要求的,请将其代码填写在题后的括号内。

错选、多选或未选均无分。

1、逻辑函数F (A,B,C,D )=∑m (0,2,6,7,8,10,14,15)化简为最简“与或”表达式为: [ B ]。

A.F CDBC ; B.FBD BC ; C.FCDBC ; D.FCDBC ;2、逻辑函数F (A,B,C )=A ⊙C 的最小项标准式为: [ D ]。

A.F=∑m (0,2,6,7);B.F=∑m (0,2,7);C.F=∑m (1,3,6);D.F=∑m(0,2,5,7); 3、四变量函数F(A,B,C,D)的最小项m 12为:[ A ]。

A. ABC D ; B.A BC D ;C. ABC D ;D.AB C D ;4、已知逻辑变量A 、B 、F 的波形图如图1所示,则F 与A 、B 的逻辑关系是: [ C ]。

学号_____________ 班级___________ 姓名________ 考场号____ 座位号____- - - -- - - - -- - - - -- - - - - - - -- - - -- -- -密 ○- - - - - - - - - - - - - - -- - - -- -- - -封 ○- - - - - - - - - - - - -- - - --- - - -- -线 ○- - - - - - - - - - -- - - - -- - - - -- - - -- - - --A BF图1。

A. F=AB ;B. F=A ⊕B ;C. F=A ⊙B ;D. F=A+B ;5、逻辑函数F=AB+A C+B C+B CDEG 的最简与或式为: [ D]; A. AB+D ; B. A C+B ;C. A C+B ;D. AB+C ;6、函数F(A,B,C)=AB+BC+AC 的最小项表达式为: [ B ]; A. F(A,B,C)=∑m (0,2,4); B. F(A,B,C)=∑m (3,5,6,7); C. F(A,B,C)=∑m (0,2,3,4); D. F(A,B,C)=∑m (2,4,6,7);7、8线—3线优先编码器的输入为I 0~I 7 ,当优先级别最高的I 7有效时,其输出012Y Y Y ••的值是: [ C ]。

2013_2014年北京交通大学微机原理试题与答案A答案

北京交通大学考试试题(A卷)课程名称:微机原理与接口学年学期:2013—2014学年第1学期课程编号:14L128Q-03 开课学院:电信出题教师:5人学生:学号:任课教师:学生学院:班级:一、填空题(每题2分,共10分)1.80X86微机系统采用补码存储数据,16位补码表示的数值围为:____________________。

(-65536~+65535)2.某RAM芯片,其数据线为D0-D7,地址线为A0-A11,则此芯片的存储容量为:________。

(4KB )3.伪指令XBF DW 10 DUP(10,10 DUP(10)),系统为变量XBF 分配的字节数为:________。

(110)/6EH4.80X86微机系统根据中断向量表,获取中断向量,中断向量表的地址围为:__________。

(000H~3FFH)5.DMAC芯片8237A部有_______个独立的通道,每个通道的选址围为:_______。

4 64KB二、选择题(单选,每题2分,共10分)1.下列哪条指令执行后对状态标志位没有影响。

()AA. MOV AL,33HB. ADD AL,33HC. CMP AL,33HD. TEST AL,33H2.已知X1是定义的一个变量,下列哪条指令与LEA AX,X1结果相同。

()DA. MOV AX,X1B.ADD AX,X1C.MOV AX, SEG X1D. MOV AX, OFFSET X13.中断控制器8259中用于存放CPU当前正在服务的中断标志的寄存器为:()B A. 中断请求寄存器IRR B. 中断服务寄存器ISRC. 中断屏蔽寄存器IMRD. 中断优先权判别器PR4.串行接口芯片8250不能处理下列哪种中断。

()CA.接收数据出错 B. 接收缓冲器满C. 发送数据出错D. 发送寄存器空5.某微机系统含有3片8237A,其中一片为主片,两片为从片,试问此系统可以使用多少个DMA通道。

北京交通大学数字电子技术2015 期末考题

(4)每次 ADC0809 转换后的数据在 EOC 时钟脉冲的作用下,存入 16×8 RAM。不断 记录,但最多存放 16 个 8 位二进制数据。因此图 5 是一个简易数字采集存储电路。

CO C′ A0

B3

0 A1

CI

0 A2

0 A3

显示译

码器

(十位)

解:1. 图 3(a)中的 74161 是 6 进制计数器,分别是 0011、0100、0101、0110、0111 和 1000。74161 的输出经异或门后输出上述状态的反码。其接到图 3(b)的 74283 的输入 端 B3B2B1B0 时,再加 1,得到补码。用 A3A2A1A0 加补码 B3B2B1B0 时,实际上就是 14 减去上 述 6 种状态,S3S2S1S0 得到 1011、1010、1001、1000、0111 和 0110。

。

(A)Qn⊕Qn+1 (B)Qn+Qn+1 (C)1 (D)全有可能

答:A

(6)集成 555 电 路 在 控 制 电 压 端 CO 处 加 控 制 电 压 UCO, 则 集成 555 内 部 比 较

器 C2 的基准电压是

。

( A) 2UCO/3

(B)UCO/3

(C)UCO

(D)UCO/2

答:D

(7)多个

2.若图 3(b)的二进制输出 S3S2S1S0 在图 3(b)的 7 段发光管上显示 2 位十进制,设 计图 3(b)中的组合电路 A 为加 6 校正电路,如图 3 答所示。

3.若 74161 的时钟 CP 是 1Hz,观察到的图 3(b)中 7 段发光管每 1 秒换 1 个两位十 进制数字,分别是 11、10、09、08、07 和 06。

(完整word版)数字电子技术试题及答案(题库)

数字电子技术基础试题(一)一、填空题 : (每空1分,共10分)1. (30.25) 10 = ( ) 2 = ( ) 16 。

2 . 逻辑函数L = + A+ B+ C +D = 。

3 . 三态门输出的三种状态分别为:、和。

4 . 主从型JK触发器的特性方程= 。

5 . 用4个触发器可以存储位二进制数。

6 . 存储容量为4K×8位的RAM存储器,其地址线为条、数据线为条。

二、选择题: (选择一个正确的答案填入括号内,每题3分,共30分 )1.设图1中所有触发器的初始状态皆为0,找出图中触发器在时钟信号作用下,输出电压波形恒为0的是:()图。

图 12.下列几种TTL电路中,输出端可实现线与功能的电路是()。

A、或非门B、与非门C、异或门D、OC门3.对CMOS与非门电路,其多余输入端正确的处理方法是()。

A、通过大电阻接地(>1.5KΩ)B、悬空C、通过小电阻接地(<1KΩ)D、通过电阻接V CC4.图2所示电路为由555定时器构成的()。

A、施密特触发器B、多谐振荡器C、单稳态触发器D、T触发器5.请判断以下哪个电路不是时序逻辑电路()。

图2A、计数器B、寄存器C、译码器D、触发器6.下列几种A/D转换器中,转换速度最快的是()。

图2A、并行A/D转换器B、计数型A/D转换器C、逐次渐进型A/D转换器D、双积分A/D转换器7.某电路的输入波形 u I 和输出波形 u O 如图 3所示,则该电路为()。

图3A、施密特触发器B、反相器C、单稳态触发器D、JK触发器8.要将方波脉冲的周期扩展10倍,可采用()。

A、10级施密特触发器B、10位二进制计数器C、十进制计数器D、10位D/A转换器9、已知逻辑函数与其相等的函数为()。

A、B、C、D、10、一个数据选择器的地址输入端有3个时,最多可以有()个数据信号输出。

A、4B、6C、8D、16三、逻辑函数化简(每题5分,共10分)1、用代数法化简为最简与或式Y= A +2、用卡诺图法化简为最简或与式Y= + C +A D,约束条件:A C + A CD+AB=0四、分析下列电路。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

北京交通大学考试试题(期中)

课程名称:数字电子技术(A)学年学期:2014-2015学年第一学期

课程编号:14L126Q 开课学院:电信学院出题教师:

学生姓名:学号:任课教师:

学生学院:班级:

一、概念题(每空3分,共30分)

1. 一组合逻辑电路输入信号的变化顺序有以下三种情况,当顺序为时,将可能出现竞争冒险。

(A)00→01→11→10;(B)00→11→10→01;(C)00→01→00→10。

2. TTL与非门的灌电流负载发生在输出电平情况下,负载电流越大,则输出电平越。

3.CMOS门电路与TTL门电路相比最大的优点是。

(A)传输速度快;(B)功耗低;(C)功能全;(D)价格低。

4.能实现线与功能的门电路有;能实现总线连接方式的门电路有。

(A)与非门;(B)异或门;(C)三态门;(D)OC门。

5.图1所示电路的逻辑表达F= 。

F

图1

图2

6.图2所示电路的逻辑功能是 。

7.如图所示逻辑电路的表达式F = 。

8.如图所示逻辑电路的表达式F = 。

A 0A 1

二、分析题(共30分)

1.分析图示集成逻辑门电路功能。

(10分)

2.分析图示电路的逻辑功能。

图中74HC85是比较器,74CH283是加法器。

(10分)

3

2

1

3.试分析图示逻辑电路的逻辑功能。

(10分)

三、设计题(共40分) 1.分别用3—8译码器和2—4数据选择器及适当的门电路,实现下面的逻辑表达式。

(10分)(10分)

BC AC AB F ++=

(a )

S Q (b ) X

CP

Y

2.如图(a )所示电路,当其输入信号如图(b )所示,画出S 和Q 的波形。

(10分)

3.电路完整的状态转换图如图所示,说明该电路的逻辑功能,判断电路能否自启动?若不能,请改正,并用D 触发器实现该功能。

(20分)。