数字电路期中试卷(答案)

数电期末试卷及答案(共4套)

##大学信息院《数字电子技术根底》期终考试试题〔110分钟〕(第一套)一、填空题:〔每空1分,共15分〕1.逻辑函数Y AB C=+的两种标准形式分别为〔〕、〔〕。

2.将2004个“1〞异或起来得到的结果是〔〕。

3.半导体存储器的结构主要包含三个局部,分别是〔〕、〔〕、〔〕。

4.8位D/A转换器当输入数字量10000000为5v。

假设只有最低位为高电平,那么输出电压为〔〕v;当输入为10001000,那么输出电压为〔〕v。

5.就逐次逼近型和双积分型两种A/D转换器而言,〔〕的抗干扰能力强,〔〕的转换速度快。

6.由555定时器构成的三种电路中,〔〕和〔〕是脉冲的整形电路。

7.与PAL相比,GAL器件有可编程的输出结构,它是通过对〔〕进展编程设定其〔〕的工作模式来实现的,而且由于采用了〔〕的工艺结构,可以重复编程,使它的通用性很好,使用更为方便灵活。

二、根据要求作题:〔共15分〕1.将逻辑函数P=AB+AC写成“与或非〞表达式,并用“集电极开路与非门〞来实现。

2.图1、2中电路均由CMOS门电路构成,写出P、Q 的表达式,并画出对应A、B、C的P、Q波形。

三、分析图3所示电路:〔10分〕1)试写出8选1数据选择器的输出函数式;2)画出A2、A1、A0从000~111连续变化时,Y的波形图;3)说明电路的逻辑功能。

四、设计“一位十进制数〞的四舍五入电路〔采用8421BCD码〕。

要求只设定一个输出,并画出用最少“与非门〞实现的逻辑电路图。

〔15分〕五、电路与CP、A的波形如图4(a) (b)所示,设触发器的初态均为“0〞,试画出输出端B和C的波形。

〔8分〕BC六、用T触发器和异或门构成的某种电路如图5(a)所示,在示波器上观察到波形如图5(b)所示。

试问该电路是如何连接的?请在原图上画出正确的连接图,并标明T的取值。

〔6分〕七、图6所示是16*4位ROM和同步十六进制加法计数器74LS161组成的脉冲分频电路。

电工电子期中考试带答案

2018-2019第二学期17.5班机电一体化期中考试试题专业二(电工技术)总分150分,时间120分钟一、 选择题(选择一项正确答案,将其序号填入括号内,多选不给分。

每题2分,共60分)1.1A 的电流在5min 时间内通过某金属导体,流过其横截面的电荷量为( D )。

A 、1C B 、5C C 、60C D 、 300C2.当参考点改变变时,下列电量也相应发生变化的是( B )。

A.电压 B.电位 C.电动势 D. 以上三者皆是3.一根导体的电阻为R ,若拉长为原来的2倍,则其阻值为( C )。

A 、2/R B 、R 2 C 、R 4 D 、R 8 4.如题所示,a 点的电位IR E U a -=,对应的电路是( B )。

A BC D5.如图所示,为使内阻为9kΩ、量程为1V 的电压表量程扩大到10V ,可串联一个( C )分压电阻。

A 、1kΩ B、90kΩ C、81kΩ D、99k Ω6.在所示电路中,各电阻均为R ,等效电阻ab R 最小的是( B )。

A 、a 电路 B 、b 电路 C 、c 电路a )b )c )7.两只相同的电容器并联之后的等效电容,与它们串联之后的等效电容之比为( B )。

A 、1:4B 、4:1C 、1:2D 、2:1 8.下列说法中,正确的是( D )。

A 、 一段通电导线在磁场中某处受到的电磁力大,表明该处的磁感应强度大B 、 通电导线在磁场中受力为零,磁感应强度一定为零。

C 、 在磁感应强度为B 的均匀磁场中放入面积为S 的线框,线框的磁通为BS =φ。

D 、磁力线密处磁感应强度大。

9.当条形磁铁快速插入线圈时,电阻R 两端的电压( A )。

A 、0>ab U B 、0<ab U C 、0=ab U10.变压器一次、二次绕组,不能改变的是( D )。

A 、电压 B 、电流 C 、阻抗 D 、频率11.变压器一次、二次绕组匝比100=K ,二次绕组的负载阻抗L Z =10Ω,等效到一次绕组的阻抗是( B )。

数字电路期中考试试卷167101

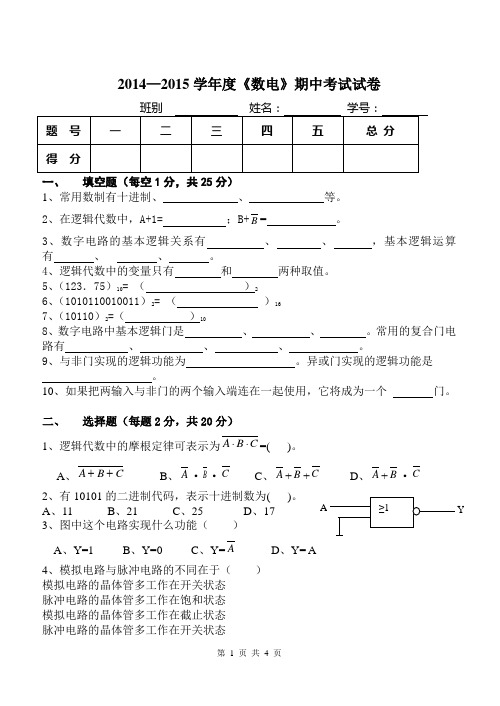

2014—2015学年度《数电》期中考试试卷班别 姓名: 学号:题 号 一 二 三 四 五 总 分 得 分一、 填空题(每空1分,共25分)1、常用数制有十进制、 、 等。

2、在逻辑代数中,A+1= ;B+B = 。

3、数字电路的基本逻辑关系有 、 、 ,基本逻辑运算有 、 、 。

4、逻辑代数中的变量只有 和 两种取值。

5、(123.75)10= ( )26、(1010110010011)2= ( )167、(10110)2=( )108、数字电路中基本逻辑门是 、 、 。

常用的复合门电路有 、 、 、 。

9、与非门实现的逻辑功能为 。

异或门实现的逻辑功能是 。

10、如果把两输入与非门的两个输入端连在一起使用,它将成为一个 门。

二、 选择题(每题2分,共20分)1、逻辑代数中的摩根定律可表示为C B A ⋅⋅=( )。

A 、CB A ++ B 、A ·B ·C C 、A +B +CD 、A +B ·C 2、有10101的二进制代码,表示十进制数为( )。

A 、11B 、21C 、25D 、17 —3、图中这个电路实现什么功能( )A 、Y=1B 、Y=0C 、Y=AD 、Y= A 4、模拟电路与脉冲电路的不同在于( ) 模拟电路的晶体管多工作在开关状态 脉冲电路的晶体管多工作在饱和状态 模拟电路的晶体管多工作在截止状态 脉冲电路的晶体管多工作在开关状态≥1 A Y5、若逻辑函数L=A+ABC+BC+B C,则L可化简为()A、L=A+BCB、L=A+CC、L=AB+B CD、L=A6、在何种输入情况下,“或非”运算的结果是逻辑0,不正确的是( )A.全部输入是0 B.全部输入是1 C.任一输入为0,其他输入为1 D.任一输入为1,其他输入为0。

7、.一位十六进制数可以用多少位二进制数来表示?()A.1B.2C.4D. 168、以下表达式中符合逻辑运算法则的是()A.C·C=C2B.1+1=10C.0<1D.A+1=19、四位16进制数最大的数是()A.1111 B .7777 C. FFFF D 都不是10、以下表达式中符合逻辑运算法则的是()四、化简与计算(25分)1、B A B A B A AB Y +++=2、BD C A AB D A AD Y ++++=3、C B A ABC Y +++=4、计算下列用补码表示的二进制数的代数和。

数电期中考试试卷答案

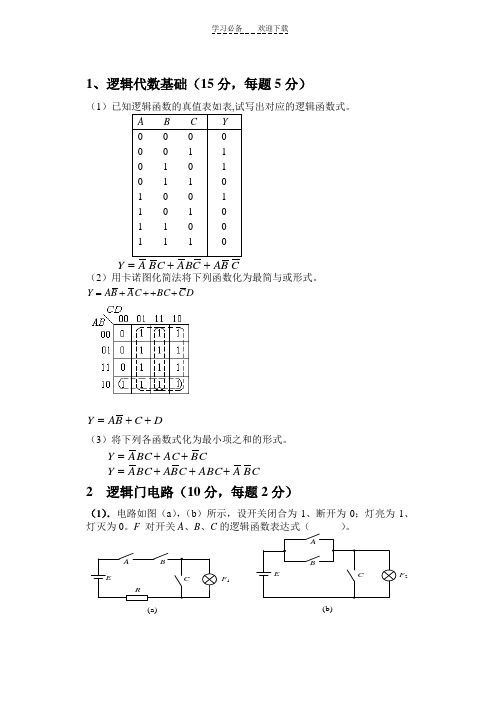

1、逻辑代数基础(15分,每题5分)(1CBACBACBAY++=(2)用卡诺图化简法将下列函数化为最简与或形式。

DCBCCABAY++++=DCBAY++=(3)将下列各函数式化为最小项之和的形式。

CBACBCAY++=CBAABCCBABCAY+++=2 逻辑门电路(10分,每题2分)(1).电路如图(a),(b)所示,设开关闭合为1、断开为0;灯亮为1、灯灭为0。

F对开关A、B、CF1F2(a)(b)A.C AB F =1 )(2B A C F += B.C AB F =1 )(2B A C F +=C. C B A F =2 )(2B A C F += (2).某TTL 反相器的主要参数为I IH =20μA ;I IL =1.4mA ;I OH =400μA ; I OL =14mA ,带同样的门数( )。

A.20 B.200 C.10 D.100 (3)在TTL 门电路的一个输入端与地之间开路,则相当于在该输入端输入( )。

A .高阻态B .高电平C .低电平 (4).在 正 逻 辑 条 件 下, 如 图 所 示 逻 辑 电 路 为( ) 。

A .“ 与 ” 门 B .“ 或” 门 C .“ 非” 门D .“ 与非” 门ABF(5).CMOS 门 电 路 的 扇 出 系 数 比 TTL 门 电 路( )。

(a) 小 得 多 (b) 小 (c) 大 得 多 1.A 2.C 3.B 4.A 5.C3、组合逻辑电路(40分,每题10分)(1) 有一水箱由大、小两台泵M L 和M S 供水,如图P3.4所示。

水箱中设置了3个水位检测元件A 、B 、C 。

水面低于检测元件时,检测元件给出高电平;水面高于检测元件时,检测元件给出低电平。

现要求当水位超过C 点时水泵停止工作;水位低于C 点而高于B 点时M S 单独工作;水位低于B 点而高于A 点时M L 单独工作;水位低于A 点时M L 和M S 同时工作。

电子线路设计期中测试卷(答案)

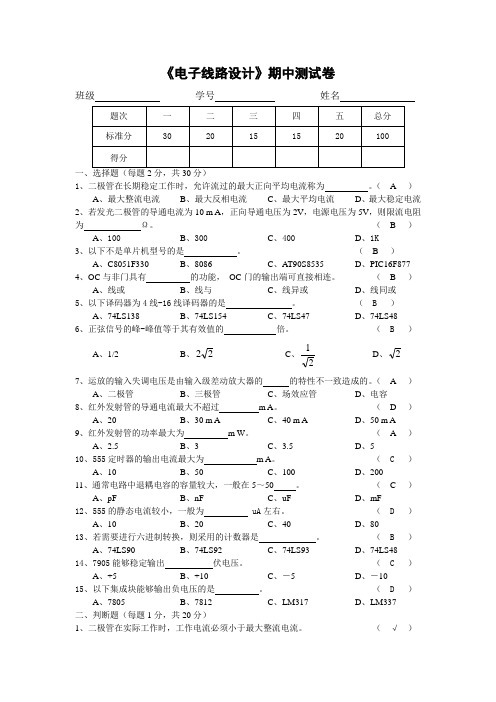

《电子线路设计》期中测试卷班级 学号 姓名一、选择题(每题2分,共30分)1、二极管在长期稳定工作时,允许流过的最大正向平均电流称为 。

( A )A 、最大整流电流B 、最大反相电流C 、最大平均电流D 、最大稳定电流2、若发光二极管的导通电流为10 m A ,正向导通电压为2V ,电源电压为5V ,则限流电阻为 Ω。

( B )A 、100B 、300C 、400D 、1K3、以下不是单片机型号的是 。

( B )A 、C8051F330B 、8086C 、AT90S8535D 、PIC16F8774、OC 与非门具有 的功能, OC 门的输出端可直接相连。

( B )A 、线或B 、线与C 、线异或D 、线同或5、以下译码器为4线-16线译码器的是 。

( B )A 、74LS138B 、74LS154C 、74LS47D 、74LS486、正弦信号的峰-峰值等于其有效值的 倍。

( B )A 、1/2B 、22C 、21D 、27、运放的输入失调电压是由输入级差动放大器的 的特性不一致造成的。

( A )A 、二极管B 、三极管C 、场效应管D 、电容 8、红外发射管的导通电流最大不超过 m A 。

( D )A 、20B 、30 m AC 、40 m AD 、50 m A 9、红外发射管的功率最大为 m W 。

( A )A 、2.5B 、3C 、3.5D 、5 10、555定时器的输出电流最大为 m A 。

( C )A 、10B 、50C 、100D 、200 11、通常电路中退耦电容的容量较大,一般在5~50 。

( C )A 、pFB 、nFC 、uFD 、mF 12、555的静态电流较小,一般为 uA 左右。

( D )A 、10B 、20C 、40D 、80 13、若需要进行六进制转换,则采用的计数器是 。

( B )A 、74LS90B 、74LS92C 、74LS93D 、74LS48 14、7905能够稳定输出 伏电压。

数字电路期中试卷

姓名: 班级: 学号:遵 守 考 试 纪 律注 意 行 为 规 范 ……………………试…………………………卷……………………密……………………封……………………线…………………… 江苏农林职业技术学院2018-2019学年第一学期期中考试 适用班级: 1609 《数字电路》试卷 卷面总分: 100 考试时间: 90 (分钟)一.单选题(每题3分,共15分) 1. 组合逻辑电路的功能是 。

A .放大数字信号 B .实现一定的逻辑功能 C .放大脉冲信号 D .存储数字信号 2.组合逻辑电路中一般不包括以下器件 。

A .与门 B .非门 C .放大器 D .或非门 3.不属于组合电路表达方式的一项是 。

A .真值表 B .逻辑电路 C .逻辑函数表达式 D .二进制代码 4.关于组合逻辑电路不正确的表述是 。

A .组合逻辑电路是由逻辑门电路所组成 B. 组合逻辑电路不可以作为存储信号的记忆元件 C. 组合逻辑电路的输出取决于输入状态 D. 组合逻辑电路的输出与以前状态有关5.组合逻辑电路是属于 。

A .数字电路 B. 模拟电路与门电路的组合C. 模拟电路D. 数字与模拟电路的组合二.简述题(每题 3分,共30 分)请指出下列各个实际连接图表示的逻辑关系,并画出相应的门电路的逻辑符号、逻辑功能、逻辑函数表达式、真值表。

1.2.3.三. 化简下列表达式(2*10=20分)1. D C ADE AC B A Y +++=1电路图E Y2. ))()()()((G E A G C E C G A D B D B Y ++++++++=四. 组合逻辑电路的分析与设计1. 用与非门设计一个举重裁判表决电路。

设举重比赛有3个裁判,一个主裁判和两个副裁判。

杠铃完全举上的裁决由每一个裁判按一下自己面前的按钮来确定。

只有当两个或两个以上裁判判明成功,并且其中有一个为主裁判时,表明成功的灯才亮。

(20分)2.对下面的电路图进行组合逻辑电路的分析设计,总结电路逻辑功能。

数电期中考试试题和答案

数电期中测试题 参考答案系别 班级 学号一、单项选择题(本大题共7小题,每小题2分,共14分)在每小题列出的四个备选项中只有一个是符合题目要求的,请将其代码填写在题后的括号。

错选、多选或未选均无分。

1.十进制数25用8421BCD 码表示为(B )A.10101B.0010 0101C.100101D.110012.函数B A ABC ABC F //++=的最简与或式是(D )A.F=A+BB.//C A F +=C.F=B+CD.F=B3.若将一个同或门(输入端为A,B )当作反相器使用,则A 、B 端应(C )A.A 或B 中有一个接1;B.A 和B 并联使用;C. A 或B 中有一个接0;D.同或门无法转换为反相器4.符合下面真值表的门电路是(C )A.与门B.或门C.同或门D.异或门 5.下列代码属于8421BCD 码的是(C )A.1010B.1100C.0111D.1101 6.最小项''A BC D 的逻辑相邻最小项是(B )A .''AB CD B .'''A BCD C .'ABCD D .'AB CD 7.函数F=AB+BC ,使F=1的输入ABC 组合为(D)A .ABC=000B .ABC=010C .ABC=101D .ABC=110二、填空题(本大题共10小题,每小题2分,共20分) 请在每小题的空格中填上正确答案。

错填、不填均无分。

1.基本逻辑运算有_______、 、 3种。

与、或、非 2.描述逻辑函数各个变量取值组合和函数值对应关系的表格叫_真值表。

3.函数Y=AB+AC的最小项之和表达式为________。

(ABC ABC C AB Y ++=//)4.3线-8线译码器74LS138处于译码状态时,当输入A 2A 1A 0=001时,输出/0/7~Y Y =______。

111111015.能够将1个输入数据,根据需要传送到m 个输出端的任何一个输出端的电路叫_______。

数字电路—期中复习

一、判断题()1.在数字逻辑电路中,信号只有高、低电平两种取值。

()2.负逻辑规定:逻辑1代表低电平,逻辑0代表高电平。

()3.在非门电路中,输入为高电平时,输出则为低电平。

()4.与运算中,输入信号与输出信号的关系是“有1出1,全0出0”。

()5.组合逻辑电路的特点是具有记忆能力。

()6.逻辑变量的取值中,1比0大。

()7.设逻辑表达式A+B=B+C,则A=C。

()8.由3个开关并联起来控制1只电灯时,电灯的亮与不亮同3个开关的闭合或断开之间的对应关系属于“与”的逻辑关系。

()9.与非门的逻辑功能是“全0出1,有1出0”。

()10.异或门是判断两个输入信号是否相同的门电路,两输入状态相异则输出为0。

()11.二进制数化为十进制数是应用“除2取余倒记法”获得的。

二、填空题1.基本逻辑门电路有与门、、。

2.在数字电路中,正逻辑用高电平表示逻辑________________。

3.如果逻辑型变量A=1,B=1,C=1,则逻辑表达式A B+BC+A C=_________。

4.异或门的逻辑功能是_____________________,_______________________。

5.逻辑变量的取值有种,即、__________。

6.与或非门的逻辑表达式为_______________________,它所实现的逻辑功能为_________________________________。

7.组合逻辑电路的分析方法和步骤为:(1)由逻辑电路图写出________________;(2)________________;(3)列出________________;(4)最后分析电路的功能。

8.组合逻辑电路的设计方法和步骤为:(1)根据实际问题的逻辑功能,列出__________;(2)写出__________,(3)化简逻辑函数表达式;(4)根据表达式________________。

三、选择题1.逻辑函数式_______________________CBAABCF+++=的逻辑值为()A ABCB 0C 1D ABC 2.如图1所示的电路为()门电路。

《数字电路与逻辑设计》期中考试试题

《数字电路与逻辑设计》期中考试试题2017.4注意:所有答案(包括选择题和计算题)一律写在试卷纸上,如果卷面位置不够,请写在试卷的背后,否则不计成绩。

一、(每题 2 分,共 28 分)单项选择题(答案填入本题后面的表格中) (请先在本试卷上答题之后,将全部答案汇总到本题末尾的表格中。

) 1.ECL 逻辑门(与 CMOS 门相比)主要优点是 D 。

A.抗干扰能力强 B. 集成度高 C.功耗低 D.工作速度快 2.均为 5V 供电时,TTL 逻辑门(与 CMOS 门相比)主要优点是 C 。

A. 噪声容限大 B. 功耗低 C. 工作速度快 D.集成度高 3. 若对 4 位二进制码(B 3B 2B 1B 0)进行奇校验编码,则校验位 C= B 。

A. B 3 + B 2 + B 1 + B 0 + 1B. B 3 ⊕ B 2 ⊕ B 1 ⊕ B 0 ⊕ 1C. B 3 B 2B 1 B 01D. B 3 B 2 B 1B 014.可以用来构成双向逻辑信号传输的逻辑器件是A 。

A . 三态输出门 B. OC 门 C. ECL 门 D. OD 门5. 逻辑函数 F=A ⊕B 和 G=A ⊙B 满足关系 A 。

A. F = G e 0B. F + G = 0C. F ⋅ G = 1D. F = G6.均为 5V 供电时,需接上拉电阻才能满足电平驱动要求的方式是 B 。

A . CMOS 门驱动 TTL 门 B. TTL 门驱动 CMOS 门 C . TTL 门驱动 TTL 门 D.CMOS 门驱动 CMOS 门 7. 输入变量仅 A 、B 全为 1 时,输出 F=1,输入与输出的关系是 C。

A .或非B .同或C .与D .异或 8. 逻辑表达式( A + B )( A + C ) = _D 。

A . AB + ACB .C + AB C . B + AC D. A + BC9. 最小项 ABCD 的相邻项是_ D。

数字电路期中复习

(1)、化简“与—或”式的主要方法

1)相邻项合并法

2)消项法

3)消去互补因子法 4)拆项法 把乘积项拆为两项, 再进行化简。 5)添项法

(2)、或与式的化简 化简方法:

①利用“或与”形式的公式进行化简。 ②采用二次对偶法进行化简。 “或与”式用公式法进行化简比较繁琐,建议采 用二次对偶比较简单。

000100108421bcd121011002看第一章补充习题和习题14171819第二章逻辑代数基础一逻辑代数的公式1??基本公式9个基本公式2??异或??同或逻辑公式1??基本公式3??多个变量的异或和同或之间的关系1偶数个变量的异或和同或互补2奇数个变量的异或和同或相等3当多个0??1相异或时起作用的是1的个数

第四章

组合逻辑电路

4.1 SSI组合逻辑电路的分析和设计 一、SSI组合电路的分析 1、分析步骤

(1)根据给定的逻辑电路图,写出表达式。

(2)列出真值表。 (3)由真值表抽象分析它的功能。(难点) 二、 SSI组合逻辑电路的设计

1、限制条件 (1)器件 (2)双轨输入(单轨不介绍)

2、设计步骤 (1)根据给定的逻辑功能,确定输入与输出信号之 间的逻辑关系。 (2)列出真值表

M i M j M i (0 i( j ) 2n 1, 且i j )

4、最小项与最大项之间的关系 (1)mi和Mi互补

(k为0 ~ (2n 1)中除了j以外的所有正整数)

例:F ( A, B, C ) m(1,2,4),

(3) m j M k

(k为0 ~ (2n 1)中除了j以外的所有正整数)

(2)最大项表达式(标准或与式)

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字电路期中试卷(答案)

第 2 页共 11 页

第 3 页共 11 页

第 4 页 共 11 页

三、简答题 (每小题5分,共25分)

1、用真值表证明等式:)(B A ⊕⊙A C =⊙)(C B ⊕ 证明:真值表如下:

由上述真值表(的后两列)知:)(B A ⊕⊙A C =⊙)(C B ⊕

2、用代数法化

简函数:

ADCBD D C B C B ABD D ABC L +++⋅+=)(

解:

C

B AB A

C B A

D A C B C AD AC B C B ABD ABC D C B C B ABD ABC D C B C B ABD ABCD D ABC ADCBD D C B C B ABD D ABC L +=+=++=++=++=+++=+++++=+++⋅+=)()()()()(

3、用卡诺图法化简函数:

∑∑+=)96,3,21()15,1312,111075,0(),,,(,,d ,,,,m D C B A R

解:画出卡诺图并化简,得

第 5 页 共 11 页

D C B C AB B A R +++=

4、分析下列功能表,说明其功能。

解:由功能表知:

(1)功能表是4线-2线优先编码器的功能表;

(2)此优先编码器有1个输入使能控制端E ,高电平有效;

(3)有4个输入端,优先级别从3

I 、2I 、1

I 、0

I 依次降低,且为高电平有效;

(4)有1个输出指示端GS ,低电平有效; (5)有2个输出端1Y 、0

Y ,高电平有效,权值分别为2、1。

(6)优先编码器的输出为:

321I I Y +=,3

210I I I Y +=,

第 6 页 共 11 页

3

210I I I I GS =

5、根据下图所示4选1数据选择器实现的组合电路,写出输出F 的逻辑表达式,并化成最简“与或”表达式。

(注:图中地址码A 1为高位,A 0为低位)

解:当0=E 时,4选1数据选择器(74X153)正常工作,可输出函数:

301201101001D A A D A A D A A D A A Y +++=

由逻辑电路图知:

Y F =,C A =1,D A =0,且00=D 、B D =1、12=D ,A D =3

从而有:

D

C D C B AC AD D C D C B ACD D C D C B A

CD D C B D C D C L ++=++=++=⋅+⋅+⋅+⋅=)(10

四、分析设计题 (1题10分,2、3题各15分,共40分)

1、分析下图所示电路的逻辑功能。

要求: (1)写出输出的逻辑函数表达

式并化简;(4分) (2)列出真值表;(4分) (3)说明电路的逻辑功能。

(2分) 解:(1)由逻辑电路图可写出逻辑函数表达式为

BC

AC AB R C B A C B A R ++=⊕⊕=⊕⊕=21)(

(2)根据表达式得真值表如下

A B C B A ⊕ AB

AC

BC

R 2 R 1 0

0 0

第 7 页 共 11 页

(3)分析:根据真值表可知,该电路逻辑功能为1位二进制数的全加器。

其中A 、B 为加数、被加数,C 为低位来的进位;R 1为和位,R 2为向高位的进位。

2、用3-8线译码器设计一个组合电路,其输入为3位二进制数,当输入的数不小于3也不大于6时,输出1,否则输出0。

(3-8线译码器逻辑符号见下,可直接利用此图。

)

解:(1)设3位二进制数为X = ABC ,其中A 为高位,C 为低位;输出为F ,当63≤≤X 时F = 1,否则F = 0。

(2)列真值表如下

(3)由真值表得逻辑函数,并变换为与非式

C

AB C B A C B A BC A C

AB C B A C B A BC A C

AB C B A C B A BC A F ⋅⋅⋅=+++=+++=

(4)由3-8线译码器的功能表知:当13=E 、021==E E 时,3-8线译码器正常工作。

第 8 页 共 11 页

令A A =2、B A =1、C A =0,另加一个4输入与非门,将3Y 、4Y 、5Y 、

6Y 引至与非门输入端,与非门的输出端

即为F 。

电路连接如图所示。

3、试用MSI 8选1数据选择器(74×151)实现比较两个2位二进制数A 、B 的大小的功能:当B A <时,指示灯亮。

(已知:ab A =、cd B =;8选1数据选择器功能表见下,约定abc 分别接地址码的高中低位)

解法1:用

MSI 8选1数据选择器(74×151)实现

(1)已知二进制数ab A =、cd B =。

设当B A <,指示灯亮时,输出变量F =1,否则指示灯不亮,输出变量F =0。

(2)由题意列真值表如下

A

B

输出 a

b C d F 0 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 1 0 1 0 0 0 0 1 0 1 0 0

1

1

1

第 9 页 共 11 页

(3)根据上述真值表可得输出逻辑函数表达式,并变换

5

5331100)(1)(1)()(D m D m D m D m d c b a bc a c b a d c b a cd b a bcd a d bc a cd b a d c b a d c b a F +++=+⋅+⋅+=+++++=

(4)由74×151的功能知:

当a A =2

、b A =1、c A =0,且令

d D D ==50、131==D D 及

07642====D D D D ,则可实现二进制数

“B A <”的比较电路,逻辑电路图如下。

0 1 1 1 1 1 0 0 0 0 1 0 0 1 0 1 0 1 0 0 1 0 1 1 1 1 1 0 0 0 1 1 0 1 0 1 1 1 0 0 1 1 1 1 0

解法2:用SSI门电路实现

(1)已知二进制数ab

A=、cd

B=。

设当B

A<,指示灯亮时,输出变量L =1,否则指示灯不亮,输出变量L =0。

(2)同上。

(3)用卡诺图化简函数

(4)用SSI非门、与门、或门实现上述函数,逻辑电路图如下左图。

或用SSI非门、与非门实现上述函数,

cd

b

d

b

a

c

a

L⋅

⋅

=,逻辑电路

图如下右图。

cd

b

d b a

c a

L+

+

=

第 10 页共 11 页

物电系 2014 级电子信息专业《数字电路》课程期中考试卷(参考答案)

第 11 页共 11 页。