主板用MOSFET的封装形式及技术

MOS管封装分析报告

MOS管封装分析报告(含主流厂商封装)在完成MOS管芯片在制作之后,需要给MOS管芯片加上一个外壳,这就是MOS管封装。

该封装外壳主要起着支撑、保护和冷却的作用,同时还可为芯片提供电气连接和隔离,从而将MOS管器件与其它元件构成完整的电路。

而不同的封装、不同的设计,MOS管的规格尺寸、各类电性参数等都会不一样,而它们在电路中所能起到的作用也会不一样;另外,封装还是电路设计中MOS管选择的重要参考。

封装的重要性不言而喻。

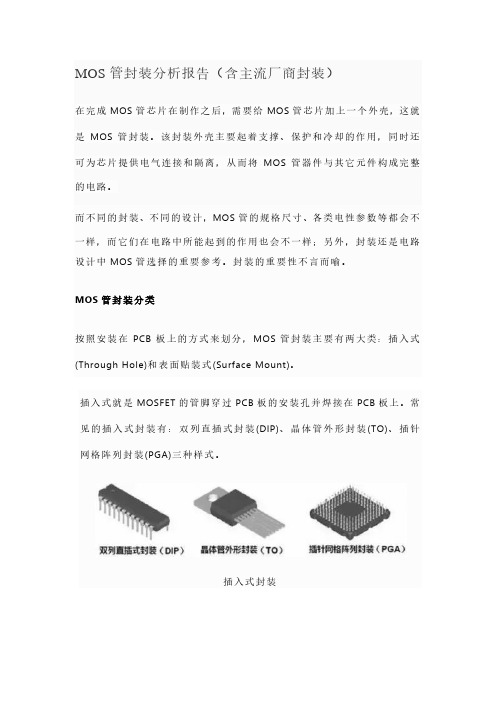

MOS管封装分类按照安装在PCB板上的方式来划分,MOS管封装主要有两大类:插入式(Through Hole)和表面贴装式(Surface Mount)。

插入式就是MOSFET的管脚穿过PCB板的安装孔并焊接在PCB板上。

常见的插入式封装有:双列直插式封装(DIP)、晶体管外形封装(TO)、插针网格阵列封装(PGA)三种样式。

插入式封装表面贴裝则是MOSFET的管脚及散热法兰焊接在PCB板表面的焊盘上。

典型表面贴装式封装有:晶体管外形(D-PAK)、小外形晶体管(SOT)、小外形封装(SOP)、方形扁平式封装(QFP)、塑封有引线芯片载体(PLCC)等。

表面贴装式封装随着技术的发展,目前主板、显卡等的PCB板采用直插式封装方式的越来越少,更多地选用了表面贴装式封装方式。

1、双列直插式封装(DIP)DIP封装有两排引脚,需要插入到具有DIP结构的芯片插座上,其派生方式为SDIP(Shrink DIP),即紧缩双入线封装,较DIP的针脚密度高6倍。

DIP封装结构形式有:多层陶瓷双列直插式DIP、单层陶瓷双列直插式DIP、引线框架式DIP(含玻璃陶瓷封接式、塑料包封结构式、陶瓷低熔玻璃封装式)等。

DIP封装的特点是可以很方便地实现PCB板的穿孔焊接,和主板有很好的兼容性。

但由于其封装面积和厚度都比较大,而且引脚在插拔过程中很容易被损坏,可靠性较差;同时由于受工艺的影响,引脚一般都不超过100个,因此在电子产业高度集成化过程中,DIP封装逐渐退出了历史舞台。

mosfet的封装流程

mosfet的封装流程MOSFET(金属氧化物半导体场效应晶体管)是一种常用的功率开关器件,广泛应用于电子电路中。

在MOSFET的生产过程中,封装是十分重要的一环。

封装是将芯片与外部环境隔离,并提供电气连接和机械支持的过程。

本文将介绍MOSFET的封装流程。

MOSFET的封装流程通常包括以下几个步骤:准备基材、制造封装、封装测试和质量控制。

首先是准备基材。

在封装流程开始之前,需要准备好基材,通常是由硅片制成的晶圆。

晶圆经过一系列的工艺步骤,如清洗、去除杂质和涂覆薄膜等,以确保其表面的平整度和纯度。

接下来是制造封装。

制造封装的第一步是将晶圆锯成小片,每个小片上都会有一个MOSFET芯片。

然后,这些芯片会通过一系列的工艺步骤,如金属化、蚀刻、光刻和沉积等,来形成MOSFET的结构。

这些工艺步骤的目的是在芯片上形成源极、漏极和栅极等电极,以及与之相连的金属线路。

完成芯片结构后,接下来是封装测试。

在封装测试中,会对芯片进行一系列的电性能测试,以确保其工作正常。

这些测试包括电流-电压特性测试、开关速度测试和温度特性测试等。

通过这些测试,可以评估MOSFET的性能是否符合要求。

最后是质量控制。

在封装流程的最后阶段,会对已经封装好的MOSFET进行质量控制。

质量控制的目的是检查封装过程中是否存在任何缺陷,如焊接问题、封装材料的质量等。

只有通过了质量控制的MOSFET才能出厂销售。

总结一下,MOSFET的封装流程包括准备基材、制造封装、封装测试和质量控制。

这个流程确保了MOSFET的性能和质量符合要求。

在封装过程中,需要经过多个工艺步骤,如金属化、蚀刻、光刻和沉积等,以形成MOSFET的结构。

而封装测试和质量控制则是对MOSFET进行电性能测试和质量检查,以确保其工作正常。

通过这些步骤,可以生产出高质量的MOSFET,满足各种电子电路的需求。

MOS管的封装类型分享

MOS管的封装类型分享

MOS管的封装类型,常常影响着电路的设计方向,甚至是产品性能走向;但面对形色各异的封装,我们该如何辨别?主流企业的封装又有什么特点?

在完成MOS管芯片在制作之后,需要给MOS管芯片加上一个外壳,这就是MOS管封装。

该封装外壳主要起着支撑、保护和冷却的作用,同时还可为芯片提供电气连接和隔离,从而将MOS管器件与其它元件构成完整的电路。

而不同的封装、不同的设计,MOS管的规格尺寸、各类电性参数等都会不一样,而它们在电路中所能起到的作用也会不一样;另外,封装还是电路设计中MOS管选择的重要参考。

封装的重要性不言而喻,今天我们就来聊聊MOS管封装的那些事。

MOS管封装分类

按照安装在PCB板上的方式来划分,MOS管封装主要有两大类:插入式(Through Hole)和表面贴装式(Surface Mount)。

插入式就是MOSFET的管脚穿过PCB板的安装孔并焊接在PCB板上。

常见的插入式封装有:双列直插式封装(DIP)、晶体管外形封装(TO)、插针网格阵列封装(PGA)三种样式。

插入式封装

表面贴裝则是MOSFET的管脚及散热法兰焊接在PCB板表面的焊盘上。

典型表面贴装式封装有:晶体管外形(D-PAK)、小外形晶体管(SOT)、小外形封装(SOP)、方形扁平式封装(QFP)、塑封有引线芯片载体(PLCC)等。

表面贴装式封装

随着技术的发展,目前主板、显卡等的PCB板采用直插式封装方式的越来越少,更多地选用了表面贴装式封装方式。

1、双列直插式封装(DIP)。

TO220F形式MOSFET封装工艺技术

TO220F形式MOSFET封装工艺技术摘要:我司目前生产的MOSFET封装产品基本采用TO220F形式,本文针对MOSFET产品特点对TO220F形式封装要求,详细阐述关键工艺流程、关键材料、可靠性实验方法等。

0 引言MOSFET是英文Metal-Oxide-Semiconductor Field-Effect Transistor即金属-氧化层-半导体-场效晶体管的缩写,是一种单极晶体管,只靠一种极性载流子(电子或空穴)传输电流。

以下分析主要依据N沟道增强型高压功率MOSFET。

1 MOSFET产品基本概述1.1工作原理图1.MOSFET剖面示意图MOSFET分3个极G:栅极S:源极D:漏极正常工作条件下,源PN结及漏PN结或为零偏或为反偏,在漏极到源极之间加电压,而沟道未形成时,将只有近似于反偏PN结漏电源大小的极小电流在漏极到源极之间流动。

但是若在栅极电压控制之下,表面形成了沟道,它将使漏区与源区连通,在V D S作用之下就出现明显的漏极电流,而且漏极电流的大小依赖于栅极电压。

在V D S=常数的条件下,漏极电流I D随栅极电压V G S的变化曲线如下,称为MOSFET的转移特性曲线图2:N沟道增强型转移特性曲线1.2 MOSFET的分类a.按照沟道导电载流子的极性,分为N沟道和P沟道:N沟道为电子,P沟道为空穴。

b.按照转移特性曲线,分为增强型和耗尽型:V G S=0时截止,漏极电流近似等于零的器件是增强型;V G S=0时导通,漏极电流不等于零的器件是耗尽型。

我司生产的2N60、4N60等产品就是属于N沟道增强型高压功率MOSFET。

2 MOSFET产品封装的工艺控制2.1 静电防护MOSFET 对静电敏感,当电荷累积过多而不能及时放掉的话,很容易造成击穿。

所以,在划片:Wafer Dicing 粘片:Die Bonding 焊线:Wire Bonding 和最后的切筋分粒成为单个器件后的每一个过程中,所有相关设备必须接地导通,人员如果进行手工操作时必须佩戴防静电手环并接地。

mosfet的封装流程

mosfet的封装流程MOSFET(金属-氧化物-半导体场效应晶体管)是一种主要用于电子设备的半导体器件。

它可以在低频和高频应用中控制电压和电流,同时也具有高度的可靠性和稳定性。

封装流程是将MOSFET芯片封装到外壳中的过程,本文将详细介绍MOSFET封装的流程。

第一步:芯片设计MOSFET芯片的设计是封装流程的起点。

在这个阶段,芯片设计师根据特定的应用需求,使用CAD软件设计出晶体管的晶片结构、电路连接、金属层和其他重要元件。

设计完成后,芯片的原型将通过多次验证和优化,确保其性能达到预期。

第二步:切割划分在芯片制造的过程中,多个MOSFET被同时加工在一块硅片上。

在封装流程中的第一步是将硅片切割成单个芯片。

通过切割划分可以分离出单个晶体管芯片,以便后续的工艺步骤。

第三步:清洗和制备划分得到的芯片需要进行清洗和制备,以去除可能存在的污染物和杂质。

一般来说,芯片会先进行机械清洗来去除表面的尘土和杂质,然后再进行化学清洗以去除更加顽固的污染物。

制备涉及到芯片表面的涂覆和处理,以便在后续步骤中使其更加适合封装。

第四步:引线焊接一旦芯片清洗和制备完毕,就可以进行引线焊接。

这一步是将芯片上的金属连接到引线上的关键步骤。

通常,在芯片的金属电极上加压形成连接。

第五步:封装引线焊接完成后,芯片需要被封装在外壳之中。

封装是将芯片保护在一个可靠且耐用的外壳中,以防止机械损坏和环境污染。

封装的过程通常涉及到预先设计的外壳底部,将引线和芯片放入外壳内部,然后封装上部分,使引线和芯片稳固地固定在外壳中。

第六步:测试和质量控制一旦完成封装,封装的MOSFET将会被送往测试和质量控制部门进行测试。

测试的目的是确保芯片在封装过程中没有受到损坏,并且在运行时能够按照预定的标准工作。

此外,还会检查芯片的功耗、速度、温度特性等重要参数,以保证其质量和性能稳定。

第七步:包装和出货经过测试和质量检查后,封装的MOSFET将会进行最终的包装和出货。

一种mosfet芯片的封装结构和工艺的制作方法

一种mosfet芯片的封装结构和工艺的制作方法

MOSFET(金属-氧化物-半导体场效应晶体管)芯片的封装

结构和制作方法如下:

1. 封装结构:

MOSFET芯片的封装结构通常由芯片、引脚和封装材料组成。

芯片是MOSFET的主体,引脚用于连接芯片与外部电路,封

装材料用于保护芯片和引脚,并提供机械支撑。

2. 制作方法:

MOSFET芯片的制作方法主要包括以下步骤:

a. 衬底准备:选择适当的半导体材料(如硅),并进行基

础处理,例如清洗和去除杂质。

b. 衬底掺杂:通过离子注入或扩散等方法,在衬底上掺入

所需的杂质,形成N型或P型区域。

c. 通道区域形成:在衬底上生长一层绝缘层,通常是氧化层。

然后,在绝缘层上生长一层薄膜,通常是多晶硅,用

于形成MOSFET的通道。

d. 金属电极形成:在薄膜上沉积金属,例如铝或铜,形成

源极和漏极。

e. 门电极形成:在绝缘层上沉积一层金属,例如铝或钨,

形成门电极。

f. 电极连接:使用金属线或导电粘合剂将源极、漏极和门电极与芯片外部引脚连接起来。

g. 封装:将芯片和引脚放置在封装材料中,并使用封装设备将其封装起来,以保护芯片和引脚,并提供机械支撑。

h. 测试和封装检验:对封装好的芯片进行电性能测试和封装质量检验,以确保其符合设计要求和质量标准。

以上是一种常见的MOSFET芯片的封装结构和制作方法,实际制作过程可能会有所不同,具体取决于芯片的设计和制造工艺。

MOS管(金属氧化物半导体场效应管)的封装结构

MOS管(金属氧化物半导体场效应管)的封装结构MOS管(金属氧化物半导体场效应管,Metal Oxide Semiconductor Field Effect Transistor)的封装结构一般采用以下几种形式:

1.TO封装(Tin-Can Outline Package):这是一种传统的封装形

式,外观类似金属罐。

TO封装通常具有3个引脚,通过引脚与电路进行连接。

MOS管内部的芯片被放置在金属罐体内,并通过引脚与外部电路连接。

2.DIP封装(Dual Inline Package):DIP封装是一种常见的直插

式封装形式。

它通常包含了两排引脚,引脚与MOS管内部芯片相连。

DIP封装的主要优点是容易安装和替换。

3.SMD封装(Surface Mount Device Package):SMD封装是一

种表面贴装封装形式,常用于表面贴装技术(SMT)的电子设备制造中。

SMD封装通常具有平面外形,方便在PCB (Printed Circuit Board)上进行组装。

常见的SMD封装类型包括SOIC、QFN和QFP等。

4.Power Package(功率封装):功率MOS管通常需要具备较大

的功率承受能力和散热性能,因此采用特殊的功率封装结构。

常见的功率封装形式包括TO-220、TO-247和D2PAK等,具有较大的引脚和散热片。

MOSFET的封装技术图解大全..

MOSFET的封装技术图解大全主板MOSFET的封装技术图解大全主板的供电一直是厂商和用户关注的焦点,视线从供电相数开始向MOSFET器件转移。

这是因为随着MOSFET技术的进展,大电流、小封装、低功耗的单芯片MOSFET以及多芯片DrMOS开始用在主板上,新的功率器件吸引了主板用户的眼球。

本文将对主板采用的MOSFET器件的封装规格和封装技术作简要介绍。

MOSFET芯片制作完成后,需要封装才可以使用。

所谓封装就是给MOSFET 芯片加一个外壳,这个外壳具有支撑、保护、冷却的作用,同时还为芯片提供电气连接和隔离,以便MOSFET器件与其它元件构成完整的电路。

芯片的材料、工艺是MOSFET性能品质的决定性因素,MOSFET厂商自然注重芯片内核结构、密度以及工艺的改进,以提高MOSFET的性能。

这些技术改进将付出很高的成本。

封装技术也直接影响到芯片的性能和品质,对同样的芯片以不同形式的封装,也能提高芯片的性能。

所以芯片的封装技术是非常重要的。

以安装在PCB的方式区分,功率MOSFET的封装形式有插入式(Through Hole)和表面贴装式(Surface Mount)二大类。

插入式就是MOSFET的管脚穿过PCB的安装孔焊接在PCB上。

表面贴裝则是MOSFET的管脚及散热法兰焊接在PCB 表面的焊盘上。

常见的直插式封装如双列直插式封装(DIP),晶体管外形封装(TO),插针网格阵列封装(PGA)等。

典型的表面贴装式如晶体管外形封装(D-PAK),小外形晶体管封装(SOT),小外形封装(SOP),方形扁平封装(QFP),塑封有引线芯片载体(PLCC)等等。

电脑主机板一般不采用直插式封装的MOSFET,本文不讨论直插式封装的MOSFET。

一般来说,“芯片封装”有2层含义,一个是封装外形规格,一个是封装技术。

对于封装外形规格来说,国际上有芯片封装标准,规定了统一的封装形状和尺寸。

封装技术是芯片厂商采用的封装材料和技术工艺,各芯片厂商都有各自的技术,并为自己的技术注册商标名称,所以有些封装技术的商标名称不同,但其技术形式基本相同。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

主板用MOSFET的封装形式和技术作者:魏昕鑫编辑:魏昕鑫2009-06-04 11:15:46 [投递]主板的供电一直是厂商和用户关注的焦点,视线从供电相数开始向MOSFET器件转移。

这是因为随着MOSFET技术的进展,大电流、小封装、低功耗的单芯片MOSFET以及多芯片D rMOS开始用在主板上,新的功率器件吸引了主板用户的眼球。

本文将对主板采用的MOSFET器件的封装规格和封装技术作简要介绍。

MOSFET芯片制作完成后,需要封装才可以使用。

所谓封装就是给MOSFET芯片加一个外壳,这个外壳具有支撑、保护、冷却的作用,同时还为芯片提供电气连接和隔离,以便MOS FET器件与其它元件构成完整的电路。

芯片的材料、工艺是MOSFET性能品质的决定性因素,MOSFET厂商自然注重芯片内核结构、密度以及工艺的改进,以提高MOSFET的性能。

这些技术改进将付出很高的成本。

封装技术也直接影响到芯片的性能和品质,对同样的芯片以不同形式的封装,也能提高芯片的性能。

所以芯片的封装技术是非常重要的。

以安装在PCB的方式区分,功率MOSFET的封装形式有插入式(Through Hole)和表面贴装式(Surface Mount)二大类。

插入式就是MOSFET的管脚穿过PCB的安装孔焊接在PCB上。

表面贴裝则是MOSFET的管脚及散热法兰焊接在PCB表面的焊盘上。

常见的直插式封装如双列直插式封装(DIP),晶体管外形封装(TO),插针网格阵列封装(PGA)等。

典型的表面贴装式如晶体管外形封装(D-PAK),小外形晶体管封装(SOT),小外形封装(SOP),方形扁平封装(QFP),塑封有引线芯片载体(PLCC)等等。

电脑主机板一般不采用直插式封装的MOSFET,本文不讨论直插式封装的MOSFET。

一般来说,“芯片封装”有2层含义,一个是封装外形规格,一个是封装技术。

对于封装外形规格来说,国际上有芯片封装标准,规定了统一的封装形状和尺寸。

封装技术是芯片厂商采用的封装材料和技术工艺,各芯片厂商都有各自的技术,并为自己的技术注册商标名称,所以有些封装技术的商标名称不同,但其技术形式基本相同。

我们先从标准的封装外形规格说起。

一、标准封装规格1、TO封装TO(Transistor Out-line)的中文意思是“晶体管外形”。

这是早期的封装规格,例如TO-92,TO-92L,TO-220,TO-252等等都是插入式封装设计。

近年来表面贴装市场需求量增大,TO封装也进展到表面贴装式封装。

TO252和TO263就是表面贴装封装。

其中TO-252又称之为D-PAK,TO-263又称之为D2PAK。

D-PAK封装的MOSFET有3个电极,栅极(G)、漏极(D)、源极(S)。

其中漏极(D)的引脚被剪断不用,而是使用背面的散热板作漏极(D),直接焊接在PCB上,一方面用于输出大电流,一方面通过PCB散热。

所以PCB的D-PAK焊盘有三处,漏极(D)焊盘较大。

2、SOT封装SOT(Small Out-Line Transistor)小外形晶体管封装。

这种封装就是贴片型小功率晶体管封装,比TO封装体积小,一般用于小功率MOSFET。

常见的规格有:主板上常用四端引脚的SOT-89 MOSFET。

3、SOP封装SOP(Small Out-Line Package)的中文意思是“小外形封装”。

SOP是表面贴装型封装之一,引脚从封装两侧引出呈海鸥翼状(L 字形)。

材料有塑料和陶瓷两种。

SOP也叫SOL和DFP。

SOP封装标准有SOP-8、SOP-16、SOP-20、SOP-28等等,SOP后面的数字表示引脚数。

MOSFET的SOP封装多数采用SOP-8规格,业界往往把“P”省略,叫SO(S mall Out-Line )。

SO-8采用塑料封装,没有散热底板,散热不良,一般用于小功率MOSFET。

SO-8是PHILIP公司首先开发的,以后逐渐派生出TSOP(薄小外形封装)、VSOP(甚小外形封装)、SSOP(缩小型SOP)、TSSOP(薄的缩小型SOP)等标准规格。

这些派生的几种封装规格中,TSOP和TSSOP常用于MOSFET封装。

4、QFN-56封装QFN(Quad Flat Non-leaded package)是表面贴装型封装之一,中文叫做四边无引线扁平封装,是一种焊盘尺寸小、体积小、以塑料作为密封材料的新兴表面贴装芯片封装技术。

现在多称为LCC。

QFN是日本电子机械工业会规定的名称。

封装四边配置有电极接点,由于无引线,贴装占有面积比QFP小,高度比QFP低。

这种封装也称为LCC、PCLC、P-LC C等。

QFN本来用于集成电路的封装,MOSFET不会采用的。

Intel提出的整合驱动与MOSFET的DrMOS采用QFN-56封装,56是指在芯片背面有56个连接Pin。

二、最新封装形式由于CPU的低电压、大电流的发展趋势,对MOSFET提出输出电流大,导通电阻低,发热量低散热快,体积小的要求。

MOSFET厂商除了改进芯片生产技术和工艺外,也不断改进封装技术,在与标准外形规格兼容的基础上,提出新的封装外形,并为自己研发的新封装注册商标名称。

下面分别介绍主要MOSFET厂商最新的封装形式。

1、瑞萨(RENESAS)的WPAK、LFPAK和LFPAK-I 封装WPAK是瑞萨开发的一种高热辐射封装,通过仿D-PAK封装那样把芯片散热板焊接在主板上,通过主板散热,使小形封装的WPAK也可以达到D-PAK的输出电流。

WPAK-D2封装了高/低2颗MOSFET,减小布线电感。

LFPAK和LFPAK-I是瑞萨开发的另外2种与SO-8兼容的小形封装。

LFPAK类似D-PAK比D-PAK体积小。

LFPAK-i是将散热板向上,通过散热片散热。

2、威世(Vishay)的Power-PAK和Polar-PAK封装Power-PAK是威世公司注册的MOSFET封装名称。

Power-PAK包括有Power-PAK1212-8、Power-PAK SO-8两种规格。

Polar PAK是双面散热的小形封装。

3、安森美(Onsemi)的SO-8和WDFN8扁平引脚( Flat Lead)封装安美森半导体开发了2种扁平引脚的MOSFET,其中SO-8兼容的扁平引脚被很多主板采用。

4、菲利普(Philps)的LFPAK和QLPAK封装首先开发SO-8的菲利普也有改进SO-8的新封装技术,就是LFPAK和QLPAK。

5、意法(ST)半导体的PowerSO-8封装法意半导体的SO-8改进技术叫做Power SO-8。

6、飞兆(Fairchild)半导体的Power 56封装飞兆半导体的SO-8改进技术叫做Power 56。

7、国际整流器(IR)的Direct FET封装Direct FET封装属于反装型的,漏极(D)的散热板朝上,并覆盖金属外壳,通过金属外壳散热。

三、内部封装技术前面介绍的最新封装形式都是MOSFET的外部封装。

这些最新封装还包括内部封装技术的改进,尽管这些新封装技术的商标名称多种多样,其内部封装技术改进主要有三方面:一是改进封装内部的互连技术,二是增加漏极散热板,三是改变散热的热传导方向。

1、封装内部的互连技术早期的标准封装,包括TO,D-PAK、SOT、SOP,多采用焊线式的内部互连,在CPU核心电压较高,电流较小时期,这种封装可以满足需求。

当 CPU供电进展到低电压、大电流时代,焊线式封装就难以满足了。

以标准焊线式SO-8为例,作为小功率MOSFET封装,发热量很小,对芯片的散热设计没有特别要求。

主板的局部小功率供电(风扇调速)多采用这种SO-8的MOSFET。

但用于现代的CPU供电就不能胜任了。

这是由于焊线式SO-8的性能受到封装电阻、封装电感、PN结到PCB和外壳的热阻等四个因素的限制。

封装电阻MOSFET在导通时存在电阻(RDS(on)),这个电阻包括芯片内PN结电阻和焊线电阻,其中焊线电阻占50%。

RDS(on)是影响MOSFET性能的重要因素。

封装电感内部焊线的引线框封装的栅极、源极和漏极连接处会引入寄生电感。

源极电感在电路中将会以共源电感形式出现,对MOSFET的开关速度有着重大影响。

芯片PN结到PCB的热阻芯片的漏极粘合在引线框上,引线框被塑封壳包围,塑料是热的不良导体。

漏极的热传导路径是芯片→引线框→引脚→PCB,这么长的路径必然是高热阻。

至于源极的热传导还要经过焊线到PCB,热阻更高。

芯片PN结到外壳(封装顶部)的热阻由于标准的SO-8采用塑料包封,芯片到封装顶部的传热路径很差。

上述四种限制对其电学和热学性能有着极大的影响。

随着电流密度要求的提高,MOSFET厂商采用SO-8的尺寸规格,同时对焊线互连形式进行改进,用金属带、或金属夹板代替焊线,降低封装电阻、电感和热阻。

国际整流器(IR)称之为Copper Strap技术,威世(Vishay)称之为Power Connect 技术,还有称之为Wireless Package。

据国际半导体报道,用铜带取代焊线后,热阻降低了10-20%,源极至封装的电阻降低了61%。

特别一提的是用铜带替换14根2-mil金线,芯片源极电阻从1.1 m降到 0.11 m。

2、漏极散热板标准SO-8封装采用塑料把芯片全部包围,低热阻的热传导通路只是芯片到PCB的引脚。

底部紧贴PCB的是塑料外壳。

塑料是热的不良导体,影响漏极的散热。

封装的散热改进自然是除去引线框下方的塑封混合物,让引线框金属结构直接(或者加一层金属板)与PCB接触,并焊接到PCB焊盘上。

它提供了大得多的接触面积,把热量从芯片上导走。

这种结构还有一个附带的好处,即可以制成更薄的器件,因为塑封材料的消除降低了其厚度。

威世的Power-PAK,法意半导体的Power SO-8,安美森半导体的SO-8 Flat Lead,瑞萨的WPAK、LFPAK,飞兆半导体的Power 56和Bottomless Package都采用这种散热技术。

3、改变散热的热传导方向Power-PAK封装显著减小了芯片到PCB的热阻,实现芯片到PCB的高效率传热。

不过,当电流的需求继续增大时,PCB也将出现热饱和,因此散热技术的进一步改进是改变散热方向,让芯片的热量传导到散热器而不是PCB。

瑞萨的LFPAK-I 封装,国际整流器的Direct FET封装就是这种散热技术。

三、内部封装技术前面介绍的最新封装形式都是MOSFET的外部封装。

这些最新封装还包括内部封装技术的改进,尽管这些新封装技术的商标名称多种多样,其内部封装技术改进主要有三方面:一是改进封装内部的互连技术,二是增加漏极散热板,三是改变散热的热传导方向。

1、封装内部的互连技术早期的标准封装,包括TO,D-PAK、SOT、SOP,多采用焊线式的内部互连,在CPU核心电压较高,电流较小时期,这种封装可以满足需求。