Circuit Envelope Simulation

spectresimulation介绍

schematic子菜单用来在电路原理图上选取要显示的 波形(点击连线选取节点电压,点击元件端点选取

节点电流),这个菜单比较常用

2021/4/2

30

第30页/共88页

其它有关的菜单项(3)

Outputs/Setup

2021/4/2

25

第25页/共88页

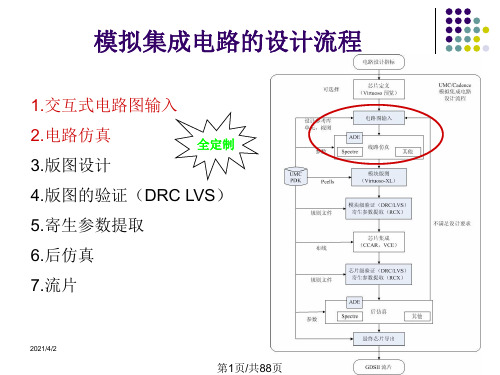

dc(直流分析)

dc(直流分析)可以在 直流条件下对

temperature,Design Variable,Component

Parameter,Model Parameter进行扫描仿真

举例:对温度的扫描(测 量温度系数)

电路随电源电压变化的 变化曲线等

2021/4/2

9

第9页/共88页

File菜单

在File菜单下,主要的菜单 项有New、Open、Exit等

New菜单项的子菜单下有 Library、Cell view两项。 Library项打开New Library窗 口,Cell view项打开Create New File窗口。

Open菜单项打开相应的 Open File窗口。

11

第11页/共88页

Tools菜单

在Tools菜单下,比较常 用的菜单项有

Library Manager

Library Path Editor

Technology File Manager

Library Manager项打开的是库管 理器。在窗口的各部分中,分别 显示的是Library、Category、Cell、 View相应的内容。

2021/4/2

15

第15页/共88页

ADS 小技巧

10Helpful Hints for using the HP Advanced Design SystemHINTSCONTENTSLearning to “Drive” Using the Keyboard (3)Using Templates or Copying Examples for More Efficient Simulation Set-up andData Display (4)Saving Mouse Clicks when Opening Projects (5)Renaming Ports on Schematics before Generating Subcircuits (6)Enabling Easy Display of Data (7)Efficiently Calculate Circuit Envelope Simulation Data (8)Using Short Cuts when Generating Schematics (9)Replacing MDS Wire Labels and Series IV Test Points with Node Names (10)Using New and Improved Data Display Capabilities (11)Managing Projects (12)Learning to “Drive” Using the KeyboardHINT1When you first learn to “drive”a software program, it is usu-ally easiest to use the mouse.As you become more of an expert user, however, it can often be faster to use the key-board to execute commands.Also, heavy software users who rely too much on mouse opera-tions run the risk of developing repetitive strain injuries.The HP Advanced Design Sys-tem has many built-in hot keys (Alt+f , for example, opens the File menu), and you can cus-tomize hot keys to perform operations that you use fre-quently .In the Options menu of the Main window or of a design window , the commandMenu/Toolbar Configurationopens the Customization dia-log box where you can custom-ize both hot keys and the tool bar configuration. In the Main window , you can customize Main window operations; in a design window , you can cus-tomize hot keys for that type of design (schematic and layout are set independently).Hot key suggestions for editing schematics:f for View All d for Redraw View z for Zoom Area 2 for Zoom Out x2e for Edit Component Param.t for Draw (insert) Text w for Component Wire (draw-ing wires between components)m for Move & Disconnect (inmost cases, this is preferable to the Move command, which causes wires to remain con-nected)ctrl+o for View/ Push Into Hier-archyUse F7 to launch simulations,and the escape key to termi-nate commands.F5 moves component text.After moving a component, it remains selected. To deselect it, just click on a blank spot in the schematic.Figure 1.Setting Schematic HotKeysall of the *.dds files in the example project are dis-played.8.Select the example.dds fileyou want to display , and open it.9.Copy and paste desiredplots, equations, etc., from the example.dds file into your data display window .Openingan Example Schematic from within a Project1.In a schematic window ,choose Window > Schematic .2.In the new Schematic win-dow , choose File > Open .3.In the Open Design dialogbox, click Browse .4.Traverse the directory treeto find the desired project and design.3.If you know the exampleproject path, you can type it in and skip the remain-ing steps. If you do not, go to the Main window and choose File >Copy Project .4.On the From Project: line,click on the Examples but-ton and then the Browse button.5.Traverse the examplesdirectory tree until the project that contains the data display that you want is entered in the Selection field of the Copy From File Browse dialog box.6.Clear the Filter field of theOpen data display dialog box.7.Highlight the exampleselection in the Copy From File Browse dialog box, and paste it into the Filter field of the Open data display dialog box. Append the suf-fix *.dds in this field, andWhen you set up a simulation, never start from scratch if you can avoid it.Often the fastest way to set up a simu-lation is to copy a schematic from an example or from another project.You can use any saved schematic or data display window as a template,including those in the program’s examples directory .You can also open a separate schematic window and display a schematic from an example or a different project.Viewing a Data DisplayUse the following steps to view a data display from an example file when you already have a data display open:1.In a Data Display window , chooseFile >New and open a new data dis-play window .2.In the new data display window ,choose File > Open.3.Define the directory, then click Filter todisplay the projects in4.Select a project,File > Copy Project7.Keep hierarchyin copy.8.Copy the project.6.Enter a name,5.To have the copy placed in a different directory than the original, click the desireddirectory type and Browse .Unless you specify a different directory , the copy is placed in the same directory as the project that was copied.2.Click Browse.1.Click the desired directory type.Figure 1.The Basics of Copying FilesHINT2Using Templates or Copying Examples for More EfficientSimulation Set-up and Data DisplaySaving Mouse Clicks when Opening ProjectsHINT3You can have the programreopen design windows for you when you reopen a project:1.In the Main Preferencesdialog box, select SaveProject Status on Exit(default is unselected).2.When you change projectsor exit the program, leave the design window(s) open that you want to see when you reopen the project.The next time you open the project, the last designs that where open will open automat-ically , saving you several mouse clicks.Figure 1.Saving Open DesignWindowsSelect this OptionHINT4Renaming Ports on Schematics before Generating SubcircuitsFigure 1.Schematic with Named PortsFigure 2. SymbolDesigners often use subcircuits to keep simulation set-ups easy to read. When you gener-ate a symbol for a subcircuit,you must place a port on the schematic at any input or out-put point, and the program provides the ports with default names (P1, P2, and so on).If you change the default names (to something moredescriptive such as Input, Out-put, Vplus, Vminus, for exam-ple), the names you give the ports appear on the subcircuit symbol when it is created. You may have to move the names on the symbol view so they do not overlap, but having the names on the symbol make it easier to correctly wire the sub-circuit into a higher-level cir-cuit.Enabling Easy Display of Data HINT5Using the shortest possiblevariable names in a data dis-play makes it easier to displaydata when you want to changedatasets. For example, after aharmonic balance simulation,instead of entering the equa-tion:Spectrum=dBm(SmampHBtest.HB1.HB1.HB.Vout)just enter the equation:Spectrum=dBm(Vout)This way, to display a spectrumusing a different dataset, allyou have to do is change thedataset name in the defaultdataset window. Using com-plete variable names (as in thefirst equation above)is neces-sary when you want to displaythe results of two differentsimulations simultaneously.ing Short Variable NamesHINT6Efficiently CalculateCircuit Envelope Simulation DataFigure ing an IntermediateVariableWhen doing calculations with or displaying Circuit Envelope data, calculations are much faster if you define an interme-diate variable. For example, if you simulate an amplifier with a digitally-modulated input signal in order to calculate the adjacent-channel power ratio or plot a trajectory diagram,you must extract the resulting fundamental frequencycomponent, which is a function of time. For example, to see the resulting output spectrum near the fundamental fre-quency ,use the following equations:Voutfund=Vout[1]Spectrum=dBm(0.5*fs(Voutfund,,,,,"Kaiser”))Trajectory=vs(imag(Voutfund),real(Voutfund))This will lead to faster data display calculations than using Vout[1] directly in all of the expressions.HINT Using Short Cuts whenGenerating Schematics7When you create a schematic,there are a couple techniquesthat can help speed things up:1.Copy components that youhave already placed on theschematic, rather thanplacing new ones (usingthe menus or palettes)each time.2.Enter component namesin the Component Historywindow. For example, typeR for resistor, and pressEnter. Then place the com-ponent in the schematic.You must type in the exactname of the component youwant; remember that ADSis case sensitive.3.Because the ComponentHistory window keeps alist of the components youplace in the schematic(after initially opening thewindow), if you see that aparticular component isClick here to display the drop-down list already in the schematic,you can click thedown-arrow next to theComponent History win-dow, select the desiredcomponent, and insert thepart in the schematic.ponent History Window with List of Placed ComponentsHINT8Replacing MDS Wire Labels and Series IV Test Points with Node NamesFigure 1.IF Output Schematic with NodeNamesWhere MDS uses wire labels to identify node voltages that are to be output to a dataset, and Series IV uses test points to identify node voltages to be used in calculations, theHP Advanced Design System uses node names.To insert a node name:1.Either select the “nodename” icon, which looks like a resistor with a rect-angle below it, or choose the command,Component >Node Name .2.Type in the name youwould like to attach to a particular node.3.Select a component pin.When placing a node name, you must select a component pin. In the HP Advanced Design Sys-tem 1.0, you cannot place node names on a wire,although this is anenhancement under con-sideration for a future release.DeletingYou do not delete a node name the same way you delete other components. Use the menu command:Edit >Component >Remove Node NameRenamingOnce you place a node name,you cannot edit its name. To change the name, simply insert a new node name with the desired name to the same node.Using New and ImprovedData Display CapabilitiesHINT9Data display has beenimproved over MDS and SeriesIV, although not all capabilitiesin MDS and Series IV areavailable in the first release ofthe HP Advanced Design Sys-tem. Some nice featuresinclude:•You can use markerread-outs in equations.For example, filter band-width or third-order inter-cept point of a mixer can becalculated from markerreadouts.•You can view matrices ofdata in tabular format,two-dimensions at a time.•To facilitate viewingresults, you can scrollthrough long lists of dataand plots.•Refer to the examples file/Tutorial/express_meas_prjfor many interesting anduseful ways to manipulatesimulation results.•When you run a swept sim-ulation, such as CircuitEnvelope, the node volt-ages and other variablesoutput to the dataset aremulti-dimensional. Use thewhat function to see theindependent variables andtheir dimensionality.Figure1.Plots from ConstEVM.ddsin/examples/RF_Board/NADC_PA_prj Figure 2. Using the whatFunctionUse ModelA basic HP Advanced Design System use model is as follows:1.You create a schematic andthen run a simulation,which generates a dataset.The dataset is written into the data directory with a .ds suffix.2.You open a data displaywindow to view the results of the simulation.3.After viewing the simula-tion results, you may save the data display window as a .dds file.Some users find it easiest to keep schematic,dataset, and data display names identical. This way ,it is easy to determine which simulation set-up was used to generate a par-ticular data display .HINT10Managing ProjectsHP Advanced Design System projects are organized as shown in this exam-ple (CDMAsrc_prj ):DataSrcTest.dds RevLinkSrc.dds dataDataSrcTest.ds RevLinkSrc.ds mom_dsn networksDataSrcTest.ael, etc.RevLinkSrc.ael, etc.synthesis verificationThere are other files as well, and they are documented in the program manu-als.Simulation data Designs Momentum data DSP synthesis DRC dataCurrent project directoryThis area displays any hierarchy in the current project.Current directory pathThe Mainwindow displays the directories that are created for a new projecfCategorizing DesignsWhat do you do if you decide that the numerous schematics in a particular project need to be categorized into subdirecto-ries for better organization?The program does not allow subdirectories in the networks directory , so something else must be done. Here are two solutions:•In the Main window , copy the project (File > Copy Project ), and deleteunwanted designs from the new project (File > Delete Design ).To delete unwanteddatasets, use the Data Dis-play window command File >Delete Dataset .If you have subcircuits that you want to be able to access from two projects,but you do not want to keep two copies, select File >Open then FileInclude >Remove Projects to enable you to access designs in project B from project A.•Alternatively , you can cre-ate a new project and just copy designs from the orig-inal project into the new one (Copy Design in the Main window).You will have to use an operating system file man-ager to move or copydatasets and data display files.Figure 1.A Typical Directory/go/hpeesof Data subject to change.The Competitive AdvantageHP EEsof’s EDA tools are developed for today’s designers building tomorrow’s communications products. From DSP and RFIC design to device modeling andconsulting services, HP EEsof offers a full array of design tools to streamline your product development process.For more information, call the local HP sales office below or the nearest listing in your telephone directory.United StatesHewlett-Packard CompanyTest and Measurement Organization 5301 Stevens Creek Blvd., Bldg. 51L-SC Santa Clara, CA 95052-8059tel: (800)452-4844 (tool free)CanadaHewlett-Packard Canada Ltd.5150 Spectrum WayMississauga, Ontario L4W 5G1tel: (905) 206-4725EuropeHewlett-PackardEuropean Market Centre P .O. Box 9991180 AZ Amsteelveen The Netherlands tel: (31) 20-547-9900JapanHewlett-Packard Japan Ltd.Measurement Assistance Center 9-1, Takakura-Cho, Hachioje-Shi,Tokyo 192, Japan tel: (905) 206-4725Latin America Hewlett-PackardLatin American Region Headquarters 5200 Blue Lagoon Drive, 9th Floor Miami, Florida 33126 U.S.A.tel: (305) 267-4245/4220Asia PacificHewlett-Packard Asia Pacific Ltd.17-21 /F Shell Tower, Times Square 1 Matheson Street, Causeway Bay Hong Kongtel: (852) 2599-7889fax: (852) 2506-9233Australia/New ZealandHewlett-Packard Australia Ltd.31-41 Joseph StreetBlackburn, Victoria 3130Australiatel: (800) 629-485 (toll free)fax: (61-3) 9899-372。

ADS软件的使用手册编写及应用_1_

ADS软件的使⽤⼿册编写及应⽤_1_ADS软件的使⽤⼿册编写及应⽤⼀.关于ADS软件⼀)ADS中的projects当⽤户对ADS中的designs进⾏建⽴,模拟和分析以完成设计任务时,将会产⽣⼀定量的数据,⽽projects正是对这些数据进⾏⾃动的组织和存储。

⼀个project包括:电路(circuit),版⾯(layout),模拟(simulation),分析(analysis)以及由于⽤户建⽴的designs和projects之间的连结⽽产⽣的designs的输出信息。

使⽤ADS的主窗⼝可以建⽴或打开projects。

当⽤户登陆ADS时,主窗⼝将被打开。

⼆)ADS中的designsADS中的designs是⽤来存储⽤户为完成设计任务⽽⽣成的原理图及版⾯设计信息。

⼀个designs包括:⼀个单独的原理图或电路图,或者包括若⼲原理图或电路图嵌⼊式的包含于⼀个单独的design中。

所有的designs都可以直接从主窗⼝打开或者从design窗⼝打开。

在⼀个design窗⼝中,⽤户可以做以下事情:建⽴或修改电路图和布线图增加变量和等式配置电路元件和模拟控制器制定版⾯,选择参数添加注释以及例证从电路中产⽣版⾯(版⾯中产⽣电路图)三)ADS中的模拟ADS软件提供模拟控制器功能,以便⽤户可以添加或配置模拟来测试⽤户的设计。

对于DSP设计来说,当⼀个模拟/射频设计仿真需要⼀个或多个不同的控制器时,就需要⼀个数据流控制器。

⽤户可以⾃⼰添加合适的控制器,也可以插⼊⼀个包含合适控制器的模板(template)。

模拟控制器的分类:1.数据流控制器:在使⽤Agilent Ptolemy模拟器时,⽤来控制混合同步数字信号来进⾏数字信号处理。

适⽤于所有的DSP设计。

2.DC :是射频/模拟电路设计模拟的基本控制器,提供拓扑检测和直流分析的功能。

适⽤于所有的射频/模拟设计。

3.AC:获得⼩信号转换参数,如电压增益,电流增益,线性电压或电流噪声。

ADS软件使用教程3

QUIZ: Is this valid?

C coupling_c C=x Next, preferences...

Schematic Preferences are available

Steps in the Design Process: labs 2-9

You are here:

Now its time to model the transistor as a sub-circuit and create a bias network that will be the core of the amplifier. • Design the RF sys behavioral model receiver • Test conversion gain, spectrum, etc. • Start amp_1900 design – subckt parasitics • Simulate amp DC conditions & bias network • Simulate amp AC response - verify gain • Test for noise contributions • Simulate amp S-parameter response • Create a matching topology • Optimize the amp in & out matching networks • Filter design – lumped 200MHz LPF • Filter design – microstrip 1900 MHz BPF • Transient and Momentum filter analysis • Amp spectrum, delivered power, Zin - HB • Test amp comp, distortion, two-tone, TOI • CE basics for spectrum and baseband • CE for amp_1900 with GSM source • Replace amp and filters in rf_sys receiver • Test conversion gain, NF, swept LO power • Final CDMA system test CE with fancy DDS • Co-simulation of behavioral system

仿真一般原则【转贴】

仿真⼀般原则【转贴】感谢原创作者!电路仿真,⽆论在ADS还是spectreRF/spectre中,某种类型电路(譬如mixer、LNA、VCO等)原本该选择什么类型仿真(譬如Tran、PSS、HB、Env等)就先选择那种类型仿真,得到想要的结果(譬如噪声、频谱、增益、S参数等)。

但是,⼀种情况,遇到仿真时间过长(譬如⼏天,以致⽆法容忍)的时候,不妨尝试另⼀种仿真类型,譬如Tran仿真消耗时间太长,那么可以考虑Env,PSS仿真时间过长也以考虑Env。

当然,这种情况下,还应该考虑仅仿真所需数据,不需要观察输出的数据点应当在仿真之初就设置不要,譬如PSP和PAC的噪声仿真差异。

另外⼀种情况,当常规类型仿真⽆法收敛的时候,不妨尝试另⼀种仿真类型,譬如PSS在信号源是数字调制的电路中或者输⼊信号源是周期的但输出却杂乱⽆章的电路中,PSS或失效或效率低下,此时,选择Env可能奏效,最坏情况下再选择Tran(最多牺牲时间)也应该满⾜要求。

注意每种类型仿真都有其适应的条件(譬如PSS的周期性和近似线性、Env的频谱占有率⾼但是空隙⼤),满⾜这个条件,则仿真⾼效率运⾏;不满⾜,即便满负荷运⾏完毕,也得不到想要观察的数据。

仿真只是⼀个⼯具,在熟练应⽤⼯具的基础上,不沉溺于⼯具本⾝,但是也不强调⼯具⽆⽤论。

电路、系统理论掌握是基础、是根本,⼯具起到辅助作⽤。

适当的了解⼯具运⾏原理,知其所以然,会使其⽤起来更为得⼼应⼿,⽆论仿真中遇到什么问题都能果断推测源头所在,⽽不是盲⽬改电路或者改仿真设置。

我以为,⼯具应⽤的最⾼境界,就是看完⼀个电路,能估计出某种合适的仿真需要花费多久时间,最为致效。

这就需要知道电路中计算⽅程的数量、计算机本⾝硬件开销、仿真算法的重复次数以致满⾜收敛误差。

通常不需要了解这么多。

spectreRF Summary1. Noise FigureQPSS and QPnoise:当输⼊出现两个⼤的⼲扰信号的时候,⽤此分析来决定NF;PSS and Pnoise:当输⼊没有⼲扰信号存在的时候,⽤此分析来决定NF;PSS and PSP:即可奏效;SP:即可奏效;2. HarmonicsPSS:单纯的基于输⼊的点频来输出频谱成分(区别于输⼊扫描),即可以单⼀输⼊频率,⼜可以多个输⼊频率(在信号源中设置即可),都将产⽣指定数量的谐波成分,分析各次谐波、交调结果。

ADS教程第9章

实验九、最终系统和电路仿真概述这是最后一个实验,把课程中的所有电路放在一起:放大器和滤波器。

它们代替了在前面实验中使用的特性(behavioral)系统模型。

任务●在系统中为1900MHz放大器构造一个子电路。

●使用Smart Simulation Wizard(灵活仿真魔术棒)。

●建立一个具有GSM源的谐波平衡仿真,并对它进行仿真。

●用CDMA源建立并运行一个CE仿真。

●运用一个数据显示例子,对ACPR和功率谱进行仿真。

●编程Marker sliders(游标)来规范(customize)数据显示。

●选作:具有最少指示的联合仿真。

目录1.为库创建最终Amp_1900子电路 (148)2.用灵活仿真魔术棒(Smart Simulation Wizard)对AMP_1900进行仿真 (149)3.创建一个由扫描LO的HB(谐波平衡)最终原理图和方程 (153)4.谐波平衡(HB)最终仿真:具有本振功率和噪音扫描的双音分析 (155)5.查看NF,Conv Gain,dbm_out和IF gain并作图 (157)6.最终的包络仿真:CDMA源 (157)7.打开一个DDS的例子,对ACPR和功率谱作图 (158)8.用一个编程的游标(marker slider)作频谱图 (160)9.选作:RF特性系统的联合仿真 (162)步骤1.为库创建最终AMP_1900子电路a.用一个新名AMP_1900保存最后的放大器电路包络设计(ckt_env_gsm),这个原理图将成为一个你的系统任务中要用到最终的放大器设计。

b.如图所示.删去所有的仿真控制元件、变量、源等。

设置Vdc=5V。

在File>Design Parameters中将元件实例名改为AMP_1900,符号名为SYM_Amplifier。

同时,确定放置端口连结器(port connector)1和2到输入输出端。

检查电路并保存和关闭AMP_1900设计。

Advanced Circuit Simulation软件用户指南说明书

.SNNOISERuns periodic AC noise analysis on nonautonomous circuits in a large-signal periodic steady state..SNNOISE output insrc frequency_sweep [N1, +/-1]+ [LISTFREQ=(freq1 [freq2 ... freqN ]|none|all]) [LISTCOUNT=num ]+ [LISTFLOOR=val ] [LISTSOURCES=on|off].HBAC / .SNACRuns periodic AC analysis on circuits operating in a large-signal periodic steady state..HBAC frequency_sweep .SNAC frequency_sweep.HBXF / .SNXFCalculates transfer function from the given source in the circuit to the designated output..HBXF out_var frequency_sweep .SNXF out_var frequency_sweep.PTDNOISECalculates the noise spectrum and total noise at a point in time..PTDNOISE output TIME=[val |meas |sweep ] +[TDELTA=time_delta ] frequency_sweep+[listfreq=(freq1 [freq2 ... freqN ]|none|all)] [listcount=num ]+[listfloor=val ] [listsources=on|off]RF OptionsSIM_ACCURACY=x Sets and modifies the size of the time steps. The higher the value, thegreater the accuracy; the lower the value, the faster the simulation runtime. Default is 1.TRANFORHB=n 1 Forces HB analysis to recognize or ignore specific V/I sources, 0 (default) ignores transient descriptions of V/I sources.HBCONTINUE=n Specifies whether to use the sweep solution from the previous simulation as the initial guess for the present simulation. 0 restarts each simulation in a sweep from the DC solution, 1 (default) uses the previous sweep solution as the initial guess.HBSOLVER=n Specifies a preconditioner for solving nonlinear circuits. 0 invokes the direct solver. 1 (default) invokes the- matrix-free Krylov solver. 2 invokes the two-level hybrid time-frequency domain solver.SNACCURACY=n Sets and modifies the size of the time steps. The higher the value, the greater the accuracy; the lower the value, the faster the simulation runtime. Default is 10.SAVESNINIT=”filename ” Saves the operating point at the end of SN initialization.LOADSNINIT=”filename ” Loads the operating point saved at end of SN initialization.Output Commands.BIASCHK .MEASURE .PRINT .PROBEFor details about all commands and options, see the HSPICE ® Reference Manual: Commands and Control Options.Synopsys Technical Publications 690 East Middlefield Road Mountain View, CA 94043Phone (650) 584-5000 or (800) Copyright ©2017 Synopsys, Inc. All rights reserved.Signal Integrity Commands.LINCalculates linear transfer and noise parameters for a general multi-port network..LIN [sparcalc [=1|0]] [modelname=modelname ] [filename=filename ]+ [format=selem|citi|touchstone|touchstone2] [noisecalc [=1|0]]+ [gdcalc [=1|0]] [dataformat=ri|ma|db]+ [listfreq=(freq1 [freq2 ... freqN ]|none|all)] [listcount=num ]+ [listfloor=val ] [listsources=1|0|yes|no].STATEYEPerforms Statistical Eye Diagram analysis..STATEYE T=time_interval Trf=rise_fall_time [Tr=rise_time ] + [Tf=fall_time ] Incident_port=idx1[, idx2, … idxN ]+ Probe_port=idx1[, idx2, … idxN ] [Tran_init=n_periods ] + [V_low=val ] [V_high=val ] [TD_In=val ] [TD_PROBE=val ]+ [T_resolution=n ] [V_resolution=n ] [VD_range=val ]+ [EDGE=1|2|4|8] [MAX_PATTERN=n ] [PATTERN_REPEAT=n ] + [SAVE_TR=ascii] [LOAD_TR=ascii] [SAVE_DIR=string ]+ [IGNORE_Bits=n ] [Tran_Bit_Seg=n ]+ [MODE=EDGE|CONV|TRAN] [XTALK_TYPE = SYNC|ASYNC|DDP|NO|ONLY]+ [Unfold_Length=n ] [TXJITTER_MODE = 1|2]RF Analysis Commands.ACPHASENOISEHelps interpret signal and noise quantities as phase variables for accumulated jitter for closed-loop PLL analysis..ACPHASENOISE output input [interval ] carrier=freq+ [listfreq=(freq1 [freq2 ... freqN ]|none|all)][listcount=num ]+ [listfloor=val ] [listsources=1|0].HBRuns periodic steady state analysis with the single and multitone Harmonic Balance algorithm..HB TONES=F1[,F2,…,FN ] [SUBHARMS=SH ] [NHARMS=H1[,H2,…,HN ]]+ [INTMODMAX=n ] [SWEEP parameter_sweep ].SNRuns periodic steady state analysis using the Shooting Newton algorithm..SN TRES=Tr PERIOD=T [TRINIT=Ti ] [MAXTRINITCYCLES=integer ]+ [SWEEP parameter_sweep ] [NUMPEROUT=val ].SN TONE=F1 [TRINIT=Ti ] NHARMS=N [MAXTRINITCYCLES=integer ]+ [NUMPEROUT=val ] [SWEEP parameter_sweep ].HBOSC / .SNOSCPerforms analysis on autonomous oscillator circuits..HBOSC TONE=F1 NHARMS=H1+ PROBENODE=N1,N2,VP [FSPTS=NUM,MIN,MA X]+ [SWEEP parameter_sweep ] [SUBHARMS=I ] [STABILITY=-2|-1|0|1|2].SNOSC TONE=F1 NHARMS=H1 [TRINIT=Ti ]+ [OSCTONE=N ] [MAXTRINITCYCLES=N ]+ [SWEEP parameter_sweep ].PHASENOISEInterprets signal / noise quantities as phase variables for accumulated jitter in closed-loop PLL analysis..PHASENOISE output frequency_sweep [method= 0|1|2]+ [listfreq=(freq1 [freq2 ... freqN ]|none|all)] [listcount=num ]+ [listfloor=val ] [listsources=1|0] [carrierindex=int ].HBNOISEPerforms cyclo-stationary noise analysis on circuits in a large-signal periodic steady state..HBNOISE output insrc parameter_sweep [N1, N2, ..., NK ,+/-1]+ [LISTFREQ=(freq1 [freq2 ... freqN ]|none|all]) [LISTCOUNT=num ]+ [LISTFLOOR=val ] [LISTSOURCES=on|off].NOISERuns noise analysis in frequency domain..NOISE v(out ) vin [interval ] [listckt[=1|0]]+ [listfreq=freq1 [freq2 ... freqN ]|none|all]) [listcount=num ]+ [listfloor=val ] [listsources=1|0|yes|no]] [listtype=1|0].ALTERReruns a simulation using different parameters and data from a specified sequence or block. The .ALTER block can contain element commands and .AC, .ALIAS, .DATA, .DC, .DEL LIB, .HDL, .IC (initial condition), .INCLUDE, .LIB, .MODEL, .NODESET, .OP, .OPTION, .PARAM, .TEMP, .TF, .TRAN, and .VARIATION commands..ALTER title_string.DCPerforms DC analyses..DC var1 START=start1 STOP=stop1 STEP=incr1Parameterized Sweep.DC var1 start1 stop1 incr1 [SWEEP var2 type np start2 stop2].DC var1 START=[par_expr1] STOP=[par_expr2] STEP=[par_expr3]Data-Driven Sweep.DC var1 type np start1 stop1 [SWEEP DATA=datanm (Nums )].DC DATA=datanm [SWEEP var2 start2 stop2 incr2].DC DATA=datanm (Nums )Monte Carlo Analysis.DC var1 start1 stop1 incr1 [SWEEP MONTE=MCcommand ].DC MONTE=MCcommand.OPCalculates the operating point of the circuit..OP format_time format_time ... [interpolation].PARAMDefines parameters. Parameters are names that have associated numeric values or functions..PARAM ParamName = RealNumber | ‘AlgebraicExpression’ | DistributionFunction (Arguments ) | str(‘string’) | OPT xxx (initial_guess, low_limit, upper_limit )Monte Carlo Analysis.PARAM mcVar = UNIF(nominal_val , rel_variation [, multiplier ]) | AUNIF(nominal_val , abs_variation [, multiplier ])| GAUSS(nominal_val , rel_variation , num_sigmas [, multiplier ]) | AGAUSS(nominal_val , abs_variation , num_sigmas [, multiplier ]) | LIMIT(nominal_val , abs_variation ).STOREStarts creation of checkpoint files describing a running process during transient analysis..STORE [file=checkpoint_file ] [time=time1]+ [repeat=checkpoint_interval ].TEMPPerforms temperature analysis at specified temperatures..TEMP t1 [t2 t3 ...].TRANPerforms a transient analysis.Single-Point Analysis.TRAN tstep1 tstop1 [START=val ] [UIC]Multipoint Analysis.TRAN tstep1 tstop1 [tstep2 tstop2 ... tstepN tstopN ]+ RUNLVL =(time1 runlvl1 time2 runlvl2...timeN runlvlN )+ [START=val ] [UIC] [SWEEP var type np pstart pstop ]Monte Carlo Analysis.TRAN tstep1 tstop1 [tstep2 tstop2 ... tstepN tstopN ]+ [START=val ] [UIC] [SWEEP MONTE=MCcommand ]Invoking HSPICESimulation Modehspice [-i] input_file [-o [output_file ]] [-hpp] [-mt #num ][-gz] [-d] [-case][-hdl filename ] [-hdlpath pathname ] [-vamodel name ]Distributed-Processing Modehspice [-i] input_file [-o [output_file ]] -dp [#num ][-dpconfig [dp_configuration_file ]] [-dplocation [NFS|TMP][-merge]Measurement Modehspice -meas measure_file -i wavefile -o [output_file ]Help Modehspice [-h] [-doc] [-help] [-v]Argument Descriptions-i input_file Specifies the input netlist file name.-o output_file Name of the output file. HSPICE appends the extension .lis.-hpp Invokes HSPICE Precision Parallel.-mt #num Invokes multithreading and specifies the number of processors. Works best when -hpp is used.-gz Generates compression output on analysis results for these output types: .tr#, .ac#, .sw#, .ma#, .mt#, .ms#, .mc#, and .print*.-d (UNIX) Displays the content of .st0 files on screen while running HSPICE.-case Enable case sensitivity.-hdl filename Specifies a Verilog-A file.-hdlpath pathname Specifies the search path for Verilog-A files.-vamodel name Specifies the cell name for Verilog-A definitions.-dp #num -dpconfig dpconfig_file -dplocation [NFS|TMP] Invokesdistributed processing and specifies number of processes, the configuration file for DP, and the location of the output files.-merge Merge the output files in the distributed-processing mode.-meas measure_file Calculates new measurements from a previous simulation.-h Outputs the command line help message.-doc Opens the PDF documentation set for HSPICE (requires Adobe Acrobat Reader or other PDF document reader).-help Invokes the online help system (requires a Web browser).-v Outputs HSPICE version information.HSPICE is fully integrated with the Synopsys® Custom Compiler™ Simulation and Analysis Environment (SAE). See the Custom Compiler™ Simulation and Analysis Environment User Guide .To use the HSPICE integration to the Cadence® Virtuoso® Analog Design Environment, go to /$INSTALLDIR/interface/ and follow the README instructions.Analysis Commands.ACPerforms AC analyses.Single / Double Sweep.AC type np fstart fstop.AC type np fstart fstop [SWEEP var+ [START=]start [STOP=]stop [STEP=]incr ].AC type np fstart fstop [SWEEP var type np start stop ]Sweep Using Parameters.AC type np fstart fstop [SWEEP DATA=datanm (Nums )].AC DATA=datanm.AC DATA=datanm [SWEEP var [START=]start [STOP=]stop [STEP=]incr ].AC DATA=datanm [SWEEP var type np start stop ]Monte Carlo Analysis.AC type np fstart fstop [SWEEP MONTE=MCcommand ].LSTBInvokes loop stability analysis..LSTB [lstbname ] mode=[single|diff|comm + vsource=[vlstb |vlstbp,vlstbn ]Data-Driven Sweep.TRAN DATA=datanm.TRAN DATA=datanm [SWEEP var type np pstart pstop ].TRAN tstep1 tstop1 [tstep2 tstop2 ... tstepN tstopN ]+ [START=val ] [UIC] [SWEEP DATA=datanm (Nums )]Time Window-based Speed/Accuracy Tuning by RUNLVL.TRAN tstep tstop [RUNLVL=(time1 runlvl1...timeN runlvlN )]Circuit Block-based Speed/Accuracy Tuning by RUNLVL.TRAN tstep tstop+ [INST=inst_exp1 RUNLVL=(time11 runlvl11...time1N runlvl1N )]+ [SUBCKT=subckt_exp2 RUNLVL=(time21 runlvl21...time2N runlvl2N )]Time Window-based Temperature Setting.TRAN tstep tstop [tempvec=(t1 Temp1 t2 Temp2 t3 Temp3...)+[tempstep=val ]].TRANNOISEActivates transient noise analysis to compute the additional noise variables over a standard .TRAN analysis..TRANNOISE output [METHOD=MC] [SEED=val ] [SAMPLES=val ] [START=x ]+ [AUTOCORRELATION=0|1|off|on] [FMIN=val ] [FMAX=val ] [SCALE=val ]+ [PHASENOISE=0|1|2] [JITTER=0|1|2] [REF=srcName ] [PSD=0|1]HSPICE Options.OPTION opt1 [opt2 opt3 …]opt1 opt2 … Specify input control options.General OptionsALTCC=n Enables reading the input netlist once for multiple .ALTER statements. Default is 0.LIS_NEW=x Enables streamlining improvements to the *.lis file. Default is 0. SCALE=x Sets the element scaling factor. Default is 1.POSTTOP=n Outputs instances up to n levels deep. Default is 0.POSTLVL=n Limits data written to the waveform file to the level of nodes specified by n .POST=n Saves results for viewing by an interactive waveform viewer. Default is 0.PROBE=n Limits post-analysis output to only variables specified in .PROBE and .PRINTstatements. Default is 0.RC Reduction OptionsSIM_LA=name Starts linear matrix (RC) reduction to the PACT, PI, or LNE algorithm. Defaultis off.Transient OptionsAUTOSTOP=n Stops transient analysis after calculating all TRIG-TARG, FIND-WHEN, andFROM-TO measure functions. Default is 0.METHOD=name Sets numerical integration method for a transient analysis to GEAR, or TRAP(default), or BDF.RUNLVL=n Controls the speed and accuracy trade-off; where n can be 1 through 6. The higher the value, the greater the accuracy; the lower the value, the faster the simulation runtime. Default is 3.Variability and Monte Carlo Analysis.AC .DC .TRAN .MEASURE .MODEL .PARAM .ACMATCHCalculates the effects of variations on the AC transfer function, with one or more outputs..ACMatch Vm(n1) Vp(n1) Vr(n1) Vi(n1) Vm(n1,n2) Im(Vmeas ).DCMATCHCalculates the effects of variations on the DC operating point, with one or more outputs..DCMatch V(n1) V(n1,n2) I(Vmeas )。

ADS软件介绍与入门

三、ADS软件介绍与入门

3.6.4 创建和打开ADS设计

ADS使用project(工程或项目)来组织和存储为设计生成的原理图和 版图等信息。一个project可以由单个的原理图或版图组成,也可以由多 个原理图或版图及其包含的内部子电路的原理图和版图组成。项目中的所 有设计都可以直接从主窗口或从一个设计窗口内显示和打开。

开关电路

三、ADS软件介绍与入门

3.3 ADS所提供的辅助设计功能

✓设计指南(Design Guide) ✓仿真向导(Simulation Wizard) ✓仿真与结果显示模板(Simulation & Data Display Template) ✓电子笔记本(Electronic Notebook)

用于分析混频器的谐波,是用户定义的混频交调产 System-Data Models库中的MixerIMT、

物的构成表。

MIXERIMT2

三、ADS软件介绍与入门

格式 MODEL_MDIF

P2D

S2D

S2PMDIF SDF SPW TIM

功能描述

所在模型库及使用

非线性模型参数

EEFET1,BJTAP等等。

用户定义,部分明白的线性概率密度函数数据。

同Statistic标签中的表达式。

采用了MDIF格式的系统生成的小信号S参数文件(带有增益压 缩的2端口S、H、Y、Z或G参数)。可以描述小信号数据,噪 声数据,非线性数据和交调数据;也可以把非线性描述为驱 动功率的或者是三阶交调截点、1dB增益压缩点、饱和功率、 饱和时增益压缩几个参数的综合表示的函数。

三、ADS软件介绍与入门

3.4 ADS与其他EDA软件和测试设备间的连接

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ADS 2002 Fundamentals - April, 2002

Slide 8 - 13

Optional - channel power calculation

On a new page in DDS, write two equations: limits defines the bandwidth and channel_pwr calculates power in the channel.

Slide 8 - 6

Envelope Setup tab in the controller

Example: one tone with 3 harmonics Stop time – Determines resolution bandwidth of output spectrum – Large enough to resolve spectral components of interest Time step – Determines bandwidth of Circuit Envelope simulation – Small enough to capture highest modulation frequency

ADS 2002 Fundamentals - April, 2002

Slide 8 - 2

Test circuits with realistic signals

GSM, CDMA, GMSK, pi/4DQPSK, QPSK, etc.

Simulations can include:

– – – – –

Example CE results:

32.8 kHz BW for NADC

Adjacent Channel Power Ratio Noise Power Ratio Error Vector Magnitude Power Added Efficiency Bit Error Rate

2-tone tests and linearized models do not predict this behavior as easily!

•mag of Vin [1]: envelope • ts of Vout: signal • mag of Vout [1]: envelope

...where [1] is the carrier: Freq[1].

Next, the controller setup...

ADS 2002 Fundamentals - April, 2002

Slide 8 - 8

What the lab is about ...

Lab 8:

Circuit Envelope Simulations

ADS 2002 Fundamentals - April, 2002

Slide 8 - 9

Steps in the Design Process

• Design the RF sys behavioral model receiver • Test conversion gain, spectrum, etc. • Start amp_1900 design – subckt parasitics • Simulate amp DC conditions & bias network • Simulate amp AC response - verify gain • Test amp noise contributions – tune parameters • Simulate amp S-parameter response • Define amp matching topology and tune input • Optimize the amp in & out matching networks • Filter design – lumped 200MHz LPF • Filter design – microstrip 1900 MHz BPF • Transient and Momentum filter analysis • Amp spectrum, delivered power, Zin - HB • Test amp comp, distortion, two-tone, TOI • CE basics for spectrum and baseband • CE for amp_1900 with GSM source • Replace amp and filters in rf_sys receiver • Test conversion gain, NF, swept LO power • Final CDMA system test CE with fancy DDS • Co-simulation of behavioral system

Harmonic Balance

Example: multiple tones with mixing

t0 t1 t2 t3 t4

Multiple tone simulation requires more time and more data display memory.

ADS 2002 Fundamentals - April, 2002

ADS 2002 Fundamentals - y, use AMP_1900 with the GSM source

variable t_step = 1 / (5X BW of GSM)

Plot the GSM spectrum

Verify baseband integrity using an equation to demodulate the signal:

You will do this in the lab!

Step time is critical for sampling the envelope: rise, fall, and modulation rate. Therefore, Step (sample time) is NOT the same as Transient.

• Output a time-varying spectrum • Use equations on the data • Faster than HB or Spice in many cases • Integrates with System Simulation & HP Ptolemy

Next, what tests can it perform?

Modulation

t2

t1

t4

Carrier

Periodic input signal

NOTE: V(t) can be complex - am or fm or pm

ADS 2002 Fundamentals - April, 2002

Slide 8 - 4

…more on CE Technology

Plot:bits_out and fm_demod

Plot the GSM BW spectrum with with and without windowing.

Also, insert a filter at Vin to alter the phase. See the difference at fm_demods.

Topic 8:

Circuit Envelope Simulation

ADS 2002 Fundamentals - April, 2002

Slide 8 - 1

What is Circuit Envelope ?

• Time samples the modulation envelope (not carrier) • Compute the spectrum at each time sample

Also, Envelope can be used for PLL simulations: lock time, spurious signals, modulation in the loop.

890 MHz

carrier

Next, how it works...

ADS 2002 Fundamentals - April, 2002

Next, an example...

Captures time and frequency characteristics:

dBm (fs (Vout))

ADS 2002 Fundamentals - April, 2002

Slide 8 - 5

Example: AMP with RF pulse

No need to resimulate, simply use Vout[1] which is 1900 MHz!

Start the lab now!

ADS 2002 Fundamentals - April, 2002

Slide 8 - 14

You are here:

ADS 2002 Fundamentals - April, 2002

Slide 8 - 10

First, simulate using an RF pulse

Use a behavioral amp and different time steps:

1 nsec vs 10 ns

Slide 8 - 3

Circuit Envelope Technology

Circuit

Vout Time sample the envelope and then perform Harmonic Balance on the samples!

More...

V(t) * e j2π fot