计算机组成原理期末复习资料-王爱英

计算机组成原理王爱英(清华)(2)

虚拟机器 M3 (汇编语言或中

间机器语言)

本 级 语 言程 序 经编 译 程 序翻 译 成 机器语言程序或操作系统语言

虚拟机器 M2 (操作系统 语言机器) 间机器语言)

一般用机器语言解释操作系统语言

实际机器 M1 (机器语言机器)

由 硬 件 或 微 程 序 *执 行 机 器 语 言

*注 : 微 程 序 将 在 第 6 章 中 讲 述

Cray-1,Cray-2,Cray-3,国产银河I, 银河II, 银河III

• 小巨型机——功能同巨型机相近,价格相对便宜,发展十分迅速

美国Convex公司的C系列机为其代表产品。

• 大型机——大中型企事业单位作为计算中心的主机使用,统一调

度主机资源,代表产品有IBM360,370,4300等。 • 小型机——它可以满足部门性的需求,供小型企事业单位使用,

• 存储器用来存放程序和数据,是计算机各种信息的存储和交流 中心。存储器可与CPU、输入输出设备交换信息,起存储、缓冲、 传递信息的作用,

• 中央处理器又叫CPU,在早期的计算机中分成运算器和控制器两 部分,由于电路集成度的提高,现在已把它们集成在一个芯片中。

• 在计算机中各部件间来往的信号可分成三种类型,即地址、数据 和控制信号。通常这些信号是通过总线传送的, CPU发出的控制 信号,经控制总线送到存储器和输入输出设备,控制这些部件完 成指定的操作。与此同时,CPU(或其他设备)经地址总线向存

储器或输入输出设备发送地址,A 使得计算机各个部件中的数3 据能 根据需要互相传送。

1.3 计算机系统的层次结构(从语言功能层次划分)

虚拟机:通过配置软件扩展功能后形成的与实际机无关的 机器。它将提供给用户的功能抽象出来,脱离了物理机。

计算机组成原理王爱英(清华)

2)十进制转换成二进制方法

一般分为两个步骤:

• 整数部分的转换

– 除2取余法(基数除法) – 减权定位法

• 小数部分的转换

– 乘2取整法(基数乘法)

除基取余法:把给定的除以基数,取余数作为最低位的 系数,然后继续将商部分除以 基数,余数作为次低位 系数,重复操作直至商为 0

例如:用基数除法将(327)10转换成二进制数 2 2 2 2 2 2 2 2 2 2 327 163 81 40 20 10 5 2 1 0 余数 1 1 1 0 0 0 1 0 1 2

例如: (7AC.DE ) 16 =(0111,1010,1100.1101,1110 ) 2 =(11110101100 .1101111 )2

3、 数值符号的表示

带符号数的编码 名词解释:真值和机器数 • 真值:正、负号加某进制数绝对值的形 式称为真值。如二进制真值: • X=+1011 y=-1011 • 机器数:符号数码化的数称为机器数 如 :X=01011 Y=11011

3)十六进制(Hexadecimal)

• 基数:16 • 符号:0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F • 计算规律:逢十六进一或借一当十六 • 二进制的多项式表示: • N16=dn-1 ×16n-1 + dn-2 ×16n-2 + • • • • • •d1 ×161 + d0 ×160 + d-1 ×16-1 + d-2 ×16-2 + • • • • • •d-m ×16-m • 其中n为整数位数;m为小数位数。Di表示第i 位的系数,16i称为该位的权.

若二进制原码小数的位数分别是8、16 位,求其该数表示的最大值、最小值及所能 表示数的个数?

计算机组成与结构第四版(王爱英著)清华大学出版社课后答案(全)

计算机的算术运算

单精度浮点数

1000 1111 1110 1111 1100 0000 0000 0000 S E F S =(-1)1=-1 E =00011111=3110 F’ =110+(110 1111 1100 0000 0000 0000)2

单精度浮点数=S×F’×2E

WANG Wei, Computer Organization and Architecture, Copyright 2004 TJU

若它分别表示如下所示的三种数,那么他们 的含义各是什么?

2的补码表示的整数 无符号整数 单精度浮点数

WANG Wei, Computer Organization and Architecture, Copyright 2004 TJU

计算机的算术运算

分析与解答:

2的补码表示的整数

(1000 1111 1110 1111 1100 0000 0000 0000)补 =(1111 0000 0001 0000 0100 0000 0000 0000)原 =-(111 0000 0001 0000 0100 0000 0000 0000) =-188011315210

WANG Wei, Computer Organization and Architecture, Copyright 2004 TJU

计算机的逻辑部件

+6

WANG Wei, Computer Organization and Architecture, Copyright 2004 TJU

计算机的逻辑部件

0100 0001 0010 1000 0000 0000 0000 0000

WANG Wei, Computer Organization and Architecture, Copyright 2004 TJU

计算机组成与结构经典例题(王爱英

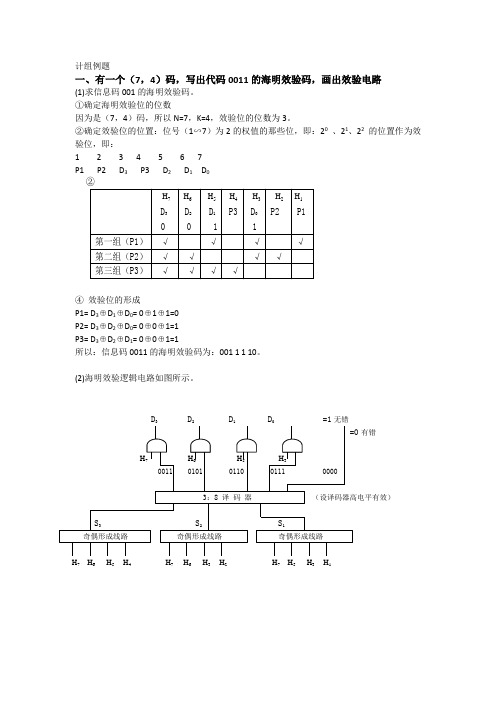

计组例题一、有一个(7,4)码,写出代码0011的海明效验码,画出效验电路(1)求信息码001的海明效验码。

①确定海明效验位的位数因为是(7,4)码,所以N=7,K=4,效验位的位数为3。

②确定效验位的位置:位号(1∽7)为2的权值的那些位,即:20 、21、22 的位置作为效验位,即:1 2 3 4 5 6 7 P1 P2 D 3 P3 D 2 D 1 D 0④ 效验位的形成P1= D 3⊕D 1⊕D 0= 0⊕1⊕1=0 P2= D 3⊕D 2⊕D 0= 0⊕0⊕1=1 P3= D 3⊕D 2⊕D 1= 0⊕0⊕1=1所以:信息码0011的海明效验码为:001 1 1 10。

(2)海明效验逻辑电路如图所示。

②H 7 H 6 H 5 H 4 H 3 H 2 H 1 D 3 D 2 D 1 P3 D 0 P2 P1 0 0 1 1 第一组(P1) √ √ √ √ 第二组(P2) √ √ √ √ 第三组(P3) √ √ √ √3 2 1 0无错 有错H7 H 6 H 5 H 4 H 7 H 6 H 3 H 2 H 7 H 5 H 3 H 1二、求有效信息1010、0111的CRC 校验码,并求循环余数,说明校验原理,画出译码与纠错电路。

(1)求有效信息1010的CRC 校验码①确定校验位的位数设R 为校验位的位数,则整个码字的位数应满足不等式:N=K +R ≤2R -1 设R=3,则23-1=7,N=4+3=7,不等式满足。

所以R 最小取3。

②选一个R +1位的生成多项式G(x),如G(x)=1011③在有效信息后面添R 个0。

然后用它和G(x)进行模2除法运算,所得的余数即为所求的校验位。

运算过程如下: 1001 1011 1010000 1011 1000 1011 11 余数为011,所以,所求的CRC 校验码为:1010011(2) 求循环余数:在上面11余数的基础上添0继续进行模2除, 如下:第一个余数110第二个余数1100 余数循环次序如下:1011 111 第三个余数 011 1110 1011 101 第四个余数 1010 1011 1 第五个余数 10 第六个余数 100 第七个余数 1000 1011 11 第一个余数(3)校验原理G (x)=1011时的1010(7,4)循环码的出错模式(4)译码与纠错电路校验的原理是根据余数来判断出错位,取反即可纠错, 译码与纠错电路如下。

计算机组成原理复习资料

12

32位单精度浮点数

IEEE 754标准

E:含阶符的阶码,8 位

阶码采用移码方式来表示 正负指数

S:1位符号位

0表示正数 1表示负数

M:尾数,23位小

数表示,小数点放 在尾数域最前面

IEEE 754标准

64位双精度浮点数

E:含阶符的阶码,11位

S:1位符号位 M:尾数,52位小数

规格化表示原则

④ X=(-1)s×1.M×2e =+(1.011011)×23 =+1011.011=(11.375)10

例2:真值20.59375,求32位单精度浮点数

① 分别将整数和分数部分转换成二进制数 20.59375=10100.10011 ② 移动小数点,使其在第1、2位之间 10100.10011=1.010010011×24 e=4 E=4+127=131=10000011 S=0 M=010010011 ③ 得到32位浮点数的二进制存储格式为: 0 100 0001 1010 0100 1100 0000 0000 0000 =(41A4C000)16

3

计算机系统组成(硬件部分)

计算机系统由硬件部分和软件部分组成。 按照传统划分,硬件部分主要由运算器、控制器、存储 器、输入部分和输出部分组成;软件部分则由系统软件 和应用软件两部分组成。 现代计算机中将运算器和控制器集成在一块芯片上,称 为中央处理器(CPU),因此,通常认为现代计算机硬 件部分由CPU、存储器和输入输出系统构成。

本章要点:

• Von Neumann型计算机的基本原理(存储程 序控制)和特点(按地址访问并顺序执行指令 、二进制运算……)和组成框图(以运算器为 中心演变成以存储器为中心)图的变迁 • 个人电脑(Personal Computer) • 普及运算(Pervasive Computing) • 计算机性能指标:处理机字长、速度(吞吐量 、响应时间、主频、时钟周期、存取周期、 CPU执行时间、每条指令周期数CPI、单位时 间内的执行指令(MIPS、MFLOPS))、存 储器容量以及带宽(存储器带宽、总线带宽等 )

计算机组成原理白中英本科生试题库附答案

计算机组成原理白中英—、选择题 1从器件角度看,计算机经历了五代变化。

但从系统结构看,至今绝大多数计算机仍属于(B)计算机 A 并行 B 冯•诺依曼 C 智能 D 串行 2某机字长32位,其中1位表示符号位。

若用定点整数表示,则最小负整数为(A) o A _(231_1) 3以下有关运算器的描述, A 只做加法运算 4 EEPR0M 是指(D ) A 读写存储器 B -理-1) (C )是正确的。

B 只做算术运算 B 只读存储器 (B )两级存储器组成, B 主存-辅存 5常用的虚拟存储系统由A cache-主存 6 RISC 访内指令中,操作数的物理位置一般安排在 A 栈顶和次栈顶 两个主存单元 -(231+1) -(230+1) 算术运算与逻辑运算 D 只做逻辑运算 电擦除可编程只i 器 其中辅存是大容量的磁表面存储器。

C (D )C 闪速存储器 cache-辅存 —个主存单元和一个 通用寄存器 通用寄存器-cacl: 两个通用寄存器7当前的CPU 由(B A 控制器 )组成。

B 控制器、运算器、 cache 8流水CPU 是由一系列叫做“段”的处理部件组成。

运算器、主存控制器、ALU 、主和具备m 个并行部件的CPU 相比,一个m 段流水C吞吐能力是(A ) o A 具备同等水平9在集中式总线仲裁中,A 独立请求B 不具备同等水平 (A )方式响应时间最快。

B 计数器定时查询 小于前者 菊花链大于前者 分布式仲裁 10 CPU 中跟踪指令后继地址的寄存器是(C ) O A 地址寄存器 B 指令计数器C 11从信息流的传输速度来看,(A )系统工作效率最低。

A 单总线B 双总线C 12单级中断系统中,CPU-旦响应中断,立即关闭(C ) 源产生另一次中断进行干扰。

A 中断允许 B 中断请求 13下面操作中应该由特权指令完成的是(B ) o A 设置定时器的初值 B 从用户模式切换到管 C 理员模式 14冯•诺依曼机工作的基本方式的特点是(B ) o A 多指令流单数据流 B 按地址访问并顺序执行指令 C 堆栈操作15在机器数(B )中,零的表示形式是唯一的。

计算机组成原理总复习串讲

另外,还需要了解相联存储器组成和相联存 器一般应用在什么场合。

第五小节:讲授的是cache存储器

Cache是一种高速缓冲存储器,是为了解决CPU和 主存之间的速度不匹配采用的一种重要的硬件技 术。了解主存与cache的地址映射方式。有三种 映射方式全相联映射方式直接映射方式组 相联映射方式,其中组相联方式是前二者的折中 方案。

微命令: 对应某个微操作的命令称为微命令,它 是执行单元可以接受的控制信号序列的最小单位。

微指令: 是对指令的分解,是一组微命令的组合。

主要包含两个字段:操作控制字段、顺序控制字段。

微程序: 微指令的有序集合称为微程序。一条机器指令的功能通

过许多条微指令来实现,即一条机器指令对应一段微程 序。 控制存储器:

储器、光存储器等

按存取方式分:随机存储器,顺序存储器

按在计算机中的作用分:主存储器,辅助存储器, 高速缓冲存储器,控制存储器

还有按读写功能分,按信息的可保存性分等分类 方法。

2,要掌握存储器的分级结构 分级结构主要是高速缓冲存储器—主存储器—— 外存储器三层结构

3,了解主存储器的性能指标

主要包括存储容量、存取时间、存储周期、存储器 带宽几个方面。

ROM它只能读出,不能写入,故称只读存储器。 最大的优点是具有不易失性,即使电源切断, ROM的信息也不会丢失。根据编程方法不同,我 们通常分成三类:掩模式只读存储器、一次编程 只读存储器、多次编程只读存储器。

2、闪速存储器的优点,工作原理、和CPU连接等

第四节讲述的高速存储器

高速存储器包括双端口存储器、多模块交叉 存储器、相联存储器、

计算机组成原理期末复习资料-王爱英

第1、 2 章1:简述冯诺依曼机的特点?答: (1)计算机由运算器、存储器、控制器和输入设备、输出设备五大部件组成;(2) 采用存储程序的方式,程序和数据放在同一个存储器中,指令和数据一样可以送到运算器运算,即由指令组成的程序是可以修改的;(3) 指令和数据均用二进制码表示;(4) 指令由操作码和地址码组成;(5) 指令在存储器内按顺序存放。

由指令计数器(PC指明要执行的指令所在单元地址,一般按顺序递增,但可按运算结果或外界条件而改变;(6) 机器以运算器为中心,输入输出设备与存储器的数据通过运算器。

2:触发器触发方式种类?答: ( 1)电平触发器[D]; (2)边沿触发器[D]; (3)主-从触发器[JK] 。

3: 阵列逻辑电路?答:(1 )读/写存储器RAM;⑵只读存储器R0M;(3)可编程逻辑阵列PAL-熔丝;(4)通用阵列逻辑GAL-电擦除;(5)门阵列GA;( 6)宏单元阵列MA;( 7)可编程门阵列PGA;4:PAL和GAL区别?(1) PAL采的采用的是熔丝工艺,一旦编程后就不能改写,而GAL采用电擦除的CMOS(E*ECMS) 工艺,可擦除重写100 次以上,数据可保存20 年以上,在数秒钟内即可完成擦除和编程过程。

(2) PAL器件的应用局限性较大,对于不同的输出结构,需选用不同型号的PAL器件,而GAL的输出结构有一个输出逻辑宏单元OLMC通过对它的编程,使GAl有多种输出方式:寄存器型输出、组合逻辑输出,并可控制三态输出门,因此显得很灵活。

5: 单元阵列由哪几个部分组成?答: 标准单元、通道区、I/O 单元、压焊点。

第 4 章主存储器1: 主存储器类型?答:(1)随机存储器又叫读写存储器RAM易失性存储器];非……(2)只读存储器ROM;(3)可编程只读存储器PROM;(4)可擦出可编程只读存储器EPROM;(5)可用电擦除的可编程只读存储器E*EPROM;2: 主存储器主要性能指标?答: 主存储容量、存储器存取时间和存储周期时间。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第1、2章1:简述冯诺依曼机的特点?答:(1)计算机由运算器、存储器、控制器和输入设备、输出设备五大部件组成;(2)采用存储程序的方式,程序和数据放在同一个存储器中,指令和数据一样可以送到运算器运算,即由指令组成的程序是可以修改的;(3)指令和数据均用二进制码表示;(4)指令由操作码和地址码组成;(5)指令在存储器内按顺序存放。

由指令计数器(PC)指明要执行的指令所在单元地址,一般按顺序递增,但可按运算结果或外界条件而改变;(6)机器以运算器为中心,输入输出设备与存储器的数据通过运算器。

2:触发器触发方式种类?答:(1)电平触发器[D];(2)边沿触发器[D];(3)主-从触发器[JK]。

3:阵列逻辑电路?答:(1)读/写存储器RAM;(2)只读存储器ROM;(3)可编程逻辑阵列PAL-熔丝;(4)通用阵列逻辑GAL-电擦除;(5)门阵列GA;(6)宏单元阵列MA;(7)可编程门阵列PGA;4:PAL和GAL区别?(1)PAL采的采用的是熔丝工艺,一旦编程后就不能改写,而GAL采用电擦除的CMOS(E*ECMS)工艺,可擦除重写100次以上,数据可保存20年以上,在数秒钟内即可完成擦除和编程过程。

(2)PAL器件的应用局限性较大,对于不同的输出结构,需选用不同型号的PAL器件,而GAL的输出结构有一个输出逻辑宏单元OLMC,通过对它的编程,使GAl有多种输出方式:寄存器型输出、组合逻辑输出,并可控制三态输出门,因此显得很灵活。

5:单元阵列由哪几个部分组成?答:标准单元、通道区、I/O单元、压焊点。

第4章主存储器1:主存储器类型?答:(1)随机存储器又叫读写存储器RAM[易失性存储器];非……(2)只读存储器ROM;(3)可编程只读存储器PROM;(4)可擦出可编程只读存储器EPROM;(5)可用电擦除的可编程只读存储器E*EPROM;2:主存储器主要性能指标?答:主存储容量、存储器存取时间和存储周期时间。

3:读写存储器分为?答:静态存储器SRAM和动态存储器DRAM;DRAM以“读出”方式再生或刷新,周期小于等于2ms。

DRAM分为三管存储单元电路和单管存储单元电路。

单管的优点:线路简单,单元占用面积小,速度快。

缺点:是破坏性的,读出后要立即对单元进行“重写”,已恢复原信息;单元独处信号很小,要求有高灵敏度的独处放大器。

SRAM和DRAM比较:DRAM优点:(1)集成度高-单管存储,(2)封装尺寸小-地址分批进入,管脚少;(3)价格便宜;(4)功率小。

缺点:(1)速度慢-用了动态原件;(2)需要再生。

第5章指令系统1:一条指令包含哪些信息?答:操作码、操作数地址、操作结果的存储地址、下一条指令的地址。

2:15条三地址指令操作码由0000~1110给出;15条而地址指令由11110000~11111110给出;15条以地址指令由111111110000~111111111110给出;16条零地址指令由1111111111110000~1111111111111111给出。

3:霍夫曼编码-依据指令出现概率;字长决定运算精度和寻址能力。

寻址能力可通过加长机器字长和地址扩展技术。

指令的长度主要取决于:操作码的长度、操作数的地址长度和操作数地址的个数。

短格式指令和长格式指令。

4:8种寻址方式?答:(1)直接寻址-->MOV AX,[3000H];特点:只访问一次存储器,地址位数决定了寻址范围,操作数的地址不易改变。

(2)寄存器寻址:MOV SS,AX;不访存,AX是通用寄存器,可以缩短指令长度,节省存储空间,提高指令执行速度。

(3)带位移量的基址寻址-->EA=(BR)+A;BR为基址寄存器(通用寄存器),A为位移量disp;特点:解决了程序在存储器中的定位和扩大寻址空间的问题,对多道程序和浮动程序很有用。

(4)变址寻址-->EA=(IX)+A;IX为変址寄存器,由用户给定,可作为偏移量,A不变,可作为基地址。

如果还有基址寄存器,计算有效地址时还要加上。

特点:可扩大寻址范围,変址由用户给定;便于处理数组问题。

(5)间接寻址-->EA=(A);分为寄存器间接和存储器间接寻址。

(A)是操作数的地址或指令的地址。

特点:多次访存,可扩大寻址范围,便于変址程序。

(6)相对寻址-->EA=(PC)+A;当前指令地址+偏移量A;特点:转移地址不固定,随PC变化,总是相差一个disp,对于浮动程序适用。

disp可正可负,通常用补码。

(7)立即数寻址-->特点:指令执行阶段不访存,提高了执行速度,只能适用于操作数固定情况下。

(8)堆栈寻址5:指令的分类与功能?答:(1)算术逻辑运算指令这类指令包括逻辑加、逻辑乘、按位加、逻辑移位等指令,主要用于无符号数的位操作、代码的转换、判断及运算。

移位指令用来对寄存器的内容实现左移、右移或循环移位。

(2)移位操作指令(算术、逻辑和循环移位)算术右移时最高位(符号位)不变,逻辑右移最高位补零。

(3)浮点运算指令(4)十进制运算指令(5)字符串处理指令——字符串的传送、比较、查询、转换等。

(6)数据传送指令数据传送指令主要包括取数指令、存数指令、传送指令、成组传送指令、字节交换指令、清累加器指令、堆栈操作指令等等。

这类指令主要用来实现主存和寄存器之间,或寄存器和寄存器之间的数据传送。

(7)转移类指令——a、无条件转移jump和条件转移指令branch;b、调用指令和返回指令call和return;c、陷阱与陷阱指令——意外中断。

(8)堆栈及堆栈操作指令——PUSH OPR:先(SP)-1->SP后OPR->(SP);在中断、子程序调用中广泛用于保存返回地址,状态标志及现场信息。

不同语言子程序调用时参数的传递,用堆栈普遍。

(9)输入输出(I/O)指令——输入输出指令主要用来启动外围设备,检查测试外围设备的工作状态,并实现外部备和CPU之间,或外围设备与外围设备之间的信息传送。

(10)特权指令——特权指令是指具有特殊权限的指令。

这类指令只用于操作系统或其他系统软件,一般不直接提供给用户使用。

在多用户、多任务的计算机系统中特权指令必不可少。

它主要用于系统资源的分配和管理。

(11)其他指令——除以上各类指令外,还有状态寄存器置位、复位指令、测试指令、暂停指令,空操作指令,以及其他一些系统控制用的特殊指令。

6:CISC指令的主要特点?答:(1)指令系统复杂庞大,指令数目一般多达两三百条;(2)指令长度不固定,指令格式多;(3)可以访存指令不受限制;(4)各种指令使用频率相差很大;(5)各种指令执行时间相差很大,大多数指令需多个时钟周期才能完成;(6)控制器大多数采用微程序控制;(7)难以用优化编译生成高效的目标代码程序。

7:SISC指令特点?答:(1)选取适用频率较高的一些简单指令,复杂指令的功能由简单指令的组合来实现;(2)指令长度固定,指令格式种类少;(3)只有Load/Store指令访存,其余指令的操作数在寄存器之间进行;(4)CPU中有多个通用寄存器;(5)控制器采用组合逻辑控制;(6)采用流水技术,大部分指令在一个时钟周期内完成;(7)采用优化的编译程序。

8:CISC和SISC比较?答:(1)SISC更能充分利用VLSI芯片的面积;(2)SISC更能提高运算速度;(3)SISC便于设计,可降低成本;(4)SISC有利于编译程序代码优化;(5)SISC不易实现指令系统兼容。

第6章中央处理器1:Intel80386微机系统组成?答:(1)80386微机处理器;(2)80384时钟发生器;reset:0FFFFFFF0H(3)80387协处理器;(4)总线控制逻辑;(5)存储器与输入输出系统;(6)DMA控制器及中断控制器;DMA控制I/O设备和与主存直接传送信息逻辑电路;中断控制器用于传送一个数据或发生故障时进行处理。

(7)"ready"逻辑电路。

由主存向80386发出。

2:Intel80386结构?答:指令部件、执行部件和存储管理。

指令部件:完成取指及指令译码功能,并发出控制信号;执行部件:包括ALU、乘法部件和寄存器组等;存储管理:用来确定存储地址。

(1)D0~D31:双向32位数据总线;(2)A2~A31地址线和“字节使能”信号BE0#~BE3#,#表低电位有效。

(3)CLK2:40MHz时钟;(4)RESET:总清或复位信号;(5)总线定义周期信号:W/R#写/读周期,D/C#数据/控制周期,M/IO#访问主存储器/IO设备,LOCK#总线锁定信号(0);(5)总线控制信号:ADS#地址状态信号(0),NA#主存或IO送80386信号,指令重叠,BS16#兼容16位主存信号或IO,READY#;(7)HOLD和HLDA总线仲裁信号。

主设备发出占用总线请求(HOLD),处理机释放总线后发出应答信号HLDA,放弃总线控制权。

此时HLDA是80386唯一送到引出端上的信号。

(8)中断INTR和NMI:为中断请求信号和不可屏蔽中断请求信号。

(9)协处理器接口信号:PEREQ请求信号,BUSY#忙信号,ERROR#出错信号。

3:控制器概括作用和功能及组成?答;作用:发出满足一定时序关系的控制信号,实现指令系统规定的各条指令的功能,并保证计算机系统正常运行。

功能:(1)取指令;(2)分析指令;(3)执行指令;(4)控制程序和数据的输入与结果输出;(5)对异常情况和某些请求的处理。

组成:(1)程序计数器PC;(2)指令寄存器IR;(3)指令译码器或操作码译码器;(4)脉冲源及启停线路;(5)时序控制信号形成部件。

补:程序状态字PAW和程序状态控制器PSR。

4:加法指令执行过程。

操作码-rs,rd-rsl-imm/disp答:(1)取指微指令1)指令地址送地址总线:PC->AB2)发访存控制命令:ADS,W/R非=0,M/IO非=13)指令送指令寄存器:DB->IR4)程序寄存器加1:PC+1;(2)计算有效地址微指令1)取两个源操作数:rsl->GR,(rsl)->ALU,disp->ALU2)加法运算:"+"3)地址送寄存器:ALU->AR;(3)取数微指令1)数据地址送地址总线:AR->AB2)发访存控制命令:ADS,W/R非=0,M/IO非3)数据送数据寄存器:DB->DR;(4)加法运算和送结果微指令1)两源操作数送ALU:rs->GR,(rs)->ALU,DR->ALU2)加法运算:“+”3)送结果:ALU->GR(rd->GR,ALU->rd),置状态位N,Z,V,C。