跨导运算放大器设计实例n

跨导运算放大器设计实例

李福乐 lifule@

1

Specifications

• CSMC 0.6um DPDM CMOS Process • GBW > 100MHz, PM > 60 when CL=2pF • DC Gain > 80dB • Output swing > 4V (differential) • Full differential architecture • Low Power (Large FOM)

所设计的OTA要应用于课程设计10bit cyclic ADC中。 在开关电容ADC中,ADC的速度取决于级电路的建立速度,而级电路的建立过程 可视为由大信号压摆区和小信号线性建立区构成,其中,小信号建立区的时间通 常要占到总建立时间的80%~90%,因此,OTA的大信号压摆率对ADC的速度影响 较小; 从另一个方面来说,压摆率只取决于偏置电Байду номын сангаас,当偏置电流和电容确定后,无论 输入管的VGS-VT是大是小,压摆率都不变。对于连续信号处理电路,我们希望 OTA在整个设计带宽内工作时,输出信号不会因为摆率跟不上而幅度受限,这个 时候需要SR/GBW大一些,即输入管的VGS-VT大一些;但是,对于采样信号处理 电路,比如我们所要设计的ADC,当我们确定好偏置电流,然后降低输入管的 VGS-VT,这个时候,SR不变,GBW变大,即SR/GBW变小了,而最终的建立时 间反而缩小了,ADC的速度加快了。 因此,SPEC中没有提出对SR的具体要求。 注意:不同应用对SR/GBW的不同要求!

3

MOST parameters

• u? Cox?

– Find out un, up, toxn and toxp from model library

(完整word版)跨导运算放大器的设计

跨导运算放大器的设计一、实验任务1-1 实验目的学会使用数模混合集成电路设计仿真软件Hspice ;学会按要求对电路的参数进行调整;学会对工艺库进行参数提取;学会用提取的参数进行手工计算分析并与仿真得出的参数进行比较。

通过上述实践达到对之前所学《模拟集成电路原理与设计》理论课程内容的更深入的理解和掌握,以及初步掌握模拟集成电路设计的方法和步骤,使学生能较快适应未来模拟集成电路设计的需求。

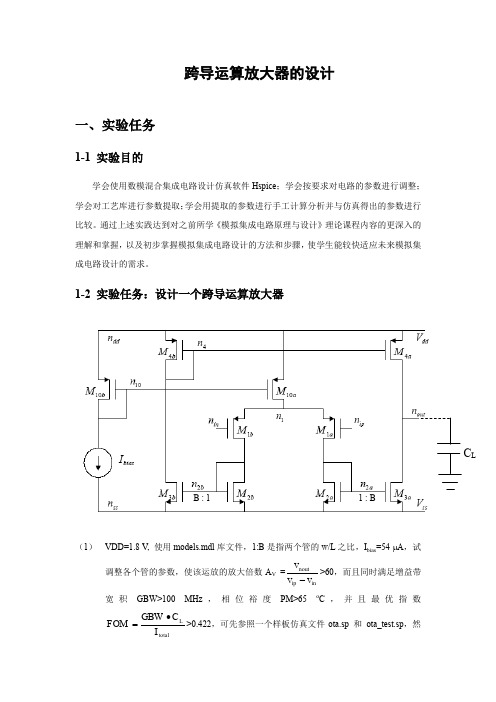

1-2 实验任务:设计一个跨导运算放大器(1) VDD=1.8 V , 使用models.mdl 库文件,1:B 是指两个管的w/L 之比,I bias =54 μA ,试调整各个管的参数,使该运放的放大倍数A V =inip noutv v v ->60,而且同时满足增益带宽积GBW>100 MHz ,相位裕度PM>65 oC ,并且最优指数totalLI C GBW FOM ∙=>0.422,可先参照一个样板仿真文件ota.sp 和 ota_test.sp,然C LB : 1 1 : B后自己调整;(2) 仿真各指标满足要求后,自行设计参数提取电路进行电路中的各个部分晶体管的参数提取,然后进行手算分析。

将分析结果与实际仿真结果进行比较; (3) 尽你所能调整除 VDD 之外的其他参数,包括I bias 来提高FOM ,最高能提高到多少? 最后提交一个word 电子文档,包括参数提取过程、手算分析过程、电路图(带管子参数)、仿真波形图、及相关详尽的说明。

二、实验内容2-1 问题12-1-1参数分析•增益Av由out m V BR g A 10=,m g = 34||out o o R r r = ,333,EN o d V L r I =444EP o d V Lr I =B= (W 3/L 3)/(W 2/L 2)则43432233111//)/(2d d PN EN d ox out m v I I L L V V L W L W I L W uC BR g A ⨯⨯==所以,可通过增大M1的宽长比,增大L4的大小,以及提高M3和M2的沟道宽长比之比B 来提高放大增益V A 。

共栅运算跨导放大器

折叠式共源-共栅运算跨导放大器姓名:刘淑杰学号:U200714149班级:2007级2班院系:控制系专业:测控技术与仪器同组人姓名:黄大龙葛金炬目录1设计目标 02相关背景知识 (1)(1)课题背景 (1)(2)题目理解 (1)3设计过程 (2)3.1 电路结构设计 (2)3.2 主要电路参数的手工推导 (2)3.3计算DC 增益 (3)3.4计算GBW (5)3.5实际计算 (7)3.6参数验证 (9)4 电路仿真 (10)4.1 用于仿真的电路图 (10)4.2 仿真网表 (10)4.3 仿真波形 (12)5 讨论 (14)收获和建议 (15)参考文献 (17)1设计目标设计一款折叠式共源-共栅跨导运算放大器(Design a Folded Cascode OTA),其设计指标见下表,参考电路原理图如下图所示,用0.35um coms工艺。

Cload DC Gain GBW Vdd Idd3pF 40dB~50dB 300MHz 3V Don’t Care图:折叠式共源-共栅跨导运算放大器设计步骤与要点:1.直流工作点的分析与设计(DC operation point design and analysis)1) 假设所有的MOS管均工作在饱和区,VGS-VT=200mV,VDD=3V,VSS= 0V,计算OTA的最大输出摆幅。

2) 基于0.35 um CMOS工艺,计算和设计MOS管的尺寸,使OTA电路满足最大输出摆幅的要求。

3) 以下数据可供设计参考L1,2,3,4 = Lmin; Lmin= 1μm。

2.在HSpice电路仿真软件,对所设计的电路进行模拟仿真与设计2相关背景知识(1)课题背景共源共栅级的普及有两个主要原因。

第一个主要原因是它们由于大输入阻抗,对单级有相当大的增益。

为了得到这个高增益,与输出节点相连的镜像电流源可以用高质量共源共栅镜像电流源实现。

通常,得到这个高增益不会导致任何速度降低,而且有时还会提高速度。

(完整word版)跨导运算放大器的设计

跨导运算放大器的设计一、实验任务1-1 实验目的学会使用数模混合集成电路设计仿真软件Hspice ;学会按要求对电路的参数进行调整;学会对工艺库进行参数提取;学会用提取的参数进行手工计算分析并与仿真得出的参数进行比较。

通过上述实践达到对之前所学《模拟集成电路原理与设计》理论课程内容的更深入的理解和掌握,以及初步掌握模拟集成电路设计的方法和步骤,使学生能较快适应未来模拟集成电路设计的需求。

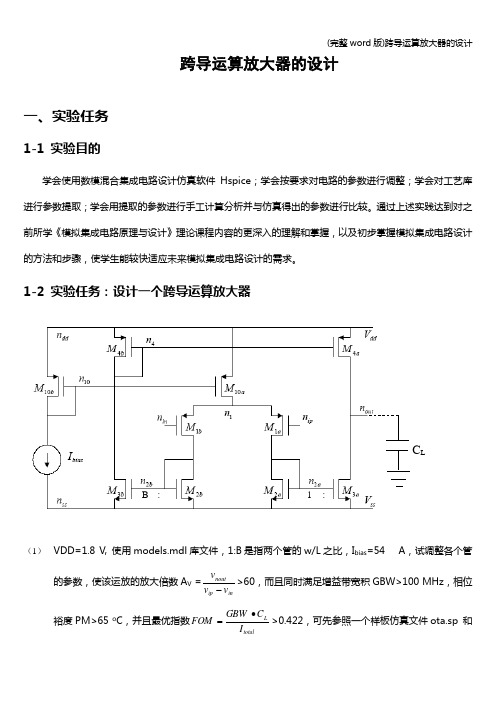

1-2 实验任务:设计一个跨导运算放大器(1) VDD=1.8 V, 使用models.mdl 库文件,1:B 是指两个管的w/L 之比,I bias =54A ,试调整各个管的参数,使该运放的放大倍数A V =inip noutv v v ->60,而且同时满足增益带宽积GBW>100 MHz ,相位裕度PM>65 o C ,并且最优指数totalLI C GBW FOM •=>0.422,可先参照一个样板仿真文件ota.sp 和C LB : 1 1 : Bota_test.sp ,然后自己调整;(2) 仿真各指标满足要求后,自行设计参数提取电路进行电路中的各个部分晶体管的参数提取,然后进行手算分析。

将分析结果与实际仿真结果进行比较;(3) 尽你所能调整除 VDD 之外的其他参数,包括I bias 来提高FOM ,最高能提高到多少?最后提交一个word 电子文档,包括参数提取过程、手算分析过程、电路图(带管子参数)、仿真波形图、及相关详尽的说明。

二、实验内容2-1 问题12-1-1参数分析•增益Av由out m V BR g A 10=,m g = 34||out o o R r r = ,333,EN o d V L r I =444EP o d V Lr I =B= (W 3/L 3)/(W 2/L 2)则43432233111//)/(2d d PN EN d ox out m v I I L L V V L W L W I L W uC BR g A ⨯⨯==所以,可通过增大M1的宽长比,增大L4的大小,以及提高M3和M2的沟道宽长比之比B 来提高放大增益V A 。

运算放大器设计实例

电压

20 年第 2 09 期电子制作

6 3

⑤ 信 号源 内阻太高。 在反相放大器的放大倍数

计算中, I R 要加上信号源 内阻。为了使 R 远远大于

信号源 内阻 ,使 K=R . 立 , R 要成 比例增 成 R、 .

加 , 旦 R> 0 一 。1 MQ, 运放 的输 入 电 流不 可 忽 略 。 想 理

模范 围受跟随器

线性区限制 。 不

能 保 证 输 入 偏 置

O~5 的范 围 。 V

圈豳

6 电子制作 20 年 第 2 4 O9 期

的原 因, 限制了输 出电流 。 显然一般 的运放驱动几十 毫安的 电流是 困难的。 同样 , R 等取值 在 1 Q R。 k

以下 , 影响 实 际放 大倍 数 。

w依 输 出 然 是 U = 2

j

K , U1 K=1 V 。 嗍 不

A

仅 是 直 流 ,也 可 以是 交流信号 , 如 5H 例 Oz

化运放 的“ 断” 虚短 ” 虚 “ 假设认 为运放的输入 电流 为 零。L 2 M3 4实际输入电流 为零点几微安 。 用 MO ( S 型输 入的运放输入电流可以小几百倍 ) 虚断” “ 假设 不能成立。同相放 大器或跟随器 的 l N+输入端直接 性曲线的水平部分 .就是放大器输出饱和到固定 电 平。 输入幅度再增加 。 出幅度不变。对 5 输 V情况下 。 输出幅度在 1 ~ V 。 35 。有一种“ aI a 中文翻 5 R l0R t 译为“ 轨至轨” 运放 , 出幅度几乎与电源相齐 。对 输 接信号源 .运放 的输入电流在信号源高内阻上形成 压降 , 实际放大倍数减小。 另外高阻输入电路容易受

运 算 放 大 器设 计 实例

跨导放大器设计实例

模拟集成电路实验——跨导放大器设计实验报告学院:电信学院班级:微电子23班姓名:游晓东学号:2120503069一、设计指标二、电路结构确定电路结构的原因: ① 根据设计指标② 电路结构对称,匹配度高,,Offset CMRR 性能指标好③ 电路稳定性好,只有一个主极点④ 该电路为差分输入,单端输出,共模抑制比大,输出共模点较稳定三、电路原理概述该电路主要由三部分组成:带隙基准电流源、偏置电路、跨导放大器9~21M M 构成一个跨导放大器,其中13M 为尾电流源,向输入的差动对管提供电流偏置。

11,12M M 为输入差分对管,将小信号电压转换成小信号电流。

9,14M M 和10,17M M 为两个对称的电流镜,比例复制小信号电流。

14,15M M 与16,17M M 为共源共栅结构,可以提高输出阻抗和开环增益。

18,19,20,21M M M M 为低压共源共栅电流镜,可以作为单端输出并且提高输出摆幅。

0~8M M 构成偏置电路部分,为跨导放大器提供偏置电流。

22~34,0~2,0~2M M Q Q R R 构成带隙基准电流源部分,为电路提供基准电流源。

四、设计过程1. 分配电流根据静态电流250A μ限制,分配带隙基准电流源部分20A μ,偏置电路部分10A μ(其中每一路2A μ),跨导放大器部分210A μ。

分配14,17M M 的偏置电流14M I 时主要考虑三个指标:,,GBW SR GMGM 要求900~1100/A V μ,因此GM 取1000/A V μ。

由于11GM B gm =⋅,B为14,9M M 的偏置电流之比,因此111000/B gm A V μ⋅= (1)GBW 要求大于3MHZ 。

112LB gm GBWC π⋅=⋅,因此11566/B gm A V μ⋅> (2)SR 要求大于3/V S μ。

92M LB I SRC ⋅=,因此9290M B I A μ⋅> (3)由于9112M ODI gm V =,若OD V 取0.2V ,则由(1)得9100M B I A μ⋅=,由(2)得956.6M B I A μ⋅>,由(3)得945M B I A μ⋅>。

折叠式共源-共栅运算跨导放大器的设计

《IC课程设计》报告折叠式共源-共栅运算跨导放大器的设计姓名:王志伟学号:U200713959班级:0707院系:控制系专业:自动化同组人姓名:田绍宇胡月目录1设计目标 (1)2相关背景知识 (2)3设计过程 (2)3.1 电路结构设计 (2)3.2 主要电路参数的手工推导 (2)3.2.1直流工作点分析 (2)3.2.2带宽分析及原件参数计算 (3)3.2.3直流增益的小信号模型分析 (4)3.3 计算参数验证 (5)4电路仿真 (5)4.1交流特性仿真 (7)4.2最大输出摆幅仿真 (9)4.3共模输出的仿真验证 (11)5讨论 (12)6收获和建议 (13)7参考文献 (14)摘要:折叠式共源共栅结构的运算放大器不仅能提高增益、增加电源电压噪声抑制比、而且在输出端允许自补偿。

1设计目标设计一款折叠式共源-共栅跨导运算放大器(Design a Folded Cascode OTA),其设计指标见表1,参考电路原理图如下图所示,用0.35um coms工艺。

图:折叠式共源-共栅跨导运算放大器设计步骤与要点:1.直流工作点的分析与设计(DC operation point design and analysis)1) 假设所有的MOS管均工作在饱和区,VGS-VT=200mV,VDD=3V,VSS= 0V,计算OTA的最大输出摆幅。

2) 基于0.35 um CMOS工艺,计算和设计MOS管的尺寸,使OTA电路满足最大输出摆幅的要求。

3) 以下数据可供设计参考L1,2,3,4 = Lmin; Lmin= 1μm。

2.在HSpice电路仿真软件,对所设计的电路进行模拟仿真与设计2相关背景知识随着集成电路技术的不断发展,高性能运算放大器得到广泛应用,其性能直接影响电路及系统的整体性能。

折叠式共源共栅运算放大器具有二阶优化性能,因此设计一个实用价值的折叠式共源共栅运算放大器是非常有现实意义的。

CMOS管的参数并不能通过简单的理论计算进行准确的预测,在给定的工艺条件下,理论计算出的管子宽长不考虑实际情况下工艺条件等诸多外界因素,仿真的结果会和设计指标有很大的差距。

第八讲 跨导运放的分析与设计讲解

由于零点的作用,相位裕度 从60多度减小至39度!

交流扫描

Ota simulation

.prot

.lib ‘LIB_PATH\csmc.lib’ tt

.unprot

.option post probe

分析miller补偿效应

.probe ac v(vo1) v(vo) vp(vo)

.op

*.dc v_vdc 2.48 2.495 0.0001

失调分析

在MOS晶体管的参数中考虑失配 例:原有的 W=12u, M=2 修改为 W=‘12u+12u*0.04u*alfa/sqrt(2*12um*5um)’ M=2 delvto=‘12.5n*alfa/sqrt(2*12um*5um)’ 这里alfa为(0,1)高斯分布变量 依次将网表的内容按照上面的方法修改

.lib ‘LIB_PATH\csmc.lib’ tt

.unprot

.option post probe

.probe dc v(vo1) v(vo)

.op .dc v_vdc 2.48 2.495 0.0001

精扫

*.trans 10ns 200ns 20ns 0.1ns

*.ac dec 10 1k 100meg $sweep rzv 0 2k 0.2k

耗,因此可查得电路功耗为2.47mW • 对于MOS管,注意各参量的含义:region、id、vgs、

vds、vth、vdsat、gm、gmb、gds……可查得流过 M_U3的偏置电流为149.8uA,并注意到M_M3的 region为Linear

直流扫描

Ota simulation

.prot

.lib ‘LIB_PATH\csmc.lib’ tt