开题报告—基于vhdl的简易计算器的设计

简易计算器开题报告

简易计算器开题报告简易计算器开题报告一、引言计算器是一种广泛应用于日常生活和工作中的工具,它能够帮助人们进行简单的数学运算。

然而,随着科技的不断进步,计算器也发生了很大的改变。

在这个数字化时代,我们可以看到各种各样的高级计算器和手机应用程序,它们提供了更多的功能和更方便的使用体验。

然而,对于一些特定的场景和需求,简易计算器仍然具有一定的优势。

本文将探讨开发一款简易计算器的可行性和必要性。

二、背景分析1. 简易计算器的定义简易计算器是一种功能简单、操作便捷的计算工具,通常只包含基本的四则运算和一些常用函数。

它的界面简洁明了,适合快速计算和简单操作。

2. 现有计算器的不足尽管现有的高级计算器和手机应用程序提供了更多的功能和更方便的使用体验,但在某些情况下,它们可能过于复杂,不适合快速计算。

例如,在一些会计、商务、教育等场景中,人们更倾向于使用简单的计算器进行基本运算,以提高工作效率。

3. 简易计算器的优势简易计算器相对于高级计算器和手机应用程序而言,具有以下优势:- 操作简单:简易计算器通常只有几个按键,界面简洁明了,使用起来非常方便。

- 快速计算:简易计算器专注于基本运算,因此在处理简单的数学运算时更加迅速。

- 便携性:简易计算器体积小巧,便于携带,随时随地使用。

三、开发目标基于上述背景分析,我们的开发目标是设计和开发一款简易计算器,以满足以下需求:1. 提供基本的四则运算功能,包括加、减、乘、除。

2. 支持一些常用函数,如开方、求平方、求倒数等。

3. 界面简洁明了,操作简单方便。

4. 提供快速计算的能力,以提高工作效率。

5. 考虑到便携性,计划将其设计为小巧的手持设备。

四、技术实现1. 硬件需求为了实现简易计算器的开发目标,需要以下硬件设备:- 微处理器:选择一款适合嵌入式系统的微处理器,例如ARM Cortex-M系列。

- 显示屏:选用一款小巧而清晰的显示屏,以方便用户查看计算结果。

- 按键:设计合适的按键布局,以支持用户输入数字和操作符。

电子信息工程基于VHDL的100进制计数器报告

目录一、设计要求--------------------------------------------------------------------------------二、设计目的--------------------------------------------------------------------------------三、设计方案--------------------------------------------------------------------------------四、设计原理---------------------------------------------------------------------------------五、硬件要求---------------------------------------------------------------------------------六、调试与问题疑点------------------------------------------------------------------------七、设计步骤----------------------------------------------------------------------------------八、体会、对设计工作的总结与展望---------------------------------------------------- 一、设计要求(1)设计带计数允许和复位输入的100进制计数器,要求完成顶层电路图和底层VHDL文件;(2)进行功能仿真;(3)下载并验证计数器功能;(4)按上述步骤设计100进制计数器;(5)为上述设计建立元件符号。

二、设计目的(1)设计一个带计数允许和复位端的100进制计数器。

VHDL设计FPGA数字系统:计算器.docx

1.3文章小结

本章介绍这几世纪以来的计算器发展,还有本次设计的研究任务,为后续的设计打下基础。

第二章项目基础

2.1软件与硬件介绍

2.1.1 EDA

电子设计自动化(英语:Electronic design automation,缩写:EDA)即电子设计自动化技术,是利用计算机工作平台,从事电子系统和电路设计的一项技术[3]。

硬件描述语言HDL (Hardware Description Language )是一种用于设计硬件电子系统的计算机语言,它用软件编程的方式来描述电子系统的逻辑功能、电路结构和连接形式,与传统的门级描述方式相比,它更适合大规模系统的设计[4]。

2.1.2 EDA的特点及发展

现在人类社会已经步入了信息时代,各种各样的信息技术在我们的生活当中发挥着越来越重要的作用。信息时代的高速发展离不开电子设计技术的发展和相关电子产品的进步,而他们的核心就是EDA技术。

This design studied Digital System is composed of added and subtracted of module to complete, including the keyboard input module, decoding module, calculate the main control module and a digital tube display module. When the keyboard input signal passes through these modules, complete data display computing requirements. This calculation control system Math four computing module is the core.

实验4计数器的VHDL设计

实验4 计数器的VHDL 设计1 .实验目的( l )掌握VHDL描述同步与异步计数器的方法。

( 2 )学习使用VHDL进行时序逻辑电路的设计。

( 3 )掌握用QuartusⅡ且进行文本输入,进行电路设计、编译和仿真。

( 4 )掌握用QuartusⅡ进行层次型电路设计的方法。

( 5 )学习利用真值表编写VHDL程序。

( 6 )学习使用RTL工具观察电路图。

2 .实验仪器设备( 1 ) PC一台。

( 2 ) QuartusⅡ开发软件一套。

( 3 ) EDA技术实验开发系统一套。

3 .实验要求( 1 )预习同步与异步计数器的相关内容。

( 2 )用VHDL方式完成计数器电路设计。

( 3 )完成计数器电路的仿真。

( 4 )下载电路到EDA实验系统验证结果。

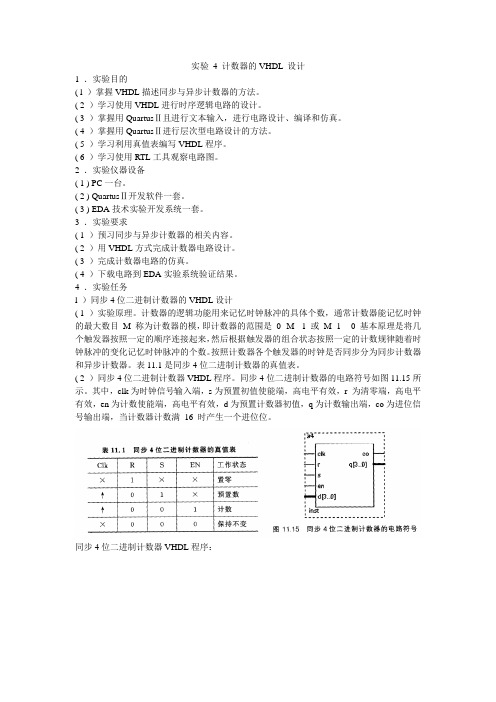

4 .实验任务l )同步4位二进制计数器的VHDL设计( 1 )实验原理。

计数器的逻辑功能用来记忆时钟脉冲的具体个数,通常计数器能记忆时钟的最大数目M 称为计数器的模,即计数器的范围是0--M - 1 或M -1 -- 0 基本原理是将几个触发器按照一定的顺序连接起来,然后根据触发器的组合状态按照一定的计数规律随着时钟脉冲的变化记忆时钟脉冲的个数。

按照计数器各个触发器的时钟是否同步分为同步计数器和异步计数器。

表11.1是同步4位二进制计数器的真值表。

( 2 )同步4位二进制计数器VHDL程序。

同步4位二进制计数器的电路符号如图11.15所示。

其中,clk为时钟信号输入端,s为预置初值使能端,高电平有效,r 为清零端,高电平有效,en为计数使能端,高电平有效,d为预置计数器初值,q为计数输出端,co为进位信号输出端,当计数器计数满16 时产生一个进位位。

同步4位二进制计数器VHDL程序:( 3 )同步4位二进制计数器的电路仿真波形图如图11.16所示。

RTL电路如图11.17所示。

根据波形图可知,该同步计数器符合设计要求。

从RTL电路中发现触发器的时钟信号是由CLK同时给定的,符合同步电路要求。

基于VHDL语言的乘法器的设计

利用VHDL設計乘法器Implement of Multiplier by Using VHDL許地申Dih-Shen Hsu中華技術學院電機系副教授Associate ProfessorDepartment of Electrical EngineeringChina Institute of Technology摘 要在計算機結構裡加,減,乘,除是常被用到的運算,本文提出以非常高速積體電路硬體描述語言(VHDL)來描述硬體,說明如何將兩個運算元作相乘的運算。

我們首先以無號數整數做乘法運算來說明其原理,設計其電路結構。

其實在VHDL 程式中,我們更可以載入STD_LOGIC_ARITH與STD_LOGIC_UNSIGNED元件盒之後,直接進行乘法運算,既簡單又容易擴充。

最後,我們將以4-bit X 4-bit 的例子來做電路描述、電路合成、電路模擬並以七段顯示器將其結果顯示出來。

關鍵字:非常高速積體電路硬體描述語言、電路描述、電路合成、電路模擬AbstractWe have known operation that perform addition, subtraction, multiplication, and division. In this paper we are presented primarily to describe hardware using by VHDL. We can explain how multiplication may be performed for two operand. Multiplication of unsigned numbers illustrates the main issues involved in the design of multiplier circuit. In fact, after the STD_LOGIC_ARITH and STD_LOGIC_UNSIGNED packages were added to the VHDL program, it became not only simple but also easy to extended. Next, consider a 4 x 4 example to circuit description, circuit synthesis, and circuit simulation by using VHDL. Finally, this approach can also be displayed by 7-segment.Keyword : VHDL , circuit description , circuit synthesis, circuit simulation壹.簡介VHDL是Very High Speed Integrated Circuit Hardware Description Language 的英文縮寫。

用VHDL实现计算器

谢谢观看!

then in3:=in1/in2; t<=in3; end if; end process p1111;

--'*'

p111:process(t) begin case t is when 0=>g<="11111100";--0 when 1=>g<="01100000";--1 when 2=>g<="11011010";--2 when 3=>g<="11110010";--3 when 4=>g<="01100110";--4 when 5=>g<="10110110";--5 when 6=>g<="10111110";--6 when 7=>g<="11100000";--7 when 8=>g<="11111110";--8 when 9=>g<="11110110";--9 when others=>t<="00000010";--错 end case; end process p111;

程序源码

--库的引用 LIBRARY IEEE; --USE IEEE.std_logic_arith.ALL; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; --use ieee.numeric_bit.all;

--实体声明 entity adder is port( d0,d1,d2,d3,d4,d5,d6,d7,d8,d9,d10,d11,d12,d13,d

(VHDL实验报告)模值12计数器、分频器的设计

电子科技大学成都学院学院指导教师模值12计数器,分频器设计二、实验目的1、了解二进制计数器的工作原理。

2、时钟在编程过程中的作用。

3、学习数控分频器的设计、分析和测试方法。

4、了解和掌握分频电路实现的方法。

5、掌握EDA技术的层次化设计方法。

三、实验原理(1)二进制计数器中应用最多、功能最全的计数器之一,含异步清零和同步使能的加法计数器的具体工作过程如下:在时钟上升沿的情况下,检测使能端是否允许计数,如果允许计数(定义使能端高电平有效)则开始计数,否则一直检测使能端信号。

在计数过程中再检测复位信号是否有效(低电平有效),当复位信号起作用时,使计数值清零,继续进行检测和计数。

其工作时序如下图所示:(2)数控分频器的功能就是当输入端给定不同的输入数据时,将对输入的时钟信号有不同的分频比,数控分频器就是用计数值可并行预置的加法计数器来设计完成的,方法是将计数溢出位与预置数加载输入信号相接得到。

(1)“模值12计数器的设计”的实验要求完成的任务是在时钟信号的作用下,通过使能端和复位信号来完成加法计数器的计数。

实验中时钟信号使用数字时钟源模块的1HZ信号,用一位拨动开关K1表示使能端信号,用复位开关S1表示复位信号,用LED模块的LED1~LED4来表示计数的二进制结果。

实验L ED 亮表示对应的位为‘1’,LED灭表示对应的位为‘0’。

通过输入不同的值模拟计数器的工作时序,观察计数的结果。

实验箱中的拨动开关、与FPGA 的接口电路,LED 灯与FPGA 的接口电路以及拨动开关、LED 与F PGA 的管脚连接在实验一中都做了详细说明,这里不在赘述。

数字时钟信号模块的电路原理如下图所示,其时钟输出与F PGA 的管脚连接表如下图所示:信号名称对应FPGA 管脚名说明DIGITAL-CLK C13 数字时钟信号送至FPGA 的C13按键开关模块的电路原理如下图所示:按键开关的输出与F PGA 的管脚连接表如下图所示:五、实验步骤(一)模值12计数器的设计1、建立工程文件1)运行QUARTUSII 软件。

基于VHDL的计数器及数码显示器

北华航天工业学院《EDA技术综合设计》课程设计报告报告题目:基于VHDL的计数器及数码显示器作者所在系部:电子工程系作者所在专业:自动化作者所在班级:B08221作者姓名:刘承东指导教师姓名:崔瑞雪完成时间:2010-11-29内容摘要计数器要求在一个数码管上可以显示十进制加法计数功能,在另一个数码管上线数十二进制加法计数功能。

并且在另两个数码管上显示十六进制可逆计数器功能,最后用两个数码管显示六十进制加法计数功能。

共用到六个数码管。

因此要完成抢答器的逻辑功能,该电路至少应包括译码模块、计数模块、数码显示。

关键词:EDA、可编程逻辑器件、计数器、显示器目录一概述 (1)二方案设计与论证 (1)三程序设计流程图 (2)四单元电路设计 (3)3.1. 数据选择器设计 (3)3.2 计数模块的设计 (4)3.3 译码器模块的设计 (10)3.4 主电路连线图 (11)四器件编程与下载 (11)五实验设备 (11)六心得体会 (11)七参考文献 (12)课程设计任务书一、概述抢答器的逻辑结构较简单,它主要由十进制加法计数模块、十二进制加法计数模块、十六进制可逆计数模块、六十进制加法计数模块与数据选择模块和译码模块组成。

在整个计数器中最关键的是如何实现各个模块的计数。

除此之外,各个计数器还需有一个使能信号和一个归零信号,以便计数器能实现计数和停止。

特别的是十进制计数器需要有一个进位。

显示时需要六个数码管。

二、方案设计与论证将该任务分成六个模块进行设计,分别为:十进制加法计数模块、十二进制加法计数模块、十六进制可逆计数模块、六十进制加法计数模块、译码模块、数据选择模。

1、计数模块:在这六个个模块中主要实现计数功能,;使能端en;抢计数器报时钟信号clk;系统复位信号rst;。

注意的是十进制计数器中需要添加一个进位信号c2、译码模块:在这个模块中主要实现计数过程中将BCD码转换成7段的功能。

3、数据选择模块在这个模块中主要实现计数过程中的数据输入功能,输入信号才c10[3..0]、c12[3..0]、c16[6..0];c60[6..0]计数输出信号sel;数据输出信号daout;计数脉冲clk,实现c10、c12、c16 、c60按脉冲轮流选通,在数码管上显示。

VHDL实现简易计算器

library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity calculator isPort(clr,clk,dent,ch,set :in std_logic;add,sub,mul,div :in std_logic;outrange,minus :out logic;led1: out std_logic_vector(6 downto 0);led2: out std_logic_vector(6 downto 0);led3: out std_logic_vector(6 downto 0);led4: out std_logic_vector(6 downto 0);end calculator;architecture Behavioral of calculator issignal sec_1_10,sec1 :std_logic;signal get,minus_sig :integer range 0 to 3;signal choose : integer range 0 to 5;signal chose : integer range 0 to 7;signal L2,LL2,LLL2,LLLL2 : integer range 0 to 10; signal L1,LL1,LLL1,LLLL1: integer range 0 to 10; signal L,LL,LLL,LLLL : integer range 0 to 10;signal nn : integer range 0 to 9999;signal bi : integer range 0 to 20000;begin分频模块process(clr,clk)variable c: integer range 0 to 10;beginif clr=‘0’ then c:=0;elsif rising_edge(clk) thenif c<10 then c:=c+1;else c:=0;end if;end if;if c>5 then sec1<=‘1’;else sec1<=‘0’;end if;end process;process(clr,clk)variable c : integer range 0 to 3200000; beginif clr=‘0’ then c:=0;elsif rising_edge(clk) thenif c<3200000 then c:=c+1;else c:=1;end if;end if;if c>1600000 then sec_1_10<=‘1’;else sec_1_10<=‘0’;end if;end process;键控模块process (sec_1_10,clr,mul,div,sub,add,set) variable cc,dd : std_logic;variable p,pp : integer range 0 to 3;variable c : integer range 0 to 5;variable m : integer range 0 to 7;variable d,e,f,g : integer range 0 to 9;variable ee : integer range 0 to 90;variable ff : integer range 0 to 900;variable gg : integer range 0 to 9000;beginif clr=‘0’ or ((mul=‘0’ or div=‘0’ or sub=‘0’ or add=‘0’)and set=‘1’ and ch=‘1’)then c:=0; d:=0; e:=0; f:=0; g:=0;ee:=0; ff:=0; gg:=0; m:=0; p:=0; cc:=0; dd:=0;pp:=0;elsif rising_edge(sec_1_10) thenif dent=‘1’ thenif m<7 then m:=m+1;else m:=7;end if;elsif set=‘0’ and add=‘0’ then dd:=‘1’;elsif dd=‘1’ thenif pp<3 then pp:=pp+1;else pp:=0;dd:=‘0’;end if;elsif div=‘0’and set=‘0’ then cc:=‘1’;elsif cc=‘1’ thenif p<3 then p:=p+1;else p:=3;cc:=‘0’;end if;elsif ch=‘0’ thenif c<5 then c:=c+1;else c:=1;end if;elsif c=2 and set=‘0’thenif d<9 then d:=d+1;else d:=0;end if;elsif c=3 and set=‘0’thenif e<9 then e:=e+1;ee:=ee+10;else e:=0;ee:=0;end if;elsif c=4 and set=‘0’thenif f<9 then f:=f+1;ff:=ff+100;else f:=0;ff:=0;end if;elsif c=5 and set=‘0’thenif g<9 then g:=g+1;gg:=gg+1000;else g:=0;gg:=0;end if;else null;end if;end if;choose<=c;L1<=d;LL1<=e; LLL1<=f; LLLLL1<=g; nn<=d+ee+ff+gg;chose<=m;get<=p;minus_sig<=pp; end process;运算及存储模块process (clr,sec1,bi)variable min mmin : std_logic;variable ad,sb,mu,dv :std_logic_vector(1 downto 0);variable c,d, f,g,m : integer range 0 to 20000;beginif clr=‘0’ then min:=‘1’; c:=0; d:=0; f:=0; g:=0;bi<=0;sb:=“00”;ad :=“00”;mu :=“00”; dv:=“00”;outrange <=‘1’;elsif rising_edge(sec1) thenif set=‘0’ and mul=‘0’then mmin:=min;if ad :=“00”and sb :=“00”and mu:=“00” and dv:=“00” then m:=nn; else m:=bi;end if;elsif set=‘0’ and div=‘0’ then bi<=m;d:=m;min:=mmin;ad:=“10”;elsif minus_sig=3 then min:=not(min);elsif sub=‘0’ and set=‘1’ then sb:=“01”;ad :=“00”;mu :=“00”; dv:=“00”;elsif add=‘0’ and set=‘1’ then ad:=“01”;sb :=“00”;mu :=“00”; dv:=“00”;elsif mul=‘0’ and set=‘1’ then mu:=“01”;ad :=“00”;sb :=“00”; dv:=“00”;f:=0;g:=0;elsif div=‘0’ and set=‘1’ then dv:=“01”;ad :=“00”;sb :=“00”; mu:=“00”;f:=0;elsif dent=‘0’ and ad=“00” and sb=“00” and mu=“00”and dv=“00”then d:=nn;bi<=nn;elsif (ad=“10” or sb=“10” or mu=“10” or dv=“10”) and dent=‘0’then d:=bi;elsif sb=“10” and dent=‘1’ then c:=nn;if min=‘1’ then sb:=“10”;if d>=c then d:=d-c;bi<=d;else min:=‘0’;bi<=c-d;end if;elsif (c+d)<10000 then sb:=“10”;bi<=(c+d); else outrange<=‘0’;bi<=0;end if;elsif ad=“01” and dent=‘1’then c:=nn;if min=‘1’then ad:=“10”;if (c+d)<10000 then d:=(c+d);bi<=d;else outrange<=‘0’;bi<=0;end if;elsif c<d then bi<=d-c;ad:=“10”;else min:=‘1’;bi<=c-d;ad:=“10”;end if;elsif mu=“01” and dent=‘1’ then c:=nn;if c=0 or d=0 then bi<=0;elsif f<c then g:=g+d;if g>9999 then bi<=0;outrange<=‘0’;else f:=f+1;end if;else bi<=g; mu:=“10”;end if;elsif dv=“01” and dent=‘1’ then c:=nn;if c=0 then bi<=0;outrange<=‘0’;elsif c=1 then bi<=d;elsif d>=c thenif f<20000 then d:=d-c;f:=f+1;else null;end if;elsif d<c/2 then bi<=f;dv:=“10”;else bi<=f+1;dv:=“10”;end if;else null;end if;end if;minus<=min;end process;process(get,sec1,clr,mul,div,sub,add,bi,set)variable cc,dd,ee :integer range 0 to 10;variable bb :integer range 0 to 20000;beginif clr=‘0’ or ((mul=‘0’ or div=‘0’ or sub=‘0’or add=‘0’) and set=‘1’ and ch=‘1’) or get=1then cc:=0; dd:=0; ee:=0; bb:=0;elsif rising_edge(sec1) thenif chose=5 or get=2 then bb:=bi;elsif bb>999 then cc:=cc+1;bb:=bb-1000;elsif bb>99 then dd:=dd+1;bb:=bb-100;elsif bb>9 then ee:=ee+1;bb:=bb-10;elsif ee=0 and dd=0 and cc=0 then L2<=bb;LL2<=10;LLL2<=10;LLLL2<=10;elsif dd=0 and cc=0 then L2<=bb;LL2<=ee;LLL2<=10;LLLL2<=10;elsif cc=0 then L2<=bb;LL2<=ee;LLL2<=dd;LLLL2<=10;else L2<=bb;LL2<=ee;LLL2<=dd;LLLL2<=cc;end if;end if;end process;译码显示电路process (get,chose,sec_1_10,L1,LL1,LLL1,LLLL1,choose,L2,LL2,LLL2,LLLL2) beginif chose=7 or get=3 then L<=L2; LL<=LL2; LLL<=LLL2; LLLL<=LLLL2;elsif sec_1_10=‘1’ then L<=L1; LL<=LL1; LLL<=LLL1; LLLL<=LLLL1;elsif chose=2 then L<=10; LL<=LL1; LLL<=LLL1; LLLL<=LLLL1;elsif chose=3 then L<=L1; LL<=10; LLL<=LLL1; LLLL<=LLLL1;elsif chose=4 then L<=L1; LL<=LL1; LLL<=10; LLLL<=LLLL1;elsif chose=5 then L<=L1; LL<=LL1; LLL<=LLL1; LLLL<=10;else L<=L1; LL<=LL1; LLL<=LLL1; LLLL<=LLLL1;end if;end process;led_1:process(L)beginif L=0 then led1<=“0000001”;elsif L=1 then led1<=“1001111”;elsif L=2 then led1<=“0010010”;elsif L=3 then led1<=“0000110”;elsif L=4 then led1<=“1001100”;elsif L=5 then led1<=“0100100”;elsif L=6 then led1<=“0100000”;elsif L=7 then led1<=“0001111”;elsif L=8 then led1<=“0000000”;elsif L=9 then led1<=“0000100”;else led1<=“1111111”;end if;end process;led_21:process(LL)beginif LL=0 then led2<=“0000001”; elsif LL=1 then led2<=“1001111”; elsif LL=2 then led2<=“0010010”; elsif LL=3 then led2<=“0000110”; elsif LL=4 then led2<=“1001100”; elsif LL=5 then led2<=“0100100”; elsif LL=6 then led2<=“0100000”; elsif LL=7 then led1<=“0001111”; elsif LL=8 then led2<=“0000000”; elsif LL=9 then led2<=“0000100”; else led2<=“1111111”;end if;end process;led_3:process(LLL)beginif LLL=0 then led3<=“0000001”; elsif LLL=1 then led3<=“1001111”; elsif LLL=2 then led3<=“0010010”; elsif LLL=3 then led3<=“0000110”; elsif LLL=4 then led3<=“1001100”; elsif LLL=5 then led3<=“0100100”; elsif LLL=6 then led3<=“0100000”; elsif LLL=7 then led3<=“0001111”; elsif LLL=8 then led3<=“0000000”; elsif LLL=9 then led3<=“0000100”; else led3<=“1111111”;end if;end process;led_4:process(LLLL)beginif LLLL=0 then led4<=“0000001”; elsif LLLL=1 then led4<=“1001111”; elsif LLLL=2 then led4<=“0010010”; elsif LLLL=3 then led4<=“0000110”; elsif LLLL=4 then led4<=“1001100”; elsif LLLL=5 then led4<=“0100100”; elsif LLLL=6 then led4<=“0100000”; elsif LLLL=7 then led4<=“0001111”; elsif LLLL=8 then led4<=“0000000”; elsif LLLL=9 then led4<=“0000100”; else led4<=“1111111”;end if;end process;end Behaviral;。

vhdl课程设计设计模为 4、8、12、16的可变计数器实验报告总结

VHDL课程设计 - 可变计数器实验报告总结

一、设计概述

本课程设计的主要目标是设计并实现一个可变计数器,其模(Modulo)值可以在4、8、12、16之间进行选择。

计数器采用VHDL编程语言进行描述,并在FPGA开发板上进行测试验证。

二、设计实现

1. 硬件平台:我们选择了Xilinx的FPGA开发板作为硬件平台,它具有丰富的I/O资源和足够的逻辑单元,可以满足我们的设计需求。

2. VHDL编程:我们采用VHDL语言进行编程,实现了模4、模8、模12和模16的可变计数器。

通过选择不同的计数模式,计数器的模值可以在4、8、12、16之间进行切换。

3. 测试与验证:为了验证计数器的功能,我们编写了测试平台,并通过仿真和实际硬件测试对计数器进行了全面的测试。

三、实验结果与分析

1. 实验结果:通过仿真和实际硬件测试,我们验证了计数器的

功能正确性。

在不同的模值下,计数器都能正确地进行计数操作,并且在达到模值后能正确地回绕到0。

2. 结果分析:实验结果表明,我们的VHDL编程和FPGA开发技能得到了很好的应用和提升。

同时,通过这次课程设计,我们更深入地理解了可变计数器的设计和实现原理,提高了我们的硬件设计能力。

四、总结与展望

本次课程设计让我们深入了解了VHDL编程语言和FPGA开发技术,提高了我们的硬件设计能力。

通过实际的设计和测试,我们成功地实现了一个可变模值的计数器,达到了课程设计的要求。

在未来的学习和工作中,我们将继续深入学习FPGA设计和VHDL编程,不断提高自己的硬件设计能力。

同时,我们也期待将这种技术应用于更多的实际项目中,为工程实践做出贡献。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

开题报告—基于vhdl的简易计算器的设计

本科毕业设计开题报告

题目:基于vhdl的简易计算器的设计

院(系):电气与信息工程学院

班级:电技09-1班

姓名:朱厚磊

学号: 08号

指导教师:杜艳秋

教师职称:讲师

黑龙江科技学院本科毕业设计开题报告

4、设计方案:

计算器的核心部件是运算器,当有数据输入时,首先将数据放在寄存器中,然后送入运算器中进行运算,最后将输出结果放入寄存器中输出。

设有操作码op,通过对操作码的选择实现加减乘除运算。

程序流程图:。