高频电路的设计及测试

《高频电子线路》实验指导书(通信技术专业适用)word资料3页

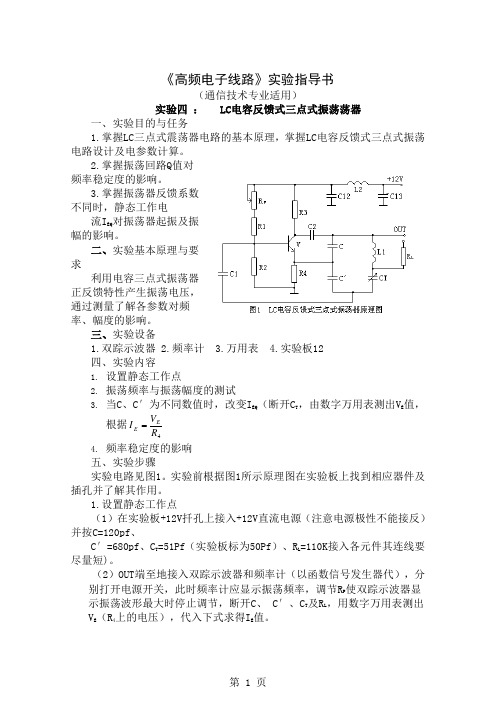

《高频电子线路》实验指导书(通信技术专业适用)实验四 : LC 电容反馈式三点式振荡荡器一、实验目的与任务1.掌握LC 三点式震荡器电路的基本原理,掌握LC 电容反馈式三点式振荡电路设计及电参数计算。

2.掌握振荡回路Q 值对频率稳定度的影响。

3.掌握振荡器反馈系数不同时,静态工作电流I EQ 对振荡器起振及振幅的影响。

二、实验基本原理与要求利用电容三点式振荡器正反馈特性产生振荡电压,通过测量了解各参数对频率、幅度的影响。

三、实验设备 1.双踪示波器 2.频率计 3.万用表 4.实验板12 四、实验内容1. 设置静态工作点2. 振荡频率与振荡幅度的测试3. 当C 、C ′为不同数值时,改变I EQ (断开C T ,由数字万用表测出V E 值,根据4R V I EE4.频率稳定度的影响 五、实验步骤实验电路见图1。

实验前根据图1所示原理图在实验板上找到相应器件及插孔并了解其作用。

1.设置静态工作点(1)在实验板+12V 扦孔上接入+12V 直流电源(注意电源极性不能接反)并按C=120pf 、C ′=680pf 、C T =51Pf (实验板标为50Pf )、R L =110K 接入各元件其连线要尽量短)。

(2)OUT 端至地接入双踪示波器和频率计(以函数信号发生器代),分别打开电源开关,此时频率计应显示振荡频率,调节R P 使双踪示波器显示振荡波形最大时停止调节,断开C 、 C ′、C T 及R L ,用数字万用表测出V E (R 4上的电压),代入下式求得I E 值。

4R V I EE == (1) 设:R e =1KΩ 表12.振荡频率与震荡幅度的测试 实验条件: C=120pf 、C ′=680pf 、R=110K当电容C T 分别为C 9、C 10、C 11时,由频率计读出其相应的f 值及由双踪示波器读出V P-P (V P-P 为输出电压峰峰值)值,并填入表1中。

3.当C 、C ′为不同数值时,改变I EQ (断开C T ,由数字万用表测出V E 值,根据4R V I EE =计算)为表格2所示系列值,由双踪示波器读出V L 值(取R=110K Ω、C T =50Pf ),并填入表2中(读取V L 值时去掉万用表)。

高频——实验报告

实验一正弦波振荡器一、实验目的1了解三点式正弦波振荡器电路的基本原理,起振条件,振荡电路设计及电路参数计算。

2通过实验掌握晶体管静态工作点、反馈系数、负载变化对起振和振荡幅度的影响。

3研究外界条件(温度、电源电压、负载变化)对角振荡器频率稳定度的影响。

4测量振荡器的反馈系数、波段复盖系数、频率稳定度等参数。

二、实验设备TKGPZ-1型高频电子线路综合实验箱;双踪示波器;频率计繁用表。

三、实验内容1熟悉振荡器模块各元件及其作用;2进行LC振荡器波段工作研究;3研究LC振荡器中静态工作点、反馈系数以及负载对振荡器的影响;4测试LC振荡器的频率稳定度。

三、基本原理将开关S2的1拨上2拨下,S1全部断开,由晶体管Q3和C13、C20、C10、CCI、L2构成电容三点式反馈振荡器的改进型振荡器——西勒振荡器,电容CCI可用来改变振荡器频率。

f=振荡器频率约为4.5MHZ振荡电路反馈系数:1320560.12 470CFC==≈振荡器输出通过耦合电容C3加到由Q2组成的射极跟随器的输入端,因C3容量很小,再加上射随器的输入阻抗很高,可以减小负载对振荡器的影响。

四、实验步骤1研究振荡器静态工作点对振荡幅度的影响。

2将开关S2的1拨上,构成LC振荡器。

3改变上偏置电位器RA1,并用示波器测量对应点的振荡幅度Vp-p,记下停振时的静态工作点电流值。

五、实验结果1、组成LC西勒振荡器:短接K1011-2、K1021-2、K103 1-2、K1041-2,并在C107处插入1000p的电容器,这样就组成了LC西勒振荡器电路。

用示波器(探头衰减10)在测试点TP102观测LC振荡器的输出波形,再用频率计测量其输出频率。

2、调整静态工作点:短接K104 2-3(即短接电感L102),使振荡器停振,并测量三极管BG101的发射极电压Ueq;然后调整电阻R101的值,使Ueq=0.5V,并计算出电流Ieq(=0.5V/1K=0.5mA)。

高频电路的设计与仿真方法

高频电路的设计与仿真方法电子与电气工程是现代科技发展中不可或缺的重要学科,它涵盖了电子、电气、通信等领域的理论与技术。

其中,高频电路的设计与仿真是电子与电气工程中的一个重要分支,它在无线通信、雷达、卫星导航等领域起着关键作用。

本文将介绍高频电路的设计与仿真方法,帮助读者了解高频电路的基本原理和实践应用。

一、高频电路的基本原理高频电路是指工作频率在几十千赫兹(kHz)到几百千兆赫兹(GHz)范围内的电路。

与低频电路相比,高频电路在设计和分析上面临着更多的挑战,因为高频信号的特性与传统电路有很大的差异。

高频电路的主要特点包括:信号传输路径长度较短、电路元件尺寸较小、电磁波传播效应显著等。

因此,高频电路的设计与仿真需要考虑到这些特点,并采用相应的方法与工具。

二、高频电路设计的基本步骤高频电路的设计过程可以分为以下几个基本步骤:需求分析、电路拓扑设计、元件选择、参数计算、电路布局与布线、仿真与调试等。

需求分析是高频电路设计的第一步,它需要明确电路的功能需求、工作频率范围、性能指标等。

在电路拓扑设计阶段,设计师需要选择适合的电路结构和拓扑,以满足设计需求。

元件选择是指根据设计要求选择合适的电子元件,如电容、电感、晶体管等。

参数计算是根据电路设计需求,计算各个元件的参数值,如电容的容值、电感的感值等。

电路布局与布线是将元件按照一定的布局规则进行布置,并通过导线进行连接。

最后,通过仿真与调试可以验证电路的性能指标是否满足设计要求,并进行必要的优化。

三、高频电路的仿真方法在高频电路设计中,仿真是一种重要的工具,它可以帮助设计师预测电路的性能、验证设计的正确性,并进行性能优化。

常用的高频电路仿真方法包括:基于电磁场的三维电磁仿真、基于电路的线性仿真和非线性仿真。

基于电磁场的三维电磁仿真是一种较为精确的仿真方法,它可以考虑到电磁波在电路中的传播和反射等效应。

该方法使用专业的电磁场仿真软件,如Ansys HFSS、CST Microwave Studio等,通过建立几何模型、设置边界条件和材料参数等,对电磁场进行数值求解,得到电路的电磁特性。

电路中的高频电路和射频电路设计

电路中的高频电路和射频电路设计电子技术的不断发展,使得无线通信技术得到了迅速的发展和普及。

在无线通信领域中,高频电路和射频电路起着至关重要的作用。

本文将重点探讨电路中的高频电路和射频电路设计,并且对其原理和应用进行分析。

一、高频电路设计高频电路是指工作频率在数百千赫至数百兆赫范围内的电路。

在高频电路设计中,需要考虑的因素众多,如材料的损耗、电路的稳定性和抗干扰能力等。

下面,将从材料选择、布局设计和电源稳定性等方面来介绍高频电路设计的要点。

1. 材料选择在高频电路设计中,材料的选择是至关重要的。

因为不同材料的特性会对电路的性能产生重大影响。

例如,导体材料的电导率和损耗因子应该尽可能低,以减小信号的损耗。

绝缘材料应具有良好的绝缘性能和低介电常数,以减小信号的衰减和交叉干扰。

2. 布局设计在高频电路设计中,布局设计对电路的性能起着重要作用。

首先,将不同的功能模块分开布局,以减少干扰和串扰。

同时,要合理布局信号线和电源线,减小信号传输的损耗和电源的波动。

3. 电源稳定性高频电路对电源的稳定性要求非常高,因为电源波动会直接影响到电路的性能和稳定性。

因此,在设计中需要添加稳压电路、滤波电路和抑制电感电容等元件,以保证电源的稳定性。

二、射频电路设计射频电路是指工作频率在几十兆赫至几百千赫范围内的电路。

射频电路设计相比于普通的电路设计更为复杂,需要更高的技术水平和更深入的理解。

以下将从天线设计、功率放大器设计和滤波器设计等方面来介绍射频电路设计的要点。

1. 天线设计天线作为射频电路的重要组成部分,其设计直接影响到无线通信的传输性能。

在天线设计中,需要考虑天线的频率响应、增益、辐射图案等因素。

同时,还需要避开电路干扰,减小天线和其他器件的耦合。

2. 功率放大器设计功率放大器在射频电路中承担着放大和传输信号的重要任务。

功率放大器设计的关键是选择合适的放大器结构和参数,以满足射频信号的要求。

在设计过程中,需要注意功率放大器的线性度、效率和稳定性等因素。

高频电路设计

高频电路设计Download tips: This document is carefully compiled by this editor. I hope that after you download it, it can help you solve practical problems. The document can be customized and modified after downloading, please adjust and use it according to actual needs, thank you! In addition, this shop provides you with various types of practical materials, such as educational essays, diary appreciation, sentence excerpts, ancient poems, classic articles, topic composition, work summary, word parsing, copy excerpts, other materials and so on, want to know different data formats and writing methods, please pay attention!是电子工程领域中一项重要的研究方向,它涉及到的频率范围一般在几百兆赫兹至几夸兆赫兹之间。

在通信、雷达、卫星导航等领域,高频电路的设计应用广泛,因此对于工程师来说,了解高频电路设计的原理和方法是非常必要的。

一、高频电路设计的基础知识在进行高频电路设计之前,首先需要了解一些基础知识。

高频电路的特点是在设计时需要考虑电磁波的传输和辐射效应,因此对于传输线、滤波器、功率放大器、混频器等组件的特性要有深入的了解。

高频电子线路实验指导书

高频电子线路实验指导书(总14页)--本页仅作为文档封面,使用时请直接删除即可----内页可以根据需求调整合适字体及大小--高频电子线路实验指导书钓鱼岛及其附属岛屿自古以来就是中国的固有领土。

主权不容侵犯,领土不容抢夺。

上图为美丽的钓鱼岛。

实验地点:航海西楼 308 室实验要求1.实验前必须充分预习,完指定的预习任务,预习要求如下:1)。

认真阅读实验指导书,分析,掌握实验电路的工作原理,并进行必要的估算。

2)。

完成各实验“预习要求”中指定的内容。

3)。

熟悉实验任务。

4)。

复习实验中使用各仪器的使用方法及注意事项。

2.使用仪器和实验仪前必须了解其性能,操作方法和注意事项。

3.实验时接线要认真,相互仔细检查,确定无误后才能接通电源,初学或没有把握应经指导老师审查同意后再接通电源。

4.高频电路实验注意事项:1)。

卡式高频电路实验仪将实验板插入主机插座后,即已接通地线,但实验板所需的正负电源则要另外使用导线进行连接。

2)。

由于高频电路频率较高,分布参数及相会感应的影响较大,所以在接线时连接线要尽可能短,接地点必须接触良好,以减少干扰。

3)。

做放大器实验时如发现波形失真甚至变成方波,应检查工作设置是否正确,或输入信号是否过大。

5.实验中有焊接电路时注意事项:1)。

应先提前给电烙铁通电预热,电烙铁要远离仪器设备和各种测量线,以防烧坏仪器和测量线,导线等,做完实验要拔掉电烙铁,关断电源,防止火灾。

2)。

老师分发的元器件,根据元件列表进行清点,缺少的应让老师补齐。

3)。

有运算放大器电路,运算放大器不能直接焊在电路板上,应先焊上插座,等电路都焊接完成后,再插上运算放大器,电路检查无误后,才能接通电源。

4)。

焊接电路时要合理布局,地线和电源线要用不同颜色的导线,一般电源线要用红线,这样一来电源就不会接错。

5)。

尽量节约使用导线,焊锡,勤俭节约,注意环境卫生。

6)。

实验中故意损坏仪器设备,要按原价赔偿。

6.实验时应注意观察,若发现有破坏性异常现象(例如有元件冒烟,发烫或有异味)应立即关断电源,保持现场,报告指导老师。

高频电子线路课程设计实验报告

高频电子线路课程设计报告班级姓名指导教师日期前言:课程设计是电子技术课程的实践性教学环节,是对学生学习电子技术的综合性训练,该训练通过学生独立进行某一课题的设计、安装和调试来完成。

学生通过动脑、动手解决若干个实际问题,巩固和运用在高频电子线路课程中所学的理论知识和实验技能,基本掌握常用电子电路的一般设计方法,提高设计能力和实验技能,为以后从事电子电路设计、研制电子产品打下基础。

本文设计了包括选频网络的设计、超外差技术的应用和三点式振荡器在内的基础设计以及振幅调制与解调电路的设计。

选频网络应用非常广泛,可以用作放大器的负载,具有阻抗变换、频率选择和滤波的功能;超外差技术是指利用本地产生的振荡波与输入信号混频,将输入信号频率变换为某个预定的频率的电路,主要指混频电路;三点式振荡器用于产生稳定的高频振荡波,在通信领域应用广泛;振幅调制解调都属于频谱的线性搬移电路,是通信系统及其它电子线路的重要部件。

在设计过程中查阅了大量相关资料,对所要设计的内容进行了初步系统的了解,并与老师和同学进行了充分的讨论与交流,最终通过独立思考,完成了对题目的设计。

实验过程及报告的完成中存在的不足,希望老师给予纠正。

目录摘要 (4)设计内容 (5)设计要求 (5)一、基础设计 (6)1、选频网络的设计 (6)2、超外差技术的设计 (9)3、三点式振荡器的设计 (11)二、综合设计:调幅解调电路的设计 (15)1、调幅电路的设计: (15)2、解调电路的设计 (20)结束语 (26)参考文献: (26)心得体会 (27)高频电子线路课程设计摘要本次课程设计主要任务是完成选频网络的设计、超外差技术的应用、三点式振荡器的设计这三个基础设计以及调幅解调电路的综合设计。

其中采用LC并联谐振回路实现谐振频率为8.2MHz,通频带为600KHZ的选频网络;对超外差技术原理进行了学习并针对其主要应用收音机进行详细的说明;对三点式振荡器的构造原则和主要类型进行简明扼要地介绍,采用电容串联改进型电容三点式振荡电路完成一定振荡频率的振荡器的设计;充分了解了调幅解调的原理并进行详细说明,在此基础上设计幅度调制和解调电路。

高频实验报告

(6)调节调制信号的大小,观察m=100%和m>100%两种调幅波在过零点处的波形情况,比较他们的区别。

3.普通调幅波解调

(1)将示波器CH2接幅度调制模块中调幅波输出端J23(TF.OUT)。根据实验步骤调节红色旋钮VR5将输出信号设置为峰峰值为Vp-p=150mv左右的调幅信号,并调整调制信号大小使调幅度m<30%。

实验报告

课程名称:高频电子线路实验

实验项目:正弦波振荡器、振幅调制与解波

实验仪器:

系别:光电信息与通信工程

专业:通信工程

班级/学号:

学生姓名:

实验日期

成绩

实验一正弦波振荡器

一、实验目的:

1、掌握三端式振荡电路的基本原理,起震条件,振荡电路设计及电路参数计算。

2、通过实验掌握晶体管静态工作点、反馈系数大小、负载变化对起振和振荡幅度的影响。

CAP可变为C7、C14、C23、C19其中一个。为了满足起振条件的要求F的值不能太大也不能太小,通常取为1/3-1/8。其中Cj为变容二极管2CC1B,根据所加的静态电压对去静态电容,CT3为5-20PF的半可变电容。该高频等效电路未考虑负载电阻。西勒电路是在克拉波电路的基础上在电感两端并联了一个小电容,且满足CAP远大于(CT1+CT17),故其回路等效电容C≈CT1+CT17+Cj。故振荡频率f0=1/2л 。西勒电路在分立元件系统或集成高频电路系统中均获得广泛的应用。

用MC1496集成电路构成的条幅电路如下图所示,图中VR8用调节引出脚1、4之间平衡,R39与R46与电位器VR8组成平衡调节电路,改变VR8可以调节输出载波信号的大小,以使乘法器实现抑制载波的振幅调制或有载的振幅调制,脚1和脚4分别接电阻R43和R49可以较好的抑制载波漏信号和改变温度性能,器件采用双电源供电方式

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

• Separate Power for digital, analog and Crystal

Bead Digital Crystal

47uF 0.1uF back

Decouple Cap.

• Put decouple capacitors at every pair of P/G

• As near as possible

back

Power/Ground Lines

• Width of P/G Ring around core enough for average current of whole chip 1um 1mA

• P/G trunks space and width

back

Heat

• Bipolar Higher Temperature Higher Current “Thermal Run Away”.

• Clock Tr/Tf as small as possible to avoid jitter

back

Power/Ground

Regulator

• All ground connected

Power

• Ground-Sea as large asSupply possible

Analog1 Analog2

• CMOS Higher Temperature Lower Current Worse speed performance

• IC dice is hotter than package surface • 散熱片

back

Clock

• Low speed Clock/Reset signal must have Schmidt-trigger as input buffer

Chip 47uF 0.1uF

back

Clock Lines

• Clock: any signal triggering other circuit by edges

• Apart from other signals as far as possible • As short as possible • If a jump line is needed, use ground line to

高頻電路的設計及測試

江明澄

Index

• IC A Extracted Cap. A Power/Ground Pins A Power/Ground

Lines A Heat A Clock

• PCB A Power/Ground A Decouple Cap. A Clock Lines

• Q&A D

• Separate P/G for I/O, Core, and Crystal • Separate P/G for analog and digital • Dedicated P/G for high driving I/O • Put pins of every P/G pair together • As many as possible • Arranged around whole chip

Extracted Cap.

• Coupled Ca.

back

Miller Effect of Extracted Cap.

CLK 3.3V 0V

CLKB 0V 3.3V

Q=C*V=C*2*3.3=(2*C)*3.3

CLK CLKB back

Power/Ground Pins

shield.

back

Q&A

• Why Slot Rule? • Why Antenna Rule? • What is CMP? Why?

back