四位十进同步可逆计数器

同步和异步十进制加法计数器的设计

同步和异步十进制加法计数器的设计全文共四篇示例,供读者参考第一篇示例:同步和异步是计算机系统中常用的两种通信机制,它们在十进制加法计数器设计中起到了至关重要的作用。

在这篇文章中,我们将深入探讨同步和异步十进制加法计数器的设计原理及应用。

让我们来了解一下十进制加法计数器的基本概念。

十进制加法计数器是一种用于执行十进制数字相加的数字电路。

它通常包含多个十进制加法器单元,每个单元用于对应一个十进制数位的运算。

在进行加法操作时,每个数位上的数字相加后,可能会产生进位,这就需要进位传递的机制来满足计数器的正确操作。

在同步十进制加法计数器中,每个十进制加法器单元都与一个时钟信号同步,所有的操作都按照时钟信号的节拍来进行。

具体来说,当一个数位的加法计算完成后,会将结果通过进位端口传递给下一个数位的加法器单元,这样就能确保每个数位的计算都是按照特定的顺序来进行的。

同步十进制加法计数器的设计较为简单,在时序控制方面有很好的可控性,但由于需要受限于时钟信号的频率,其速度受到了一定的限制。

在实际应用中,根据不同的需求可以选择同步或异步十进制加法计数器。

如果对计数器的速度要求较高,并且能够承受一定的设计复杂度,那么可以选择异步设计。

如果对计数器的稳定性和可控性要求较高,而速度不是首要考虑因素,那么同步设计可能更为适合。

无论是同步还是异步,十进制加法计数器的设计都需要考虑诸多因素,如延迟、数据传输、进位控制等。

通过合理的设计和优化,可以实现一个高性能和稳定的十进制加法计数器,在数字电路、计算机硬件等领域中有着广泛的应用。

同步和异步十进制加法计数器的设计都有其各自的优势和劣势,需要根据具体的需求来选择合适的设计方案。

通过不断的研究和实践,我们可以进一步完善十进制加法计数器的设计,为计算机系统的性能提升和应用拓展做出贡献。

希望这篇文章能够为大家提供一些启发和帮助,让我们共同探索数字电路设计的奥秘,开拓计算机科学的新境界。

第二篇示例:同步和异步计数器都是数字电路中常见的设计,用于实现特定的计数功能。

十进制可逆计数器74LS192引脚图管脚及功能表

十进制可逆计数器74LS192引脚图管脚及功

能表

2011年05月19日11:22 本站整理作者:本站用户评论(0)

关键字:

十进制可逆计数器74LS192引脚图管脚及功能表

74LS192是同步十进制可逆计数器,它具有双时钟输入,并具有清除和置数等功能,其引脚排列及逻辑符号如下所示:

图5-4 74LS192的引脚排列及逻辑符号

(a)引脚排列(b) 逻辑符号

图中:为置数端,为加计数端,为减计数端,为非同步进位输出端,为非同步借位输出端,P0、P1、P2、P3为计数器输入端,为清除端,Q0、Q1、Q2、Q3为数据输出端。

其功能表如下:

74ls00 是常用的2输入四与非门集成电路,他的作用很简单顾名思义就是实现一个与非门。

Vcc 4B 4A 4Y 3B 3A 3Y

┌┴—┴—┴—┴—┴—┴—┴┐

__ │14 13 12 11 10 9 8│

Y = AB )│ 2输入四正与非门 74LS00

│ 1 2 3 4 5 6 7│

└┬—┬—┬—┬—┬—┬—┬┘

1A 1B 1Y 2A 2B 2Y GND

<74LS00引脚图>

74LS00真值表:

A=1 B=1 Y=0

A=0 B=1 Y=1

A=1 B=0 Y=1

A=0 B=0 Y=1

表5-2 74LS192的功能表

[图]74LS20管脚图74LS27管脚图

74LS20管脚图74LS27管脚图

(5) 74LS20四输入双与非门,管脚图如附图1-31所示。

(6) 74LS27三输入三或非门,管脚图如附图1-32所示。

实验二异步复位十进制可逆计数器

实验二异步复位十进制可逆计数器一、实验目的:学习时序电路的设计、仿真和硬件测试,进一步熟悉VHDL设计技术。

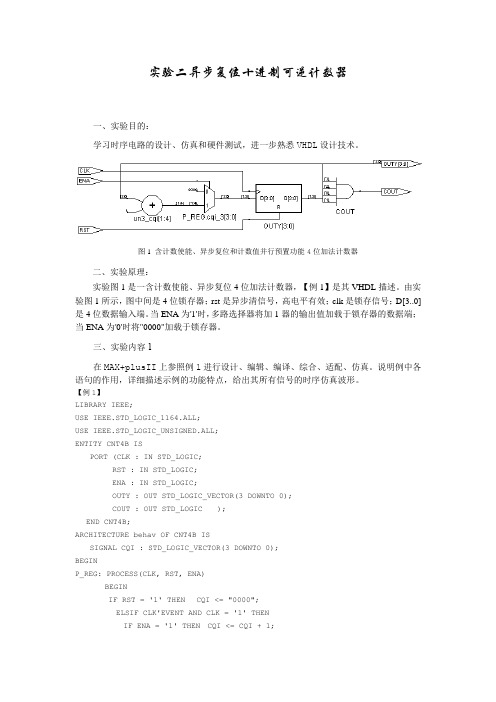

图1 含计数使能、异步复位和计数值并行预置功能4位加法计数器二、实验原理:实验图1是一含计数使能、异步复位4位加法计数器,【例1】是其VHDL描述。

由实验图1所示,图中间是4位锁存器;rst是异步清信号,高电平有效;clk是锁存信号;D[3..0]是4位数据输入端。

当ENA为'1'时,多路选择器将加1器的输出值加载于锁存器的数据端;当ENA为'0'时将"0000"加载于锁存器。

三、实验内容1在MAX+plusII上参照例1进行设计、编辑、编译、综合、适配、仿真。

说明例中各语句的作用,详细描述示例的功能特点,给出其所有信号的时序仿真波形。

【例1】LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT4B ISPORT (CLK : IN STD_LOGIC;RST : IN STD_LOGIC;ENA : IN STD_LOGIC;OUTY : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);COUT : OUT STD_LOGIC );END CNT4B;ARCHITECTURE behav OF CNT4B ISSIGNAL CQI : STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINP_REG: PROCESS(CLK, RST, ENA)BEGINIF RST = '1' THEN CQI <= "0000";ELSIF CLK'EVENT AND CLK = '1' THENIF ENA = '1' THEN CQI <= CQI + 1;END IF;END IF;OUTY <= CQI ;END PROCESS P_REG ; --进位输出COUT<=CQI(0) AND CQI(1) AND CQI(2) AND CQI(3);END behav;四、实验内容2:将实验内容1中的计数器改为十进制可逆计数器, 进行设计、编辑、编译、综合、适配、仿真;并进行引脚锁定以及硬件下载测试。

同步计数器

根据二进制加法运算规则可知,在一个多位二进制数的末位上加1时, 若其中第 i 位(即任何一位)以下各位皆为1时,则第 i 位应改变状态 (由0变成1,由l变成0)。而最低位的状态在每次加1时都要改变。

由此,当计数器用 T 触发器构成时,第 i 位触发器输入端的逻,n-1) 只有最低位例外,每次输入计数脉冲时它都要翻转,故T0=1

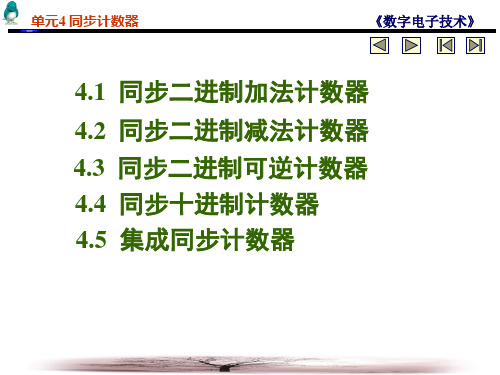

单元4 同步计数器

《数字电子技术》

单元4 同步计数器

《数字电子技术》

单元4 同步计数器

《数字电子技术》

单元4 同步计数器

课堂练习

《数字电子技术》

1、试分析时序电路的逻辑功能,写出电路的驱动方程、状 态方程和输出方程,画出电路状态转换图,检查电路能否 自启动。

R ____

J

____

K

____

F

;

单元4 同步计数器

《数字电子技术》

(2)圆心编程

圆心编程

条件

平面选择

旋转方向 G90时

终点位置 G时

圆心的坐标

指令 G17 G18 G19 G02 G03 X、Y、Z

X、Y、Z I、J、K

说明 圆弧在XY平面上 圆弧在ZX平面上 圆弧在YZ平面上

顺时针方向 逆时针方向 终点数据是工件坐标系中的坐标值

自动倒棱角

在倒棱/倒角过程中有的情况在倒角/倒棱前加“,”; 有的情况下不加

N0010 G91 G01 X100.0,C10.0; N0020 X100.0 Y100.0;

单元4 同步计数器

《数字电子技术》

单元4 同步计数器

2.任意角度倒棱角C/倒圆弧R

R后的数值指令倒圆R的半径值。 N0010 G91 G01 X100.0,R10.0; N0020 X100.0 Y100.0;

西交《数字逻辑电路》在线作业答卷

B.A+C

C.(A+B)(A+C)

D.AB

答案:C

12.将十进制小数转换为二进制数一般采用( )

A.乘2取整法

B.乘2取余法

C.乘10取整法

D.乘10取余法

答案:A

13.下列逻辑式中,正确的是( )

A.A+A=A

B.A+A=1

C.A+A=0

D.A·A=1

B.并行输入串行输出方式

C.串行输入并行输出方式

D.串行输入串行输出方式

答案:C

24.通常寄存器应具有( )功能。

A.清零和置数

B.存数和取数

C.只有存数、取数和清零,没有置数

D.A和B都有

答案:C

25.表示两个相邻脉冲重复出现的时间间隔的参数叫( )

A.脉冲周期#脉冲宽度#脉冲前沿#脉冲后沿

西交《数字逻辑电路》在线作业

试卷总分:100 得分:100

一、单选题 (共 25 道试题,共 50 分)

1.一个最大4位的十进制数转换成二进制数,至少需要( )位

A.9

B.7

C.12

D.10

答案:C

2.当x = -10000时,则有( )

A.[x] 补 = 110000

B.[x] 补 = 101111

答案:A

14.对于四变量逻辑函数,最小项有( )个

A.4

B.16

C.1

D.0

答案:B

15.对于JK触发器,输入J=0、K=1,CP脉冲作用后,触发器的Qn+1应为( )

同步可逆十进制计数器verilog代码

同步可逆十进制计数器verilog代码以下是一个同步可逆十进制计数器的Verilog代码:```module sync_reversible_counter(input clk, // 输入时钟信号input reset, // 输入复位信号output reg [3:0] count // 输出计数器值);// 定义状态变量reg [2:0] state;// 初始化状态变量和计数器值initial beginstate = 3'b000;count = 4'b0000;end// 状态转移逻辑always @(posedge clk) beginif (reset) begin // 复位信号为高电平时,将状态变量和计数器值重置为初始值state <= 3'b000;count <= 4'b0000;end else begin // 否则进行状态转移操作case (state)3'b000: begin // 当前状态为000时,下一状态为001,计数器加1state <= 3'b001;count <= count + 1;end3'b001: begin // 当前状态为001时,下一状态为010,计数器加1state <= 3'b010;count <= count + 1;end3'b010: begin // 当前状态为010时,下一状态为011,计数器加1state <= 3'b011;count <= count + 1;end3'b011: begin // 当前状态为011时,下一状态为100,计数器加1state <= 3'b100;count <= count + 1;end3'b100: begin // 当前状态为100时,下一状态为101,计数器加1state <= 3'b101;count <= count + 1;end3'b101: begin // 当前状态为101时,下一状态为110,计数器加1state <= 3'b110;count <= count + 1;end3'b110: begin // 当前状态为110时,下一状态为111,计数器加1state <= 3'b111;count <= count + 1;end3'b111: begin // 当前状态为111时,下一状态为000,计数器加1state <= 3'b000;count <= count + 1;endendcaseendendendmodule```这个Verilog代码实现了一个同步可逆十进制计数器。

同步十进制计数器

同步与异 步十进制计数 器的功能和工 作波形相同, 但时钟控制方 式及电路构成 不同。 计数顺序 0 1 2 3 4 5 6 7 8 9 10 计

Q3 0 0 0 0 0 0 0 0 1 1 0

数 器 状 Q2 Q1 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 0 0 0 0 0 0

本节小结:

计数器是一种应用十分广泛的时序电路,除 用于计数、分频外,还广泛用于数字测量、运算 和控制,从小型数字仪表,到大型数字电子计算 机,几乎无所不在,是任何现代数字系统中不可 缺少的组成部分。 计数器可利用触发器和门电路构成。但在实 际工作中,主要是利用集成计数器来构成。在用 集成计数器构成N进制计数器时,需要利用清零 端或置数控制端,让电路跳过某些状态来获得N 进制计数器。

Q0高 Q1高 Q2高 Q3高 CTT CT74LS161 CO CTP (高位) CR LD D0 D1 D2 D3 1 1 × ×××

1

1

1 × ×××

讨论

将上图中的“161”换成“160”,则构成几进制计数器?

讨论总结

(1)两个十进制计数器级联构成 100 进制计数器。从高位 Q3 Q2 Q1 Q0 读出的是十位数,而从低位 Q3 Q2 Q1 Q0 读出 的是个位数。 (2)两个 4 位二进制计数器级联则构成 8 位二进制计数器, 即 256 进制计数器。从高位 Q3 Q2 Q1 Q0 读出的是高 4 位 二进制数,而从低位 Q3 Q2 Q1 Q0 读出的是低 4 位二进制

方案 2: 用 “160” 的后七个状态 0011 ~ 1001 实现七进制计数。 计数顺序 0 1 2 3 4 5 6 7 8 9 10 计 数 器 状 态 进位输出 Q3 Q2 Q1 Q0 CO 0 0 0 0 0 D3D2D1D0=0011 0 0 0 1 0 0 0 1 0 0 0 0 1 1 0 0 1 0 0 0 0 1 0 1 0 0 1 1 0 0 LD = Q3 Q0或CO 0 1 1 1 0 1 0 0 0 0 1 0 0 1 1 0 0 0 0 0

4位10进制计数器

4位10进制计数显示模块设计

一、实验目的:设计4位10进制计数显示模块。

二、实验要求:

(1)、叙述设计思想;

(2)、4位10进制计数显示模块的VHDL描述;

(3)、画出顶层VHDL文件的图形描述;

(4)、调试程序、下载到实验板验证设计的正确性。

三、实验步骤

1、设计思路

4位10进制计数显示要实现四位数有0000开始,没过1s自动加1,并且可以循环计数。

同时,有使能端(ENA)可以控制暂停计数和继续计数,有复位端(RST)可以是四位数复位(0000)。

要实现这个功能需要用到6个主要元件:分频器、计数器、数码管显示译码器、段控制元件、位选择元件和动态扫描元件。

过程如下图图1所示。

图1

2、实验各个模块的VHDL描述:(1)、分频器元件的VHDL语言

(2)、十进制计数器元件的VHDL语言

(3)、动态扫描元件的VHDL语言(4)、位控制元件的VHDL语言

(5)七段数码显示译码器VHDL语言(6)、段控制元件的VHDL语言

3、顶层VHDL文件的图形描述

4、调试程序、下载到实验板验证设计的正确性。

通过对程序进行调试和引脚合理的分配之后,将程序下载到实验板上,实验结果与预期的一样。

四、实验体会

通过该次实验,对VHDL语言的基本用法和作用有了更深入的理解,运用起来更加熟练;同时,通过元件生成和顶层文件的图形描述,使我对quartus II软件的使用有了更深入了解,这使得我CPLD设计过程更加熟练。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

四位十进同步可逆计数器.

CLK接口接入由脉冲模块产生的脉冲,PL由主持人模块发出信号经过一个非门接入,控制计时开始,D/U’接高电平构成减法器,D0和D3接高电平D1和D2接低电平,E接地,输出Q0~Q3与4511的ABCD 相接4511的输出端Qa~Qg和LED数码管对应的接口相连接,LE接口由锁存模块提供经过一个或门接入控制锁存。

倒计时功能主要是利用74LS190计数芯片来实现,同时利用反馈和置数实现进制的转换,以适合分和秒的不同需要。

由于该系统特殊的需要,到各计时器到零时,通过停止控制电路使计数器停止计数并用LED发出警报

74LS190 十进制减计时器

CD4511 是一片CMOS BCD—锁存/7 段译码/驱动器,用于驱动共阴极LED (数码管)显示器的BCD 码—七段码译码器。

编辑本段特点

具有BCD转换、消隐和锁存控制、七段译码及驱动功能的CMOS 电路能提供较大的拉电流。

可直接驱动共阴LED数码管。

A0~A3:二进制数据输入端

/BI:输出消隐控制端

LE:数据锁定控制端

/LT:灯测试端

Ya~Yg:数据输出端

VDD:电源正

VSS:电源负

编辑本段推荐工作条件

电源电压范围:3V~18V

输入电压范围:0V~VDD

工作温度范围:M类-55℃~125℃E类-40℃~85℃

其中a b c d 为BCD 码输入,a为最低位。

LT为灯测试端,加高电平时,显示器正常显示,加低电平时,显示器一直显示数码“8”,各笔段都被点亮,以检查显示器是否有故障。

BI为消隐功能端,低电平时使所有笔段均消隐,正常显示时,B1端应加高电平。

另外CD4511有拒绝伪码的特点,当输入数据越过十进制数9(1001)时,

显示字形也自行消隐。

LE是锁存控制端,高电平时锁存,低电平时

CD4511和CD4518配合而成一位计数显示电路,若要多位计数,只需将计数器级联,每级输出接一只CD4511 和LED 数码管即可。

所谓共阴LED 数码管是指7 段LED 的阴极是连在一起的,在应用中应接地。

限流电阻要根据电源电压来选取,电源电压5V时可使用300Ω的限流电阻。

2.锁存功能

译码器的锁存电路由传输门和反相器组成,传输门的导通或截止由控制端LE的电平状态。

当LE为“0”电平导通,TG2截止;当LE为“1”电平时,TG1截止,TG2导通,此时有锁存作用。

如图3-3 (3)译码

CD4511译码用两级或非门担任,为了简化线路,先用二输入端与非门对输入数据B、C进行组合,得出

四项,然后将输入的数据A、D一起用

或非门译码。

(4)消隐

BI为消隐功能端,该端施加某一电平后,迫使B端输出为低电平,字形消隐。

消隐控制电路如图3-4所示。

消隐输出J的电平为 J=

=(C+B)D+BI

如不考虑消隐BI项,便得J=(B+C)D

据上式,当输入BCD代码从1010---1111时,J端都为“1”电平,从而使显示

理(转载于/wzhhuihui)

2011-05-25 14:15

数码管显示原理

我们最常用的是七段式和八段式LED数码管,八段比七段多了一个小数点,其他的基本相同。

所谓的八段就是指数码管里有八个小LED发光二极管,通过控制不同的LED的亮灭来显示出不同的字形。

数码管又分为共阴极和共阳极两种类型,其实共阴极就是将八个LED 的阴极连在一起,让其接地,这样给任何一个LED的另一端高电平,它便能点亮。

而共阳极就是将八个LED的阳极连在一起。

其原理图如下。

其中引脚图的两个COM端连在一起,是公共端,共阴数码管要将其接地,共阳数码管将其接正5伏电源。

一个八段数码管称为一位,多个

数码管并列在一起可构成多位数码管,它们的段选线(即

a,b,c,d,e,f,g,dp)连在一起,而各自的公共端称为位选线。

显示时,都从段选线送入字符编码,而选中哪个位选线,那个数码管便会被点亮。

数码管的8段,对应一个字节的8位,a对应最低位,dp对应最高位。

所以如果想让数码管显示数字0,那么共阴数码管的字符编码为00111111,即0x3f;共阳数码管的字符编码为11000000,即0xc0。

可以看出两个编码的各位正好相反。

如下图。

共阳极的数码管0~f的段编码是这样的:。