$sdf_annotate用法

逻辑综合及门级仿真

DATA STABLE tc 2

q

CLK t

Q

DATA STABLE

t

建立时间(Setup Time,tsu): 在触发时钟边沿之前输入必须稳定 保持时间(Hold Time, thold): 在触发时钟边沿之后输入必须保持 Clock-to-Q时间(tc2q):

– – 在触发时钟边沿,输出并不能立即变化 与逻辑门的延迟类似,也由两部分组成: 内在Clock-to-Q时间 负载相关Clock-to-Q时间

File -> Save 以DB格式保存综合后的结果 File -> Save As 以VHDL/Verilog形式输出电路网表

File -> Save Info -> Design Timing 输出时序反标文件

2008-11-11

清华大学微电子学研究所 张春

26/33

内容摘要

综合及相关基本概念

2008-11-11

清华大学微电子学研究所 张春

5/33

Cell(标准单元) Based ASIC

Use pre-designed logic cells (standard cells) in combination with larger cells (megacells) Standard Cells

2008-11-11

清华大学微电子学研究所 张春

13/33

文件及目录准备

源代码

库文件

建立工作目录work,用于保存中间文件 mkdir work 编写配置文件:.synopsys_dc.setup

define_design_lib work –path “./work” set target_library { /home/ic/library/typical.db } set link_library {* /home/ic/library/typical.db } set symbol_library { /home/ic/library/umc18.sdb }

ISE详细步骤

★ ISE详细步骤、作用及其理解:这里把仿真单独编号1)新建工程2)生成原文件手段CORE Generator ModuleLanguage Templates3) check syntax①Behavioral simulate我觉得从Synthesis and Simulation Design Guide文件看,应该先RTL Simulation (that is, Behavioral simulate )。

其实没有关系,综合和RTL仿真的顺序无所谓,这两个不一定要谁在前己见:注意跑行为仿真前是不需要综合的,仅是RTL代码仿真参考:[In-Depth Tutorial] Chapter 4 P914) Synthesis步骤:Entering Constraints (xcf格式) -> Entering Synthesis Options -> Synthsizing参考:[In-Depth Tutorial]P43-P50我觉得这里的constraints是 synthesis constraints:《cgd》p18已见:参《Xilinx ISE 9.X FPGA/CPLD设计指南(人民邮电)》P31综合是把HDL描述转化为使用基本门电路以及厂家库提供的基本单元进行描述的网表(Netlist)的过程。

综合时需要附加一定的约束,指导综合过程的进行,最常用的约束有管脚位置约束和附加时序约束② Post- Synthesis Simulation这里以《夏宇闻》第17章的设计为例,前面行为仿真时可以直接仿真cputop模块(专为仿真写的,不可综合),但在synthesize时,必须把cpu模块Set as Top Module,因为cputop模块是不可综合的,然后点击Generate Post-Synthesis Simulation Model,可以注意到原文件夹下会生成netgen文件夹,打开会发现有synthsis文件夹,里面有cpu_synthesis.v 文件,这个文件是专门用来仿真的。

Modelsim 自动化仿真平台搭建

Modelsim do文件的自动化仿真 创建虚拟信号

虚拟信号可以把实际信号转化为更人性化的信号,比如将信号的数值转化为字符显示,例如状 态机的跳转可以用虚拟信号标注这样更清晰。

virtual type { {1 IDLE} {2 READ} {4 WRITE} {8 STOP} } state_struc 以上简历一个虚拟的结构体,结构体的名字叫state_struc

Modelsim do文件的自动化仿真 Tcl语言的语法

vlib:创建库。格式vlib <library name>,默认库的名字为work 示例: vlib work vmap:映射逻辑库名,将逻辑库名映射库路径。语法格式vmap work <library name> 示例:vlib work work vdir:显示指定库的内容 。语法格式vdir –lib <library name> 示例:vdir –lib work vlog:编译Verilog 源代码,库名缺省编译到work本地库,文件按顺序编译。语法格式 vlog

modelsim将加载两次,这种结果不是我们想要的。 .SDO文件并不是标准的延时文件,如果想转到标准的延迟文件可以用以下命令,sdf文件比

sdo文件小加载速度快。sdf文件采用了gzip压缩。 sdfcom netlist/my_design.sdo netlist/my_design.sdf

Modelsim 自动化仿真平台源自Modelsim GUI仿真流程

1. 打开Modelsim 软件,建一个工程文件夹,简历Modelsim 仿真工程。 2. 在用户窗口界面加入需要仿真的所有代码和库文件。 3. 编译有文件 4. 选择testbench顶层文件启动仿真。 5. 选择所要观察的目标信号,并将其加入到波形观察窗口,如需更改bus显示

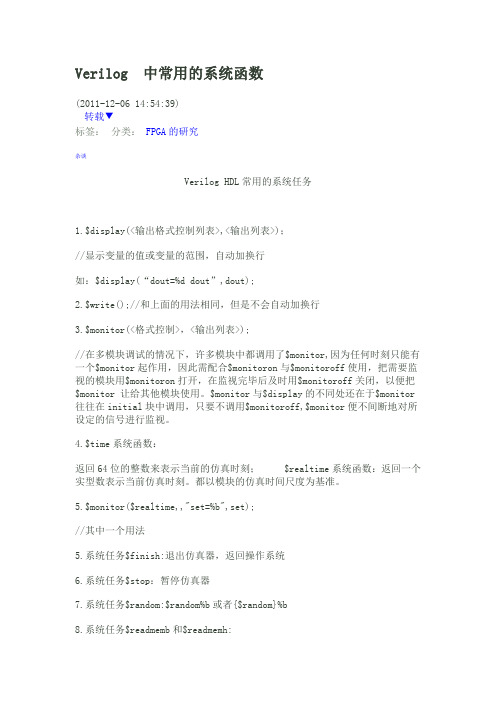

verilog系统函数解读

Verilog 中常用的系统函数(2011-12-06 14:54:39)转载▼标签:分类:FPGA的研究杂谈Verilog HDL常用的系统任务1.$display(<输出格式控制列表>,<输出列表>);//显示变量的值或变量的范围,自动加换行如:$display(“dout=%d dout”,dout);2.$write();//和上面的用法相同,但是不会自动加换行3.$monitor(<格式控制>,<输出列表>);//在多模块调试的情况下,许多模块中都调用了$monitor,因为任何时刻只能有一个$monitor起作用,因此需配合$monitoron与$monitoroff使用,把需要监视的模块用$monitoron打开,在监视完毕后及时用$monitoroff关闭,以便把$monitor 让给其他模块使用。

$monitor与$display的不同处还在于$monitor 往往在initial块中调用,只要不调用$monitoroff,$monitor便不间断地对所设定的信号进行监视。

4.$time系统函数:返回64位的整数来表示当前的仿真时刻; $realtime系统函数:返回一个实型数表示当前仿真时刻。

都以模块的仿真时间尺度为基准。

5.$monitor($realtime,,"set=%b",set);//其中一个用法5.系统任务$finish:退出仿真器,返回操作系统6.系统任务$stop:暂停仿真器7.系统任务$random:$random%b或者{$random}%b8.系统任务$readmemb和$readmemh:用于从文件中读取数据到寄存器中,任何时候都可以被执行(数据方向:文件>>寄存器);有以下用法:1) $readmemb("<数据文件名>",<存贮器名>);2) $readmemb("<数据文件名>",<存贮器名>,<起始地址>);3) $readmemb("<数据文件名>",<存贮器名>,<起始地址>,<结束地址>);4) $readmemh("<数据文件名>",<存贮器名>);5) $readmemh("<数据文件名>",<存贮器名>,<起始地址>);6) $readmemh("<数据文件名>",<存贮器名>,<起始地址>,<结束地址>);其中文件中的地址表示方式@hhhh--hh,但是寄存器中的地址可直接用数表示。

VCS简明使用教程

一、编译:VCS

-line 实现单步仿真,将会极大地增加运行时间 -mhdl 实现混合HDL语言的编译和仿真 +ad=<filename> 实现混合信号的编译和仿真 -nospecify 禁止模块路径延迟和时序检查,提高仿真速度 +notimingcheck 禁止时序检查任务,可以改善仿真速度 +vpdfile+filename 指定要写入的vpd文件名,而不用vcdplus.vpd +vpdupdate 同时读写vpd文件 +vpdfilesize+nMB 指定vpd文件的最大size +race 自动产生一个race.out文件,列出了竞争 +cli+1|2|3|4 指明仿真时用UCLI模式,后边不同的数字代表了不同的操作 级别,一般用3既可 +prof 产生一个名为vcs.prof的文件,报告CPU和memory的使用情况 -parallel +fc[=No1]|+sva[=No2]|+tgl[=No3]|+vpd[=No4] 使用多核处理 器的选项,若每个参数后不跟数字,则表示使用1级;fc为多核功能覆盖, sva为多核SystemVerilog断言,tgl为多核toggle覆盖,vpd为多核VCD+ dumping。No实际上就是使用的cpu核的个数。 -parallel -o para_bin_name 指定一个能使用多核技术的可执行文件名。 -timescale=1ns/10ps 指定仿真单位和时间精度

二、仿真:simv 运行选项

命令:simv runtime_options,以下是运行选项的说明:

-cm line|cond|fsm|tgl|path|branch -cm_dir directory 指明仿真将中间文件存在哪里 -l log_file 记录DVE或VCS的log文件 -gui 启动DVE -ucli 进入UCLI交互模式 -do ucli_command_file ucli_command_file是UCLI命令的列表文件 +vcs+stop+time 指定仿真运行中断的的时间 +vcs+finish+time 指定仿真运行结束的时间 -cm_glitch <period> 对于小于period的脉冲不进行覆盖 -cm_name <filename> 指明test文件的文件名 -cm_tglfile <filename> -cm_log <filename> 指明仿真期间关于coverage的log文件名 -q 安静模式 -sverilog -V verbose mode

modelsim笔记

vsim -c -t 10ps -lib simprim -sdfmax /DUV=G:/RTL/assign/assign_timesim.sdf work.assign_tb

-c --> command line simulation

-t --> time precision

-lib --> required libraries

Once you are done with synthesis. You will have your Netlist and your SDF file.

In case u use FPGA synthesis then you need Simprims

Now you need to add the SDF file in ur test bench. You can do this by $sdf_annotate("*.sdfude the sdf file, mention the region to which this SDF file acts upon, what kind of sdf simulation (sdfmax, min or typ), you need to include all the libraries which contain the components in your netlist. I had given a example from one of my designs.

Failed to find INSTANCE ’/testbench/u5’

** Warning (vsim-SDF-3432) myasic.sdf:

This file is probably applied to the wrong instance.

nc后仿_综合后仿真

选择Annotation一项, 在子菜单中选中除第一 项的所有条目。 在delay types中选择 Maximum一项,SDF 文件中对每项延时都有 最大值,典型值,最小 值,这里选择最大值用 于仿真

在上述步骤之后,会生成一个你的设计对应的snapshot,仿真 就是针对这个Snapshot进行的。如图示,选中该文件,点击 仿真按钮

点击

进入nc_postsim文件夹

双击spi_test1,打开并加入反标命令, 退出时记得保存:File->save

准备工作介绍

在仿真已有的设计以前,必须编译和描述它。编译 过程将把源文件中的用HDL编写的单元编译成内在 的描述。描述设计将在设计的实例化,结构化信息 的基础上建立设计的层次结构,建立信号的连接, 计算所有对象的初始值。编译,描述和仿真自己的 设计要用到以下的工具: Ncvlog: 编译Verilog源文件。 ncelab 描述设计并且生成仿真的snapshot。 ncsim 对snapshot进行仿真仿真。

NC-Verilog

综合后仿真

后仿概述

后仿是在前仿的基础上加入延时信息的功能 仿真。 同时验证了设计的时序以及功能都正确,并 且确保后仿功能和前仿一致。

实验任务

掌握前仿与后仿的区别 学会用NC-verilog对设计进行后仿 在SimVision分析环境下对设计中的问题进 行调试

前仿与后仿的区别

SPI_test1为测试模块 名,ex1为例化名

将ex1,ex2,ex3全部 应用sdf文件

仿真并得到器件延时信息

谢谢!

仿真所需文件

netlist.v:DC综合生成的网表文件 .sdf:DC综合生成的标准延时文件 ,这个文 件中包含了设计的网表中单元和连线的延时 信息。 smic25.v工艺库仿真文件,包含综合目标库 中元件的仿真模型信息

ModelSim常见错误原因及解决

1.常见错误:Failed to find INSTANCE ...,问题出在下面所示的第2步或第4步。

正确处理步骤:(1)Quartus中编译测试码欲调用的顶层模块(设模块名:xxx),设置EDA tool 的simulation 工具,如verilog ,以产生xxx.vo文件及xxx_v.sdo延时文件;(2)打开modelsim,新建工程,添加xxx.vo文件、测试用激励波形文件testbench.v、所用器件的网表文件(以cyclone为例:$Quartus\eda\sim_lib\cyclone_atoms.v)。

全部编译。

!!:确认testbench.v中不包含顶层模块xxx代码。

(3)xxx_v.sdo复制到modelsim工程目录。

(4)最后,建立仿真配置文件:在workspace的project页中右键单击,选simulation configuration,如下图于是,workspace中得到simulation 1。

按下图设置:注意,上面的框中添加xxx_v.sdo,下面的文本框中设置作用域,格式为:\testbench模块名\xxx的实例名。

(5)`timescale 影响仿真结果显示效果。

=================例===================[1]//文件count4.vmodule count4(out,reset,clk);output[3:0] out;input reset, clk;reg[3:0] out;always @(posedge clk)beginif (reset)out <= 0;elseout <= out + 1;endendmodule[2]//测试文件count_tp.v`timescale 1ns/1nsmodule count_tp;reg clk,reset;wire[3:0] out;parameter DELY = 100;count4 mycount(out,reset,clk);always #(DELY/2) clk = ~clk;initialbeginclk = 0; reset = 0;#DELY reset = 1;#DELY reset = 0;#(DELY*20) $finish;endinitial $monitor($time,,,"clk=%d reset=%d out=%d",clk,reset,out); endmodule[3]所用器件:cyclone[4]结果:明显产生了时延p.s.-----------------------网上有朋友指出勾选SDF中的两个选项,将原来的警告禁止,将原来的错误变为警告, 可以成功地进行反标注并运行仿真,但这样做并没有解决实际问题,只能产生功能仿真,没有得到带时延的时序仿真2.** Error: D:/ModelSim_6.5/ModelSimnear "'t": Illegal base specifier in numeric constant.syntax error, unexpected "BASE", expecting "class"错误原因:不是’timescale 而是`timescale,那个是键盘左上角的点,不是一撇。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

$sdf_annotate用法

一、概述

$s df_a nn ot at e是一个功能强大的工具,可以帮助用户对SD F文件进

行注释和标记。

通过$s df_a nn ot at e,用户可以在S DF文件中添加各种

注释和标记,以便于数据的分析、查询和可视化。

二、基本用法

1.安装和配置

首先,确保你的操作系统中已经安装了$s d f_an no ta te工具。

然后,

进入$s df_a nn ot ate的安装目录,并进行配置。

配置主要包括指定输入

文件路径、输出文件路径等参数。

2.添加注释

使用$s df_a nn ot ate可以轻松地给S DF文件中的化合物添加注释。

注

释可以包括分子式、分子量、化学名称等信息。

在命令行中输入以下命令

来添加注释:

$s df_a nn ot at e-iin p ut.s df-o ou tp ut.s df--

a n no ta te"m ol ec ula r_f or mu la"--a nno t at e"mo le cu la r_w e ig ht"--

a n no ta te"c he mi cal_na me"

这个命令将会在输出文件中添加分子式、分子量和化学名称的注释。

3.标记特定分子

除了注释功能之外,$s df_a nn ot a t e还可以帮助用户标记特定的分子。

标记可以根据用户指定的条件来进行,比如分子量大于某个阈值、含有特

定官能团等等。

以下是一个例子:

$s df_a nn ot at e-iin p ut.s df-o ou tp ut.s df--

m a rk"m ol ec ul ar_we i gh t>300"--

m a rk"s ub st ru ct ure('c1c cc cc1')"

这个命令将会在输出文件中标记分子量大于300和含有苯环的分子。

三、高级用法

1.自定义注释和标记

$s df_a nn ot at e支持自定义注释和标记。

用户可以根据自己的需要定义注释和标记的规则。

例如,用户可以添加一个自定义的注释"l og P"来计算化合物的疏水性:

$s df_a nn ot at e-iin p ut.s df-o ou tp ut.s df--

a n no ta te"l og P=cal c ul at e_lo gP()"

这个命令将会在输出文件中添加一个名为"l og P"的注释,其值为计算得到的化合物疏水性。

2.批量处理多个文件

$s df_a nn ot at e还支持批量处理多个SD F文件。

用户可以指定一个包含多个文件路径的列表,并通过循环迭代的方式进行处理。

以下是一个示例:

$s df_a nn ot at e-iin p ut1.sd fi np ut2.s d fi np ut3.sd f-

o o ut pu t1.s df ou tpu t2.sd fo ut pu t3.sd f

这个命令将会分别对三个输入文件进行处理,并将结果输出到相应的输出文件中。

四、总结

$s df_a nn ot at e是一个非常实用的工具,可以帮助用户对SD F文件进行注释和标记。

通过$s df_a nn ot at e,用户可以方便地添加注释、标记特定分子,甚至自定义注释和标记规则。

希望本文档对你理解和使用

$s df_a nn ot at e有所帮助。

如果有任何问题或建议,请随时与我们联系。

谢谢!。