第二章 8086系统结构

微机原理(杭州电子科技大学【4】8086系统结构[2-3]

![微机原理(杭州电子科技大学【4】8086系统结构[2-3]](https://img.taocdn.com/s3/m/3b8cd1f4f90f76c661371a65.png)

15:28

22

二、系统的复位与启动

【8086CPU时序】

① 复位信号:通过RESET引脚上的触发信号来引起8086系统复位和启

动,RESET至少维持4个时钟周期的高电平。

② 复位操作:当RESET信号变成高电平时,8086/8088CPU结束现行

操作,各个内部寄存器复位成初值。

标志寄存器

清零

指令寄存器 CS寄存器 DS寄存器 SS寄存器 ES寄存器

的比例倍频后得到CPU的主频,即: CPU主频 = 外频 × 倍频系数

⑥ PC机各子系统时钟(存储系统,显示系统,总线等)是由系统频率按 照一定的比例分频得到。

15:28

5

内频 550MHz Pentium III

倍频系数5.5

L1 Cache

L2 550MHz Cache

处理机总线 100MHz

微机原理与接口技术

第四讲

15:28

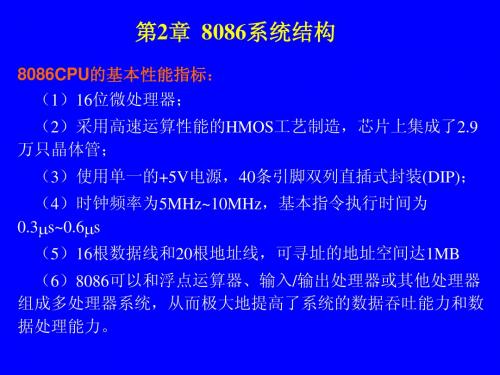

第二章 8086系统结构

内容提要

z微型计算机的发展概况 z8086CPU内部结构 z8086CPU引脚及功能 z8086CPU存储器组织 z8086CPU系统配置 z8086CPU时序

15:28

2

※有关概念介绍

z 主频,外频,倍频系数 z T状态 z 总线周期 z 指令周期 z 时序 z 时序图

总线操作

读存储器操作 (取操作数)

写存储器操作 (将结果存放到内存)

读 I/O 端口操作 (取 I/O 端口中的数)

写 I/O 端口操作 (往 I/O 端口写数)

中断响应操作

总线周期

存储器读周期 存储器写周期 I/O 端口读周期 I/O 端口写周期 中断响应周期

15:28

第2章-8086微处理器part2

8086 CPU在最小模式中引脚定义

M/#IO:Memory/Input & Output,三态输出

存储器或I/O端口访问信号 。指示8086的访问对象,发 给MEM或I/O接口。 M/# IO为高电平时,表示 当前CPU正在访问存储器;

M/# IO 为低电平时,表 示当前CPU正在访问I/O端 口

数据驱动器数据流向控制信 号,输出,三态。

在8086系统中,通常采用 74LS245、8286或8287作 为数据总线的驱动器,用 DT/#R信号来控制数据驱动 器的数据传送方向。 当DT/#R=1时,进行数据 发送; 当DT/#R=0时,进行数据 接收。

8086 CPU在最小模式中引脚定义

READY:准备就绪信号 由外部输入,高电平有效 ,表示CPU访问的存储器 或I/O端口己准备好传送 数据。 当READY无效时,要求 CPU插入一个或多个等待 周期Tw,直到READY信 号有效为止。

S3 0 1 0 1

当前正在使用的段寄存器 ES SS CS或未使用任何段寄存器 DS

8086 CPU在最小模式中引脚定义

#BHE/S7:高8位总线允许(Bus High Enable)

T1:指示高8位数据总线上的数据 是否有效 (#BHE:AD0)配合:00时读写字 ,01时读写奇地址字节,10时读写 偶地址字节 其他T周期:输出状态信号S7(S7 始终为逻辑1,未定义) DMA方式下,该引脚为高阻态。

最大模式引脚信号(续)

LOCK# :总线封锁(优先权锁定) 三态输出,低电平有效。 LOCK有效时表示CPU不允许其它总线主控者占用 总线。 ห้องสมุดไป่ตู้ 这个信号由软件设置。 • 当在指令前加上LOCK前缀时,则在执行这条 指令期间LOCK保持有效,即在此指令执行期 间,CPU封锁其它主控者使用总线。 在保持响应期间,LOCK#为高阻态。

第二章 8086体系结构

8086微处理器概览

标志位寄存器(FR) • 16位标志位寄存器FR,共有9个

标志位。其中6个是状态标志位, 3个是控制标志位,用于反映 CPU运行过程中的某些状态特征。

标志位寄存器

3、标志寄存器FR

标志寄存器FR中共有9个标志位,可分成两类: ➢状态标志 表示运算结果的特征,它们是 CF、PF、AF、 ZF、SF和OF ➢控制标志 控制CPU的操作,它们是IF、DF和TF。

IP :BIU要取指令的地址。

IP

三、8086CPU的管脚及功能

8086是16位CPU。它采用高性能的N— 沟道,耗尽型负载的硅栅工艺(HMOS)制 造。由于受当时制造工艺的限制,部分管 脚采用了分时复用的方式,构成了40条管 脚的双列直插式封装

1、 8086的两种工作方式

最小模式:系统中只有8086一个处理器,所有的控制信号都 是由8086CPU产生(MN/MX=1)。

最大模式:系统中可包含一个以上的处理器,比如包含协处 理器8087。在系统规模比较大的情况下,系统控 制信号不是由8086直接产生,而是通过与8086配 套的总线控制器等形成(MN/MX=0)。

三总线结构 数据线DB 地址线AB 控制线CB

微机的三总线结构

➢ 最小模式下的引脚说明

( 1 ) AD15 ~ AD0 (Address Data Bus):

堆栈指针用于存放栈顶的逻辑偏移地 址,隐含的逻辑段地址在SS寄存器中。

寄存器的特殊用途和隐含性质

在指令中没有明显的标出,而这些寄存器参 加操作,称之为“隐含寻址”。

具体的:在某类指令中,某些通用寄存器有指 定的特殊用法,编程时需遵循这些规定,将某些 特殊数据放在特定的寄存器中,这样才能正确的 执行这些指令。采用“隐含”的方式,能有效地 缩短指令代码的长度。

微机原理和接口技术(第三版)课本习题答案解析

第二章 8086 体系结构与80x86CPU1.8086CPU 由哪两部份构成?它们的主要功能是什么?答:8086CPU 由两部份组成:指令执行部件<EU,Execution Unit>和总线接口部件<BIU,Bus Interface Unit>。

指令执行部件〔EU 主要由算术逻辑运算单元<ALU>、标志寄存器F R、通用寄存器组和E U 控制器等4个部件组成,其主要功能是执行指令。

总线接口部件<BIU>主要由地址加法器、专用寄存器组、指令队列和总线控制电路等4个部件组成,其主要功能是形成访问存储器的物理地址、访问存储器并取指令暂存到指令队列中等待执行,访问存储器或者I/O 端口读取操作数参加E U 运算或者存放运算结果等。

2.8086CPU 预取指令队列有什么好处? 8086CPU 内部的并行操作体现在哪里?答: 8086CPU 的预取指令队列由6个字节组成,按照8086CPU 的设计要求, 指令执行部件〔EU 在执行指令时,不是直接通过访问存储器取指令,而是从指令队列中取得指令代码,并分析执行它。

从速度上看,该指令队列是在C PU 内部,EU 从指令队列中获得指令的速度会远远超过直接从内存中读取指令。

8086CPU 内部的并行操作体现在指令执行的同时,待执行的指令也同时从内存中读取,并送到指令队列。

5.简述8086 系统中物理地址的形成过程。

8086 系统中的物理地址最多有多少个?逻辑地址呢?答: 8086 系统中的物理地址是由20 根地址总线形成的。

8086 系统采用分段并附以地址偏移量办法形成20 位的物理地址。

采用分段结构的存储器中,任何一个逻辑地址都由段基址和偏移地址两部份构成,都是16 位二进制数。

通过一个20 位的地址加法器将这两个地址相加形成物理地址。

具体做法是16 位的段基址左移4位<相当于在段基址最低位后添4个"0">,然后与偏移地址相加获得物理地址。

微机原理课件第二章 8086系统结构

但指令周期不一定都大于总线周期,如MOV AX,BX

操作都在CPU内部的寄存器,只要内部总线即可完成,不 需要通过系统总线访问存储器和I/O接口。

2021/8/17

17

• 8086CPU的典型总线时序,充分体现了总 线是严格地按分时复用的原则进行工作的。 即:在一个总线周期内,首先利用总线传 送地址信息,然后再利用同一总线传送数 据信息。这样减少了CPU芯片的引脚和外 部总线的数目。

• 执行部件(EU)

• 功能:负责译码和执行指令。

2021/8/17

5

• 联系BIU和EU的纽带为流水指令队列

• 队列是一种数据结构,工作方式为先进先出。写入的指令 只能存放在队列尾,读出的指令是队列头存放的指令。

2021/8/17

6

•BIU和EU的动作协调原则 BIU和EU按以下流水线技术原则协调工作,共同完成所 要求的任务: ①每当8086的指令队列中有空字节,BIU就会自动把下 一条指令取到指令队列中。 ②每当EU准备执行一条指令时,它会从BIU部件的指令 队列前部取出指令的代码,然后译码、执行指令。在执 行指令的过程中,如果必须访问存储器或者I/O端口, 那么EU就会请求BIU,完成访问内存或者I/O端口的操 作; ③当指令队列已满,且EU又没有总线访问请求时,BIU 便进入空闲状态。(BIU等待,总线空操作) ④开机或重启时,指令队列被清空;或在执行转移指令、 调用指令和返回指令时,由于待执行指令的顺序发生了 变化,则指令队列中已经装入的字节被自动消除,BIU会 接着往指令队列装入转向的另一程序段中的指令代码。 (EU等待)

•CF(Carry Flag)—进位标志位,做加法时最高位出现进位或 做减法时最高位出现借位,该位置1,反之为0。

第二章 8086微处理器

第二章8086/8088微处理器及其系统结构内容提要:1.8086微处理器结构:CPU内部结构:总线接口部件BIU,执行部件EU;CPU寄存器结构:通用寄存器,段寄存器,标志寄存器,指令指针寄存器;CPU引脚及其功能:公用引脚,最小模式控制信号引脚,最大模式控制信号引脚。

2.8086微机系统存储器结构:存储器地址空间与数据存储格式;存储器组成;存储器分段。

3.8086微机系统I/O结构4.8086最小/最大模式系统总线的形成5.8086CPU时序6.最小模式系统中8086CPU的读/写总线周期7.微处理器的发展学习目标1.掌握CPU寄存器结构、作用、CPU引脚功能、存储器分段与物理地址形成、最小/最大模式的概念和系统组建、系统总线形成;2.理解存储器读/写时序;3.了解微处理器的发展。

难点:1.引脚功能,最小/最大模式系统形成;2.存储器读/写时序。

学时:8问题:为什么选择8088/8086?•简单、容易理解掌握•与目前流行的P3、P4向下兼容,形成x86体系•16位CPU目前仍在大量应用思考题1、比较8086CPU与8086CPU的异同之处。

2、8086CPU从功能上分为几部分?各部分由什么组成?各部分的功能是什么?3、CPU的运算功能是由ALU实现的,8086CPU中有几个ALU?是多少位的ALU?起什么作用?4、8086CPU有哪些寄存器?各有什么用途?标志寄存器的各标志位在什么情况下置位?5、8086CPU内哪些寄存器可以和I/O端口打交道,它们各有什么作用?6、8086系统中的物理地址是如何得到的?假如CS=2400H,IP=2l00H,其物理地址是多少?思考题1.从时序的观点分析8088完成一次存储器读操作的过程?2.什么是8088的最大、最小模式?3.在最小模式中,8088如何产生其三总线?4.在最大模式中,为什么要使用总线控制器?思考题1.试述最小模式下读/写总线周期的主要区别。

微机原理课件 第2章 8086系统结构

通 用 寄 存 器

AH AL BH BL CH CL DH DL SP BP DI SI

AX BX CX DX

∑

地址总线 20位 数据总线 8088:8位 8086:16位

段寄存器

指令指针

ALU数据总线(16位)

CS DS SS ES IP 内部暂存器

总线 控 制逻辑

运算寄存器

EU 控 制系统

指令队列 Q总线 (8位) 1 2 3 4 5 6 8088 8086

8086/8088CPU提供的指令,能够直接处理的最大无符号数就是一个字(16 位),如果超出这个范围,就必须使用多字节来表示要计算的数据。 这个原理不光只在8086/8088芯片中有,任何芯片,无论它处理的数据范围多 么大,它总是一个有限的单位,如果超出这个单位,就必须使用标志位作为运算 的中介。 b. 在执行移位指令时, CF标志用于存放移出位的值。 例如对01010011实行逻辑右移,即把这个字节中的每一位向右移动一位,左 边空出的那一位置为0,以前最右边那一位就被移出字节范围外了,那么这一位 就是移出位,移出位都是保存在 CF中的。这个例子中,移位完成后, CF应该 等于1。 c. CF标志位还能够为一些条件转移指令提供判别依据。 例如JC指令,它就是先判别CF标志位的值,如果CF=1,就跳转到指令中给出 地址继续执行程序,如果 CF=0,就不作跳转,CPU会顺序执行下一条指令。也 就是说,在程序中,可以根据CF标志取值的不同来实现程序的分支或循环结构。

OF—溢出标志位,OF溢出的判断方法如下: 加法运算: 若两个加数的最高位为0,而和的最高位为1,则产生溢出; 若两个加数的最高位为1,而和的最高位为0,则产生溢出; 两个加数的最高位不相同时,不可能产生溢出。 减法运算: 若被减数的最高位为0,减数的最高位为1,而差的最高位为1, 则产生溢出; 若被减数的最高位为1,减数的最高位为0,而差的最高位为0, 则产生溢出; 被减数及减数的最高位相同时,按两数的大小判断溢出。 如果所进行的运算是带符号数的运算,则溢出标志恰好能够 反映运算结果是否超出了8位或16位带符号数所能表达的范围, 即字节运算大于十127或小于-128时,字运算大于十32767或小 于-32768时,该位置1,反之为0。

第二章 8086系统

8086/8088微处理器的结构及指令执行的操作 过程 8086/8088微处理器的寄存器组织、存储器组 织、I/O组织、堆栈 8086/8088在最小模式下引脚功能 8086/8088微处理器在最小模式下的典型配置 8086的操作时序

第二章

8086/8088系统结构

2、物理地址和逻辑地址 8086系统中的每个存储单元在1M内存空间中的位 置可以用2个形式的地址来表示。 物理地址(实际地址、绝对地址)和逻辑地址。

物理地址:是用唯一的20位二进制数所表示的地 址,规定了1M字节存储体中某个具体单元的地址 。 CPU与存储器之间进行信息交换都需要提供的地 址,范围00000H—FFFFFH。

BP作基址寻址 SS 一般数据存取 源字符串 目的字符串 DS DS ES

5、8086存储器的分体结构 由于访问存储器的操作类型不同,BIU所使用的逻辑 地址来源也不同。 (1)存储体

15 00001 00003 00005 512KB× 8(位) 奇地址存储体 (A0=1) 512KB× 8(位) 偶地址存储体 (A0=0) 8 7 0 00000 00002 00004

数据DS、ES:存放数据和运算结果; 堆栈段SS:用来传递参数,保存数据和状态信息。

CS IP

0000

代码段

DS或ES

0000

数据段

SI、DI或BX

SS

0000 SP或BP

堆栈段 存储器

段寄存器和偏移地址寄存器组合关系

存储器分段的好处 (1)使指令系统中的大部分指令仅涉及16位偏移 地址,减少了指令长度,提高了程序的执行速度。 (2)为程序在内存中的浮动分配创造了条件。由 于程序可以浮动地装配在内存任何一个区域。这 使得多道程序和多任务程序能充分使用现有的存 储器容量。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

执行下面两个数相加:

1010 0011 0100 1101

+ 0011 0010 0001 1001

1101 0101 0110 0110 分析其结果对下列标志位有何影响: (SF)= 1 1 (ZF)=

(PF)=

(CF)=

0 (AF)= 0 (OF)=

1 0

11

习题 CH2 8086系统结构

数据线和地址线是以 分时复用 方式轮流使用的。

1

习题 CH2 8086系统结构

8086的ALE引脚的作用是

锁存地址

。

8086/8088CPU构成的微机中,每个主存单元对应

两种地址: 逻辑地址 和 物理地址 。 CPU访问存储器时,在地址总线上送出的地址我们 物理 地址。 8086CPU的最小工作模式是 称为

7

习题 CH2 8086系统结构

当M/IO#=0,RD#=0,WR#=1时,CPU完成的

B 。 A. 存储器读 C.存储器写

操作是

B. I/O读

D.I/O写

8088/8086CPU的复位信号至少维持 D 个时钟

周期的高电平有效。 A.1 B.2 C.3 D.4

8

习题 CH2 8086系统结构

3

习题 CH2 8086系统结构

8086系统中,存储器分为奇、偶两个存储体,

其中,奇地址存储体的数据信号线固定与数据总 线的 相连,偶地址存储体数据 高八位 总线的 低八位 相连。 8086CPU从偶地址读出两个字节时,需要 1 个 总线周期;从奇地址读两个字节时,需要 2 个 总线周期。 8086/8088CPU上电复位后,执行第一条指令的 地址是 FFFF0 H。

8086对存储器的管理为什么采用分段的办法?

最大段和最小段的存储空间分别是多大?20位的

物理地址是如何形成的? (略)

8086CPU状态标志位有哪些?说明其符号、名

称和含义(略)

12

4

习题 CH2 8086系统结构

标志判断无符号数运算溢出, 用 OF 标志判断带符号数运算溢出。 8086CPU的PSW寄存器共有 9 个有效的标 志位。 某2K容量的存储器起始地址为12000H,则其末 地址为 127FF H。 一个含有19个字节数据的变量,它的起始逻辑地 址为3000H:0200H,该变量的最后一个字节的 物理地址是 30212 H。

8086CPU可访问的存储器空间为1MB,实际上分为

奇地址存储体和偶地址存储体两部分,奇地址存储 体的片选信号是 B , A. ALE B.BHE# C.A0 D.HOLD 偶地址存储体的选择信号是 B , A. HOLD B. A0 C.BHE# D.HLDA 对于存储体内每一个存储单元的选择信号是 A 。 A. A19 ~A1 B.A18~A1 C. A19 ~ A0 D.A16~ A0

指 系统中只有一个处理器,CPU提供全部的控制信 ,它

是通过将MN/MX#引脚接 高电平或+5V 来实现的。

2

习题 CH2 8086系统结构

对于8086,逻辑地址是由 段基址 和 偏移地址 组

成,设有逻辑地址1000H:2345H,试写出其对应 的物理地址 12345 H 。 段基址是由 段寄存器 存储。物理地址是指实际 的 20 位主存单元地址。 对于8086/8088CPU,设有物理地址00400H,试写 出其两种不同的逻辑地 0000H:0400H 、 。 0040H:0000H 8086系统最多可管理 1M 字节存储单元。

8086用

CF

5

习题 CH2 8086系统结构

8086 CPU中,指令指针(IP)中存放的是 B 。

A.指令

B.指令地址

C.操作数

下面的说法中,

D.操作数地址

B 是正确的。 A.指令周期等于时钟周期 B.指令周期大于时钟周期 C.指令周期是时钟周期的两倍

6

习题 CH2 8086系统结构

9

习题 CH2 8086系统结构

ቤተ መጻሕፍቲ ባይዱ

8086执行指令 MOV AL,[BX],其中BX=2041H

时,BHE#和A0的输出是 B 。 A.0,0 B.0,1 C.1,0 是C 。 A.地址总线 C.控制总线 B.数据总线

D.1,1

计算机系统总线中,可用于传送读、写信号的

D.以上都不对

10

习题 CH2 8086系统结构

习题 CH2 8086系统结构

8086CPU从功能上分为 EU 8086中的BIU中有 4

个

和 BIU 两部分。 16 位的段寄存器、一

个 16 位的指令指针、 6 字节指令队列、 20 位 的地址加法器。

8086 可以访问 8

位和 16 位的寄存器。 8086CPU对外的数据线是 16 根,地址线 20 根,

微机中控制总线提供

D 。 A. 存储器和I/O设备的地址码 B. 所有存储器和I/O设备的时序信号和控制信号 C. 来自I/O设备和存储器的响应信号 D. 上述B、C 现行数据段位于存储器B0000H到B0FFFH字节 单元,则段寄存器DS的内容及该段长度(字节数) 分别为: A 。 A.B000H,1000H B.0000H,0FFFH C.B000H,0FFFH D.B000H,00FFH