实时信号处理系统设计

基于DSP+FPGA的实时信号采集系统设计与实现

基于DSP+FPGA的实时信号采集系统设计与实现周新淳【摘要】为了提高对实时信号采集的准确性和无偏性,提出一种基于DSP+FPGA 的实时信号采集系统设计方案.系统采用4个换能器基阵并联组成信号采集阵列单元,对采集的原始信号通过模拟信号预处理机进行放大滤波处理,采用TMS32010DSP芯片作为信号处理器核心芯片实现实时信号采集和处理,包括信号频谱分析和目标信息模拟,由DSP控制D/A转换器进行数/模转换,通过FPGA实现数据存储,在PC机上实时显示采样数据和DSP处理结果;通过仿真实验进行性能测试,结果表明,该信号采集系统能有效实现实时信号采集和处理,抗干扰能力较强.%In order to improve the accuracy and bias of real-time signal acquisition,a real-time signal acquisition system based on DSP +-FPGA is proposed.The system adopts 4 transducer array to build parallel array signal acquisition unit,the original signal acquisition amplification filtering through analog signal pretreatment,using TMS32010DSP chip as the core of signal processor chip to realize real-time signal acquisition andprocessing,including the signal spectrum analysis and target information simulation,controlled by DSP D/A converter DAC,through the realization of FPGA data storage,real-time display on the PC and DSP sampling data processing results.The performance of the system is tested by simulation.The results show that the signal acquisition system can effectively realize the real-time signal acquisition and processing,the anti-interference ability is strong.【期刊名称】《计算机测量与控制》【年(卷),期】2017(025)008【总页数】4页(P210-213)【关键词】DSP;FPGA;信号采集;系统设计【作者】周新淳【作者单位】宝鸡文理学院物理与光电技术学院,陕西宝鸡721016【正文语种】中文【中图分类】TN911实时信号采集是实现信号处理和数据分析的第一步,通过对信号发生源的实时信号采集,在军事和民用方面都具有广泛的用途。

基于FPGA的实时视频信号处理平台的设计

r eq dr

.

>r c k d

一 . 一

U — 【. 0 Vq7.】 r bd t 【. 0 g —a a 8 . ] yv Sg a 【. u — in I 9 .

t f gf 0 l 8 4

.

r rbsga 【 : _ g—i l8 斫… … n ~

图像 处 理 部 分 内 部 功 能模 块 如 图 2所 示 。

I 墨 卜 塑 丝 . 壅 选 堂 奎 竺 卜 鐾 堡 叫 生卜1 苤 H 皇 矍 l查 I 整

图 2 图像 处 理 部 分 内 部 功 能框 图

F g Di g a o ma e p o e sn a to t r a u c in i .2 a r m fi g r c s i g p r i e n lf n to f n

缚 . 且 数 字 图像 传 感 器 输 出 的 图像 帧 率 也 比较 低 , 辨 率 而 分

也 随 着 半 导 体 行 业 的 发 展 有 了 很 大 的提 高 , 此 为 了输 出 的 因

图 像 能 直 接 在 V A 显 示 器 上 显 示 ,需 要 对 图 像 进 行 帧 率 提 G

【. 0 7.]

w Q RE

CK L 广

R B F F C IO

d a【 0 at 8 】

d t 7 0 a a【 】

.

CKt0 L 0

—

wr re q

>w c k r I

r 呈 b

一 1 ck y v r r q u + d e

wr e q r

RRQ D ̄.

rb g

—

×l _ —

S A R M

—

> ]l wck 7

一种Windows系统中的实时信号处理方法

一种Windows系统中的实时信号处理方法杜亚琦;周建英【摘要】在当前,数字信号处理系统越来越倾向于采用基于FPGA的硬件采集处理设备加CPU主控模块相结合的方法.在Windows操作系统中,如何实时的处理硬件送上来的数据成了一个必须解决的问题.这里介绍了一种应用循环缓存的方法,可以处理通过网络、PCI等接口送上来的数据,并且保证了系统运行的稳定性和实时性.【期刊名称】《电子设计工程》【年(卷),期】2018(026)013【总页数】4页(P33-36)【关键词】Windows操作系统;循环缓存;实时性;多线程【作者】杜亚琦;周建英【作者单位】通信信息控制和安全技术重点实验室浙江嘉兴314033;中国电子科技集团公司第三十六研究所浙江嘉兴314033;中国电子科技集团公司第三十六研究所浙江嘉兴314033【正文语种】中文【中图分类】TN911.3像VxWorks这种实时嵌入式操作系统虽然实时性很好,而且还有并行实时多任务灵活调度等优点,但是这种系统的设计需要专业熟练人员才能设计,对于基础较弱,刚入职的设计师来说,设计好这种系统还是有一定的难度[1-3]。

但是Windows操作系统则不存在这种问题,对于大部分人员来说,即使不是从事程序设计,只要会应用电脑,就对这种操作系统不会陌生,在Windows系统下开发程序对于大部分程序员来说都是相对更容易上手的[4-5]。

这些优点可以降低应用程序以及数字信号处理系统的难度、成本和周期。

而且随着芯片技术的发展,Windows操作系统的CPU处理速度有很大的提高,已经基本能满足大部分数字信号处理系统的需求[6-7]。

但Windows的设计初衷是强调系统的整体性能,其采用的中断处理、内存管理、线程调度等机制存在实时缺陷,不能保证系统行为的确定性和可预测性[7],为了克服这种缺点,这里我们采用了一种类似于硬件的FIFO的循环缓存处理方法,在内存中开辟出一个区域,用于缓存接收到的数据,用两个线程异步地对FIFO进行分别读写,只要缓冲区的大小足够大,数据的写入和读取就可以达到平衡,系统就可以稳定的运行[8-9]。

基于FPGA+DSP的实时图像处理系统设计与实现

万方数据万方数据·110·微处理机2010年(DPRAM)。

虽然C6416片内集成了高达8M位的片内高速缓存,但考虑到图像处理算法必涉及到对前后几帧图像进行处理,为保证系统运行时存储容量不会成为整个系统的性能瓶颈(chokepoint),在DSP模块中额外扩展存储空间。

由于EMIFA口的数据宽度更大,因此系统在EMIFA的CEl空间内扩展了两片总共128M位的同步存储器。

C6416的引导方式有三种,分别是:不加载,CPU直接开始执行地址0处的存储器中的指令;ROM加载,位于EMIFBCEl空间的ROM中的程序首选通过EDMA被搬人地址O处,ROM加载只支持8位的ROM加载;主机加载,外部主机通过主机接口初始化CPU的存储空间,包括片内配置寄存器。

本系统采用的是ROM加载方式。

C6416片内有三个多通道缓冲串口,经DSP处理的最终结果将通过DSP的多通道缓冲串口传送至FPGA。

3.4图像输出模块该模块的功能是将DSP处理后的图像数据进行数模转换,并与字符信号合成后形成VGA格式的视频信号。

这里选用的数模转换芯片为ADV7125。

这是ADI公司生产的一款三通道(每通道8位)视频数模转换器,其最大数据吞吐率330MSPS,输出信图2原始图像图3FPGA图像增强结果5结论实时图像处理系统以DSP和FPGA为基本结构,并在此结构的基础上进行了优化,增加了视频输入通路。

同时所有的数据交换都通过了FPGA,后期的调试过程证明这样做使得调试非常方便,既可以监视数据的交换又方便修正前期设计的错误。

整个系统结构简单,各个模块功能清晰明了。

经后期大量的系统仿真验证:系统稳定性高,处理速度快,能满足设计要求。

号兼容RS一343A/RS一170。

由FPGA产生的数字视频信号分别进入到ADV7125的三个数据通道,经数模转换后输出模拟视频信号并与原来的同步信号、消隐信号叠加后便可以在显示器上显示处理的结果了。

基于DSP和FPGA的视频采集实时处理系统设计

后 经过 图像处 理模 块 进 行 处理 , 处 理 后 的 数据 通 将

作者简介 : 常奇峰 (9 4 ) 男, 18 一 , 河南省周 口市人 , 南京航 空航 天大学硕 士研 究生, 主要研 究方向为数 字图像 处理.

郑 州 轻 工 业 学 院 学 报 (自 然 科 学 版 )

本文 拟 以 T 公 司 的 T 30 6 1 核 心 , I MS2 C 73为 结

合大 规 模 逻 辑 器 件 F G , 及 视 频 采 集 芯 片 PA 以

S A A 7 11 1A设计 实时 f 的视频 采集处 理 系统. 生好

1 系统原理及硬件结构设计

系统原 理框 图如 图 1 所示 .

21 00拄

过双 口送 给 D\ A进行 转换 , 将数 字信 号 转换 为模 拟 信号 , 送往 显示器 显示 .

工作时 , 一块 缓存用 于存放 当前采集 到 的图像数 据, 另一块用 于保存前一 帧数 据, 实现 了高速采集 的数据存储 与读取并行 , 简化 了系统设计 , 提高 了 系统的可靠性.

的效率降低 , 响应 速度 变差. 但是采 用可编程逻辑

器件设计 视 频 采 集 处 理 系统 , 有 开 发 周 期 短 , 具 功 耗 低 , 作频率 高 , 工 编程 配置灵 活等一 系列 优点 .

收 稿 日期 :0 9—1 2 20 2— 6

该系统首先对 由 C D摄像头输出的模拟视频 C

性能实 , 明该系统可以完成常用算法的实时处理. 证

关键 词 : 视频 采 集 ;P A; F G 图像 处理 中 图分 类号 :P 7 . T 242 文 献标 志码 : A

一种基于DSP和FPGA的实时信号处理平台设计

T 1 1是 A I 司推 出的一款 高性能浮点 D P处理器 . s0 D公 S 采用超级 哈佛结构 , 可直接构成 分布式并行 系统 和共享存储式并 行系统, 主要性 能 指 标 如 21 F1 : - 3 () 1内部核时钟频 率可达 30 z 即指令周 期为 33 s 内核 具有 双运算模 块——x和 Y, 条相互 独立 的 18 i内部数 3 2 bt 据 总线 ; () 3支持 81/26 bt /63/4 i 定点和 3 /4 i 26 bt 浮点数据格式 ; ()4 46 位数据线 和 3 位 地址线, 2 可提供4 G的统一寻址空 问; ()4 DMA通道 , 51 个 提供 了处理 核零开销数据传输 ; () 6支持 慢速 设 备和 流水 协议 两种 外设 访 问模式 , 芯片 内部 集成 SR D AM 控 制 器 ; ()通 道全双T链路 V , 74 I单个链路 V最大通信速率 20 ye/, I 5 MB ts 总 s

用到 雷 达 信 号 处 理 系统 中。

[ 关键词 ] 雷达信 号处理

O 引 言 .

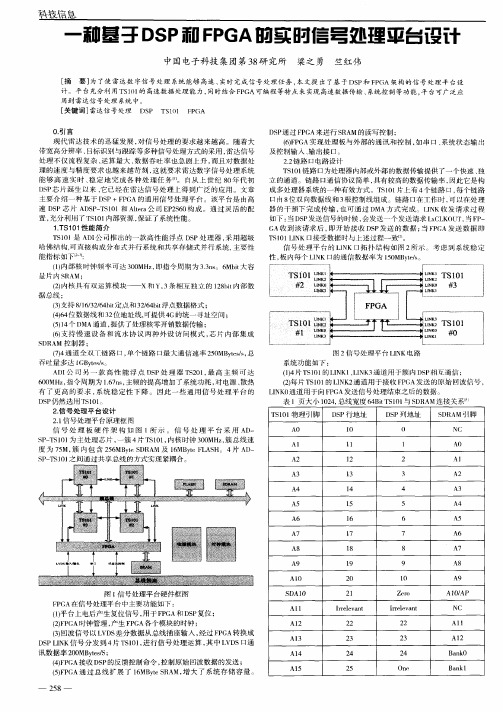

DS T 11 F G P S 0 P A D P通过 F G S P A来进行 S M的读写控制 ; RA ()P 6F GA实现 处理板与外 部的通讯 和控制 , 如串 口 、 系统 状态输 出 及 控 制 输 入 、 出接 口 。 输 22 路 口 电路 设 计 .链

T 1 1物 理 引 脚 D P行 地 址 S0 S

A0

A1

21 .信号处理平 台原理框 图 信 号 处 理 板 硬 件 架 构 如 图 1 示 。信 号 处 理 平 台 采 用 A 所 D— s — s 0 为 主 处 理 芯 片 , 簇 4片 T 1 1 内 核 时 钟 3 0 P T l1 一 S0 , 0 MHz簇 总 线 速 , 度 为 7 M, 内包 含 2 6 yeS AM及 1MB t F A H。4片 A 5 簇 5 MB t DR 6 ye L S D— S — SIl P T 之间通过共享总线 的方式实现 紧耦合 。 O

实时操作系统信号量机制的设计与实现

3 信 号 量 机 制 的 设 计

3 1 线程 创 建 .

来每秒具有 4 G字节的吞 吐率 , 这使超高速数据传

输 成为 可能 。

A S T21 D P— S0 还包含 了一 个新 的通信逻辑单

收稿 日期 :06年 1 20 0月 1 7日, 回 日期 : 0 修 2 6年 1 月 7日 0 1

20 0 7年第 2 期

舰 船 电 子 工 程

9 9

创 建线 程 。每个 线程拥 有 自己 的栈空 间 , 有 自己 并

3 3 信 号量 .

的优先级 。为用户任务 函数创建的线程 , 其优先级 由用 户定 义 。定义 空 闲任 务 (de 的优 先 级 为 25 il) 5 ( 最低 )线程优先级最 高为 0 其 中优 先级处于 0 , , 到l 5之间的线程属于高优先级线程 , 其余 的线程

l 解 码 的增 强 型 指令 ( Vt b 和 T r i s 如 iri e u o解 码 b 器) 这个功能也可 以在非通 信算法 中使用 , , 这使 得系统算法实现的效率和灵活性大大加强 。

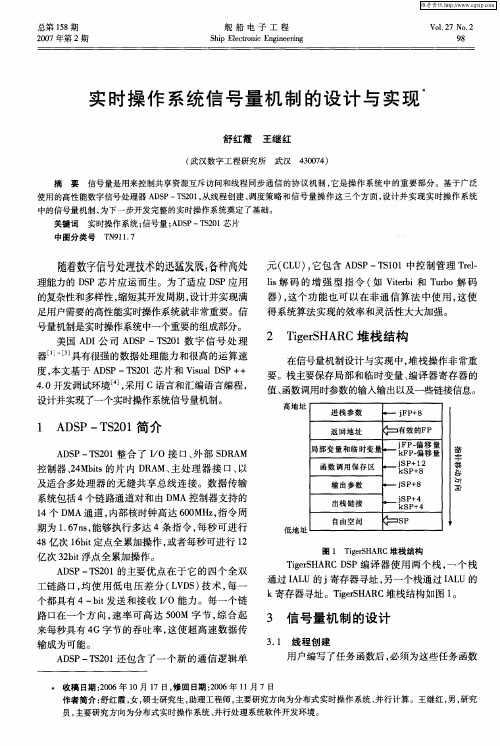

2 TgrH R i S A C堆栈结构 e

在信号量机制设计与实现中, 堆栈操作非常重

的复杂性和多样性 , 缩短其开发周期, 设计并实现满 足用户需要的高性能实时操作系统就非常重要。信 号量机制是实时操作系统中一个重要的组成部分。 美国 A I 司 A S T 2 1 字信 号 处理 D公 D P— S0 数 器¨ 具有很强的数据处理能力和很高的运算速 卜3

度, 本文基于 A S T 21 D P— S0 芯片和 Vsa D P+ i lS + u 40开发调试环境 , . J采用 c语言和汇编语言编程 ,

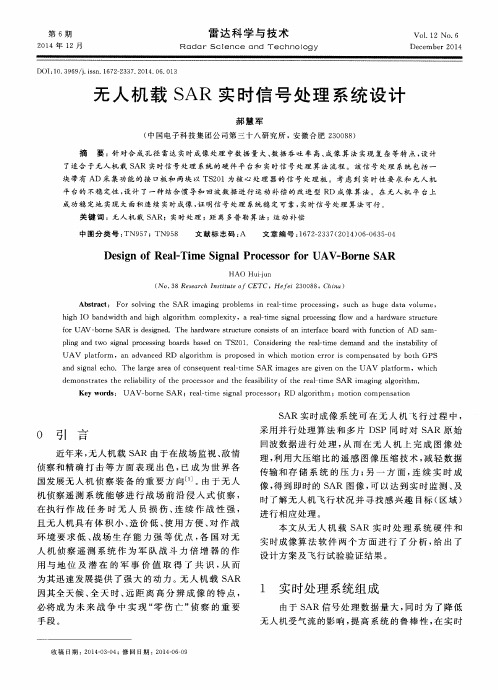

无人机载 SAR 实时信号处理系统设计

a n d s i g n a l e c h o . Th e l a r g e a r e a o f c o n s e q u e n t r e a l — t i me S AR i ma g e s a r e g i v e n o n t h e U AV p l a t f o r m .wh i c h d e mo n s t r a t e s t h e r e l i a b i l i t y o f t h e p r o c e s s o r a n d t h e f e a s i b i l i t y o f t h e r e a l t i me S AR i ma g i n g a l g o r i t h m.

Ke y wor ds : U AV — b o r ne SAR ;r e al — t i me s i gn a l p r o c e s s o r ; RD a l g or i t hm ; m o t i on c o m pe n s a t i on

S AR实 时成 像 系 统 可 在 无 人 机 飞 行 过 程 中 ,

平台的不稳定性 , 设 计 了一 种 结 合 惯 导 和 回波 数 据 进 行 运 动 补 偿 的 改进 型 R D 成 像 算 法 。 在 无 人 机 平 台上

成 功 稳 定 地 实现 大 面积 连 续 实 时 成像 , 证 明信 号 处理 系统 稳 定 可 靠 , 实 时信 号 处理 算 法 可 行 。 关 键词 : 无人机 载 S A R;实 时 处理 ;距 离 多普 勒 算 法 ;运 动 补 偿

h i g h I O b a n d wi d t h a n d h i g h a l g o r i t h m c o mp l e x i t y ,a r e a l — t i me s i g n a l p r o c e s s i n g f l o w a n d a h a r d wa r e s t r u c t u r e

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

课程名称:实时信号处理系统设计论文名称:基于DSP+FPGA的实时视频信号处理设计专业:电子信息工程年级:大四学号:班级:姓名:一、摘要:实时视频信号处理的实时性和跟踪算法的复杂性是一对矛盾,为此采用DSP+ FPGA 的架构设计,同时满足实时性和复杂性的要求,提高了系统的整体性能。

DSP 作为主处理器, 利用其高速的运算能力, 快速有效地处理复杂的跟踪算法; FPGA 作为协处理器, 完成视频图像的接收、存储、预处理, 使设计具有更大的灵活性。

系统采用了形心跟踪和相关跟踪两种算法。

实验证明, 该系统可以稳定地实时跟踪运动目标。

二、引言:实时视频信号处理技术的应用领域十分广泛, 民用领域如机器人视觉、资源探测、天气预报和各种医学图像分析, 军用领域如导弹的精确制导、战场的动态分析等, 都利用了实时视频信号处理技术,这些应用对实时性和识别跟踪精度等都有较高的要求, 因此如何处理实时性和复杂的识别跟踪算法这对矛盾, 是进一步提高系统性能的关键。

本文设计并实现了一种基于DSP+ FPGA的实时数字视频信号处理系统。

DSP 作为主处理器, 处理复杂的跟踪算法; FPGA 作为协处理器, 接收来自COMS 相机的数字视频信号, 控制视频数据缓存SDRAM并进行图像预处理。

整个系统具有很强的处理能力, 很好地解决了实时性和复杂的跟踪算法间的矛盾, 与单独使用DSP 或者FPGA 的系统相比较, 系统性能得到了很大的提高。

三、系统总体设计:采用FPGA+ DSP 的系统结构, 具有处理效率高、开发周期短、支持更高计算处理能力的优点, 是开发难度和系统成本的折衷。

图1 为系统的总体框图。

图1 系统的总体框图系统的主处理器选用TI 公司高性能的定点DSP T MS320C6416。

T MS320C6416是TI 公司推出的高速定点DSP, 时钟频率最高可达1 GHz,其最主要的特点是采用了先进的甚长指令结构( VLIW) , 每个时钟周期可以执行8 条指令, 所有指令都可以条件执行, 完成1 024 点定点FFT 的时间只需10 微妙, 比传统DSP 快1~ 2 个数量级,其高速处理能力优势明显。

FPGA 选用Xilinx 公司的XC3S200AN。

XC3S200AN 是Xilinx 公司Spartan3AN 系列的FPGA, 具有200k 的系统门, 288 kB 的block RAM , 16 个专用乘法器, 4 个DCM, 最大可达195 个用户I/ O 引脚, 高达4 MB 的集成式Flash存储器, 可用于器件配置及系统资源, 省了宝贵的板上空间, 降低了成本。

系统的工作过程是: 图像接收模块接收从CMOS 相机传来的数字图像数据并将其存储到SDRAM( 由SDRAM 控制器控制对SDRAM 的读写) 然后FPGA 读取SDRAM 中的图像数据进行如中值滤波等预处理的工作, 并将结果再次存入SDRAM。

此时, FPGA 的图像接收、SDRAM 控制器控制读写、图像预处理算法等均完成。

随后, DSP 读取SDRAM 中预处理后的数据进行目标跟踪, 得出目标的位置和大小等, 并将结果通过RS232 串口传给下级系统。

2.1 图像接收模块该模块的主要功能是接收CMOS 相机输出的数字图像信号, 包括同步信号和数据信号, 并将这些数字图像信号暂存到输入FIFO 中。

FIFO接收来自相机的图像数据并进行缓冲, 产生符合SDRAM 控制器位宽的数据信号。

FIFO 半满时发出半满信号, 通知SDRAM 控制器读取数字图像数据到SDRAM。

图像接收和存储可以同步进行, 便于实现实时跟踪。

2.2 SDRAM控制器模块由于图像数据流的数据量大、实时性要求高,所以需要高速大容量的存储器作为图像数据缓存。

SDRAM 具有容量大、价格低廉等优点, 成为图像处理中常用的数据存储器。

但是, SDRAM控制较复杂, 需要处理预充、刷新、换行等操作, 因此有必要设计SDRAM 控制器来完成与SDRAM的接口。

在以SDRAM 为缓存的系统中, 使用可编程器件对其进行控制具有很强的灵活性。

本设计采用MICRON 公MT48LC16M16A2,它是单片容量为256 MB 的SDRAM。

图2 是SDRAM 控制器的功能框图。

主要模块的主要功能为:( 1) 模式配置模块: 配置SDRAM 的模式寄存器。

( 2) 刷新模块: 为SDRAM 提供刷新控制以保持内部数据。

( 3) 主状态机: 对各种命令进行译码, 仲裁、控制状态转移。

直接控制SDRAM, 将用户产生的地址命令进行解析, 产生读、写、刷新等一系列操作。

对SDRAM 发出的各种命令要符合特定的时序要求, 在上电时还必须完成对SDRAM 的初始化工作。

( 4) 地址/ 数据选择: 为SDRAM 的读写生成数据路径。

建立用户与SDRAM 的数据通道, 在SDRAM 和用户接口之间传递需要写入或者读出的数据, 并且调整对应读、写操作的DQM 信号时序, 使其满SDRAM 的要求。

缓存从SDRAM中读出的数据, 由于直接读出的速度非常高, 直接处理会对后端产生很大的压力, 因此需要进行缓存之后才送到DSP 进行后续处理。

图2 SDRAM 控制器的功能框图2.3图像处理模块本设计选用TMS320C6416 作为跟踪算法的主处理器。

TMS320C6416 有丰富的L2 RAM 资源( 00000000--000FFFFF) , 系统运行时通过EDMA 方式把程序和数据搬移到内部RAM, 从而实现整个系统程序高速运行, 非常适合实时图像处理。

为了满足系统实时性的要求, 采用PingPong 缓存方案实现图像数据的传输, 对所有的输入和输出数据流使用两组数据缓冲区。

当EDMA 向( 或从) Ping 缓冲区传输数据时, CPU 可以对Pong 缓冲区内的数据进行操作。

当EDMA和CPU 的活动均完成时, 它们之间进行切换,EDMA 向( 或从) Pong 缓冲区传输数据, CPU 对Ping 缓冲区的数据进行操作。

如此循环, 则EDMA 对数据的搬移和CPU 数据的处理可以同时进行, 从而大大提高系统的效率。

使用EDMA 的参数连接可以实现EDMA 传输Ping Pong 缓冲区的自动切换而不需CPU 的干预。

当然, 实现这种切换的前提是在切换到一个缓冲区前CPU己经完成对该缓冲区数据的处理。

在实时图像处理中CPU 处理一帧图像的时间比采集一帧图像的时间要短, 所以这个前提是可以保证的。

为了实时跟踪运动目标, 采用在视频信号的正程处理图像信号和提取跟踪信息, 在视频信号的消隐期间将处理得到的目标位置大小等传给下级系统。

三、系统软件流程系统上电后, TMS320C6416 实现自引导, 从FLASH 拷贝用户程序到内部RAM 之后转入中断等待状态。

FPGA 初始化后接收当前视场中的目标图像数据并将其存储到SDRAM。

FPGA 预处理目标图像数据, 进行如中值滤波等预处理的工作, 处理完之后再次存入SDRAM 并触发中断( 本设计采用EXT INT 4) 给T MS320C6416, 通知DSP 取走数据。

所有的图像数据搬移都可由EDMA在CPU 处理的后台进行TMS320C6416 直接从内部RAM 读取图像数据进行处理。

TMS320C6416 处理完图像数据后, 通过RS232 串口将目标的位置等信息传送给下级系统, 等待下一帧图像的到来。

软件流程图如图3 所示。

图3 软件流程图四、目标跟踪算法视频跟踪有波门跟踪和相关跟踪两种方式。

常用的波门跟踪方法有形心跟踪、边缘跟踪、面积平衡跟踪等。

本文采用形心跟踪和相关跟踪算法。

4.1 形心跟踪算法目标的形心是目标图像上一个确定的点, 当目标姿态变化时, 这个点的位置变动很小, 所以用形心跟踪目标比较平稳, 而且抗干扰能力强。

根据公式(1) 可以得到目标的形心。

f (j ,k) 是图像在(j , k) 点的像元灰度值, 分割后值为1 或0, ( x , y ) 为目标区域的形心。

形心跟踪的应用是在精确分割出目标图像的前提下实现的, 用自适应阈值与区域生长法相结合的方式可以比较精确地分割出目标。

波门的尺寸略大于目标图像, 使波门紧紧套住目标图像, 避免目标受波门外背景和噪声干扰的影响。

波门还可以控制所要处理的图像大小, 仅对感兴趣的局部图像进行实时处理。

因此形心跟踪算法非常适合于实时跟踪运动目标。

4.2 相关跟踪算法相关跟踪又称图像配准法。

相关跟踪通过求取基准图像( 目标模板) 与被测量目标图像相似度来获取目标的相对坐标, 求出目标位置。

将目标图像上各点和目标模板上对应点进行灰度差相加求和, 灰度差的和越小则两图像越相似, 为零时,则表示两图像完全匹配。

设实时图像为S ( x , y ) , 大小为n * m 个像素, 模板图像Q( x , y ) , 大小为u*v 个像素, 其中0 <=u<= n, v <=m。

( k, h) 为模板图像在景物图像中的偏移值。

R( k, h)为相关系数。

(2)相关跟踪无需对图像进行分割和特征提取处理。

在原始图像数据上进行运算, 保留了图像的全部信息。

因此相关跟踪比形心跟踪能够利用更多的目标信息, 这在许多复杂的场景中是一种切实可行的跟踪测量方法。

但是相关跟踪算法的计算量较大, 要求跟踪目标的运动速度不能过快, 否则会因为前一场取得的目标模板在下一场图像中无法匹配到跟踪位置, 导致跟踪失败。

本文提出的硬件设计已经通过实验验证, 满足了系统的性能要求, 可在实际系统中稳定可靠地运行。

实验证明: 在该硬件平台上加载形心跟踪算法, 搜索范围为120*80 时, 跟踪用时0.527ms。

在该硬件平台上加载相关跟踪算法时, 波门大小为100*80, 模板大小为60*48, 跟踪用时5. 5 ms。

处理一场数据需要的时间不到18 ms, 小于CCIR 标准20 ms 的场周期, 完全可以满足实时跟踪的要求。

五、总结:为期半个学期的实时信号处理课就快结束了,通过学习这门课程,让我受益匪浅,学到了很多东西。

在学完后写论文的过程中虽然遇到了很多问题,但通过查资料,请教同学等途径终于将其得以完成。

同时,在写论文的过程中让我感触很深,使我对抽象的理论有了具体的认识。

通过本次论文的设计,使我了解了实时信号处理这门课程在现实生活中的具体应用。

本次设计把理论应用到了实践中,同时通过设计,也加深了自己对理论知识的理解和掌握,在解决困难的过程中,获得了许多专业方面的知识,拓展了视野。

提高了理论水平和实际的动手能力,学会了解决问题的方法,激发了我们的探索精神。

这样的课程设计是很好的锻炼机会,希望老师以后也多安排一些这些方面的论文设计,通过本次论文设计使我深入了解到课程设计在大学学习的重要性,课程设计增强了我们的实践动手能力,也为大四后学期的毕业设计提供了宝贵的经验。