基于DDS技术的简易波形发生器实验报告

基于DDS技术的波形发生器设计与仿真

基于DDS技术的波形发生器设计与仿真【摘要】本文介绍了基于FPGA技术的DDS波形发生器的原理与设计,并利用SignalTapII嵌入式逻辑分析仪对正弦波、三角波、方波、锯齿波进行仿真验证。

实验结果表明,利用FPGA能在很短时间内快速构建任意波形,提高了设计效率,具有实际应用价值。

【关键词】DDS;FPGA;波形发生器1.引言DDS频率合成器具有频率分辨率高[1],输出频点多,可达2N个频点(假设DDS相位累加器的字长是N);频率切换速度快,可达us量级;频率切换时相位连续的优点,可以输出宽带正交信号,其输出相位噪声低,对参考频率源的相位噪声有改善作用;可以产生任意波形;全数字化实现,便于集成,体积小,重量轻[2]。

本文介绍了DDS的基本原理,同时针对DDS波形发生器的FPGA实现进行了简要介绍,利用SignalTapII嵌入式逻辑分析仪对正弦波、三角波、方波、锯齿波进行仿真验证。

2.DDS波形发生器的FPGA实现FPGA的应用[3]不仅使得数字电路系统的设计非常方便,而且它的时钟频率已可达到几百兆赫兹,加上它的灵活性和高可靠性,非常适合用于实现波形发生器的数字电路部分。

使用FPGA设计DDS电路比采用专用DDS芯片更为灵活,只需改变FPGA中的ROM数据,DDS就可以产生任意波形,具有相当大的灵活性。

2.1 FPGA设计流程FPGA的设计框图如图1所示,FPGA的主要功能是:产生与外围电路的接口电路,使其能够接受外围逻辑控制信号;保存频率字,并构成相位累加器,产生与主时钟相同频率的RAM寻址字;用内部的存储块构成存放多种波形数据的ROM,并通过相应的控制线进行选择;构造出两个多波形选择输出的输出通道,其中的一路通道可具备移相功能;用内部的PLL倍频外部低频晶振,并输出与主时钟同频的时钟,驱动片外高速D/A。

2.2 时钟模块根据耐奎斯特采样定理要得到输出频率为10MHz的信号,其所输入的信号时钟频率必须达20MHz以上。

DDS信号发生器实验报告含原理图PCB和代码

电子信息技术综合实训报告格式竞赛题名称:《DDS信号发生器的设计》队员名称:评阅人签名:2012年9月15日1、设计思路描述:本设计是一个以AT89C51单片机为核心基于DAC0832芯片的DDS信号发生器。

信号发生器采用数字波形合成技术,通过硬件电路和软件程序相结合,可输出正弦波和三角波,波形的转换可通过软件控制。

本设计通过按键选择波形,经过AT89C51单片机将数据输出到DAC0832,由数字信号转变为模拟信号,再通过运放器稳定地输出到示波器上。

原理框图如下:2、硬件电路图:DAC0832是采样频率为八位的D/A转换器件,芯片内有两级输入寄存器,使DAC0832具备双缓冲、单缓冲和直通三种输入方式,以便适于各种电路的需要(如要求多路D/A异步输入、同步转换等)。

D/A转换结果采用电流形式输出。

要是需要相应的模拟信号,可通过一个高输入阻抗的线性运算放大器实现这个供功能。

运放的反馈电阻可通过RFB端引用片内固有电阻,还可以外接。

该片逻辑输入满足TTL电压电平范围,可直接与TTL电路或微机电路相接。

下面是DAC0832引脚图和内部结构电路图DAC0832引脚功能说明:DI0~DI7:数据输入线,TLL电平。

ILE:数据锁存允许控制信号输入线,高电平有效。

CS:片选信号输入线,低电平有效。

WR1:为输入寄存器的写选通信号。

XFER:数据传送控制信号输入线,低电平有效。

WR2:为DAC寄存器写选通输入线。

Iout1:电流输出线。

当输入全为1时Iout1最大。

Iout2: 电流输出线。

其值与Iout1之和为一常数。

Rfb:反馈信号输入线,芯片内部有反馈电阻。

Vcc:电源输入线 (+5v~+15v)Vref:基准电压输入线 (-10v~+10v)AGND:模拟地,摸拟信号和基准电源的参考地。

DGND:数字地,两种地线在基准电源处共地比较好。

主控电路及数模转换电路分别如下:主控电路数模转换电路3软件流程图:4测试方法描述:运用proteus软件设计好电路图,将程序代码编译好以后载入proteus中的AT89C51芯片进行仿真。

基于DDS的任意波形信号发生器的开题报告

基于DDS的任意波形信号发生器的开题报告一、题目基于DDS的任意波形信号发生器二、选题背景任意波形发生器作为一种测试仪器,广泛应用于电子、通讯、航空航天、军工等领域。

目前市场上的任意波形发生器存在着各种局限性,例如波形生成精度不高、输出频率范围小、信号失真等问题。

而采用直接数字合成(DDS)技术的任意波形发生器可以解决这些问题。

DDS技术是一种基于数字信号处理的技术,能够直接在数字域中实现信号的合成和处理。

DDS技术的主要特点是输出频率范围广、频率分辨率高,信号稳定度好,价格相对较低。

因此,基于DDS技术的任意波形发生器具有较高的可靠性、精度和稳定性,是一种理想的波形发生器。

三、研究内容该课题的研究内容主要包括以下几个方面:1. DDS技术原理及算法。

2. 硬件设计:包括DDS芯片的选型、时钟电路、滤波电路、输出端口等电路的设计。

3. 软件设计:包括DDS控制算法、波形生成算法、用户操作界面等软件的设计。

4. 系统整合:将硬件和软件进行系统集成,并进一步进行测试和完善。

四、研究意义通过研发基于DDS技术的任意波形发生器,可以实现信号生成的高精度、高稳定性、高可靠性、高灵活性和高扩展性,可以在测试仪器、通信设备、导航、医疗和科研等领域中得到广泛应用。

五、拟解决的关键问题1. DDS芯片的选型和相关电路设计,以保证波形发生器的稳定性和精度。

2. 波形的生成和输出电路的设计,以保证波形的准确性和稳定性。

3. 软件的设计和开发,包括DDS控制算法、波形生成算法、用户操作界面等等,以实现任意波形的快速、精确生成。

六、研究方法1. 文献调研:查阅相关学术资料、专利文献,了解DDS技术的原理和应用。

2. 硬件设计:根据选型要求和设计需求,设计和验证相应的电路方案。

3. 软件设计:根据硬件设计需求和用户需求,设计和开发相应的软件方案。

4. 系统整合:将硬件和软件进行系统集成,并进行测试和完善。

七、可行性分析基于DDS技术的任意波形发生器已经有了相应的理论基础和技术支持,并且在工业界和科研领域已经得到了广泛的应用和验证。

基于DDS技术的任意波形发生器设计

计算机应用基于DDS 技术的任意波形发生器设计浙江大学(杭州310027) 刘成尧 王小海 祁才君 王文华 摘 要 文章介绍了基于DDS 技术的任意波形发生器的设计。

详细讨论了CPLD 器件在DDS 技术实现中的具体应用。

该任意波形发生器具有输出频率稳定、准确,波形质量好和输出频率范围宽等优点。

关键词 直接数字频率合成 CPLD 任意波形发生器1 概述基于DDS 技术的任意波形发生器(AW G )利用高速存储器作为查找表,通过高速D/A 转换器对存储器的波形进行合成[1]。

它不仅可以产生正弦波、方波、三角波和锯齿波等规则波形,而且还可以通过上位机(或下位机)编辑,产生真正意义上的任意波形。

例如,它能模拟编码雷达信号、潜水艇特征信号、磁盘数据信号、机械振动瞬变过程、电视信号以及神经脉冲之类的波形,也能重演由数字示波器(DSO )捕获的波形。

DDS 技术的实现依赖于高速、高性能的数字器件。

可编程逻辑(CPLD )器件以其速度高、规模大、可编程,以及有强大EDA 软件支持等特性,十分适合实现DDS 技术。

本文中即将讨论的是EPF6016A 器件在DDS 技术实现任意波形发生器中的具体应用。

2 DDS 实现任意波形发生器的原理DDS 技术建立在采样定理的基础上,它首先对需要产生的波形进行采样,将采样值数字化后存入存储器作为查找表,然后再通过查表将数据读出,经过D/A 转换器转换成模拟量,把存入的波形重新合成出来。

DDS 原理如图1所示。

图1 DDS 的原理框图 利用上位机生成所需波形的数据,然后通过单片机将生成的数据写入波形存储器(RAM )中,再由DDS 系统将波形合成出来,这样就可以产生出所需的任意波形。

DDS 系统任意波产生的原理图如图2所示。

图2 DDS 系统任意波形的产生3 CPLD 在DDS 技术实现中的应用FL EX6016芯片的主要结构包括132个逻辑阵列块(logic array block )、快速通道(fast track )和I/O单元[2]。

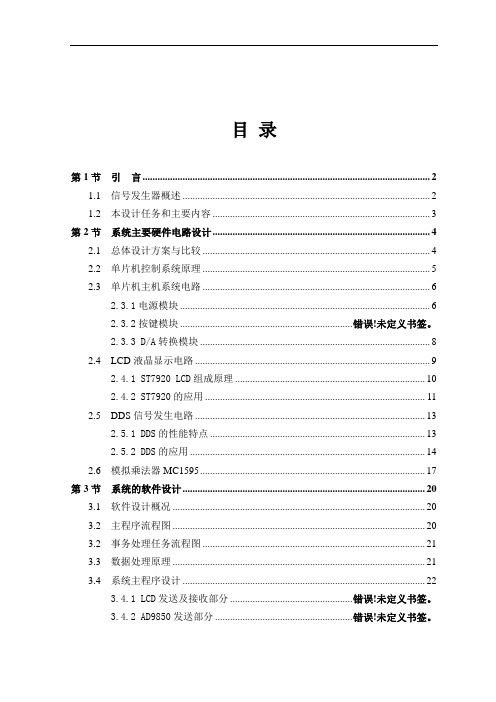

DDS信号发生器报告

目录第1节引言 (2)1.1 信号发生器概述 (2)1.2 本设计任务和主要内容 (2)第2节系统主要硬件电路设计 (3)2.1 总体设计方案与比较 (3)2.2 单片机控制系统原理 (4)2.3 单片机主机系统电路 (5)2.3.1电源模块 (5)2.3.2按键模块 .................................................................. 错误!未定义书签。

2.3.3 D/A转换模块 (7)2.4 LCD液晶显示电路 (8)2.4.1 ST7920 LCD组成原理 (9)2.4.2 ST7920的应用 (10)2.5 DDS信号发生电路 (12)2.5.1 DDS的性能特点 (12)2.5.2 DDS的应用 (13)2.6 模拟乘法器MC1595 (16)第3节系统的软件设计 (19)3.1 软件设计概况 (19)3.2 主程序流程图 (19)3.2 事务处理任务流程图 (20)3.3 数据处理原理 (20)3.4 系统主程序设计 (21)3.4.1 LCD发送及接收部分 .............................................. 错误!未定义书签。

3.4.2 AD9850发送部分 .................................................... 错误!未定义书签。

3.4.3 D/A5615发送部分 .................................................. 错误!未定义书签。

第4节结束语 .. (26)参考文献 (27)基于DDS技术的信号发生器第1节引言信号发生器又称信号源或振荡器,在生产实践和科技领域中有着广泛的信号发生器又称信号源或振荡器,在生产实践和科技领域中有着广泛的应用。

本设计分五个模块:单片机控制及显示模块、数模(D/A)转换模块、波形产生模块、输出显示模块、电源模块。

基于DDS技术的任意波形发生器研究与设计

1 DDS概述1.1 DDS基本原理直接数字合成技术(Direet Digital Synthesis,简称DDS)是建立在采样定理基础上,首先对需要产生的波形进行采样,将采样值数字化后存入存储器作为查找表,然后通过查表读取数据,再经D/A转换器转换为模拟量,将保存的波形重新合成出来。

DDS基本原理框图如图1所示。

由图l看出,除了滤波器(LPF)之外,DDS系统都是以数字集成电路实现,因此DDS系统易于集成和小型化。

DDS系统的参考时钟源通常是一个具有高稳定性的晶体振荡器,整个系统的各个组成部分提供同步时钟。

频率字(FSW)实际上是相位增量值(二进制编码),作为相位累加器的累加值。

相位累加器在每一个参考时钟脉冲输入时,累加一次频率字,其输出相应增加一个步长的相位增量。

由于相位累加器的输出连接在波形存储器(ROM)的地址线上,因此其输出的改变就相当于查表。

这样就可把存储在波形存储器内的波形抽样值(二进制编码)经查找表查出。

ROM的输出送到D/A转换器,经D/A转换器转换成模拟量输出。

1.2 DDS的基本参数及其计算在系统时钟脉冲的作用下,相位累加器不停累加,即不停查表,把波形数据送到D/A 转换器转换成模拟量输出,从而合成波形。

滤波器则进一步平滑D/A转换器输出的近似正弦波的锯齿阶梯波,同时衰减不必要的杂散信号。

设频率字(FSW)的值为d,系统时钟频率为f,相位累加器的字长为N,则系统的输出频率为:2 任意波形发生器的设计方案基于DDS技术的任意波形发生器主要由微处理器控制模块、键盘与显示模块、DDS通道的FPGA实现模块、D/A转换模块以及滤波器模块组成。

同时片外扩展了4 KB程序存储器SRAM和6 KB数据存储器ROM,分别用于存储波形抽样数据和3种标准输出波形抽样数据。

本系统设计原理如图2所示。

2.1 微处理器控制模块采用AT89C5l单片机完成数据处理和控制其他电路工作。

将键盘接收的数据通过特定算法转换成二进制码,再将处理后的控制字、波形参数和其他器件的控制信号发送出去。

12DDS波形发生器

三角波

方波

锯齿波

LOGO

四、实验步骤及内容

4 频率以及幅度的控制和显示

通过键盘由单片机控制改变前级D/A的输出幅度实现幅度调 节并通过LCD显示当前输出信号的幅度,同样通过键盘由 单片机控制频率控制字的改变通过LCD显示当前输出信号 的频率实现对幅度和频率的控制以及显示。

四、实验步骤及内容

系统整 体框图

DDS信号源

一、实验目的

1 了解直接数字频率合成技术(DDS)的原理。

2 学会使用单片机和CPLD产生不同频率、不同幅度 的正弦波、方波与三角波。

二、实验原理

系统以单片机作为核心控制模块,向双口RAM 写入波形数据,并控制前级D/A的输出电压幅度, 前级D/A提供后级D/A的基准电压,从而间接控制输 出波形的幅度。

四、实验步骤及内容

2 幅度控制的实现

幅度控制部分采用双D/A技术,由单片机控制,第一级D/A 的输出波形作为第二级D/A的基准电压源,以此来控制信号 发生器的输出电压幅度。

3 后级滤波的实现

采用二阶巴特沃兹滤波器。巴特沃兹滤波器的幅度函数是单 调下降的,但巴特沃兹滤波器能实现最大平坦幅度滤波。由 于信号发生器的输出波形中的主要噪声为D/A转换产生的高频 分量,与设计的频率范围相差很远,所以相对来说,滤波器 在频带内的平坦程度比其衰减陡度更为重要。

fout

fclk 2N

*M

f

f clk 2N

通过改变频率 控制字M实现 对输出信号频 率的调节

三、实验器材

单片机89C51,CPLD DAC0800,DAC0832,IDT7312

键盘,液晶显示屏

实验器材

四、实验步骤及内容

1 直接数字频率合成(DDS)的实现

简易DDS波形发生器设计

实验二简易DDS波形发生器设计084775116 马丽丽084775117 潘奕颖一、实验目的:进一步熟悉绘制ASM图分析实验的方法;进一步掌握将VHDL程序符号化的使用方法;熟悉ROM表的制作与符号化;了解DDS波形发生器的基本原理。

二、实验内容:利用FPGA和DAC,设计一个简易的DDS波形发生器并发出正弦波。

三、设计要求:1.分辨率优于1Hz;2.ROM表长度8位,位宽10位;3.输出频率优于100kHz(每个周期数据点大于50);4.显示信号频率/频率控制字(可切换);5.直接输入频率控制字或输出频率。

四、实验仪器:计算机1台;QUARTUS II软件一套;试验箱1台。

五、方法步骤:1.绘制ASM图;阅读实验要求,分析实验过程,然后绘制ASM图如下页:2. 建立一个工程;打开QUARTUS II 软件,Files → New Project Wizard → 选择储存路径→ next → next → 选择芯片Cyclone II EP2C5T144C8 → next → finish 。

3. 编写累加器的VHDL 文件,并将其转换成图形文件;①Files → New → VHDL File → 开始编写程序; ②经过编写后,进行编译(Tools → Compiler Tool →Strart),改错,再编译,改错直至编译成功,保 存文件名为“dds1.vhd ”;程序如下:library ieee;library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity dds1 isport(m:in std_logic_vector(19 downto 0);cp,r:in std_logic;q:out std_logic_vector(7 downto 0));end dds1;architecture z of dds1 issignal t:std_logic_vector(22 downto 0);signal n:std_logic_vector(22 downto 0);beginprocess(cp)beginn<="000"&m;if cp'event and cp='1' thenif r='1' thent<="00000000000000000000000";elsif t+n>8388607 thent<="00000000000000000000000";elset<=t+n;end if;end if;q<=t(22 downto 15);end process;end z;③编译通过以后,File → Create/Update → Create Symbol Files For Current File。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2012-9-25 21:43:25

-3-

252,253,253,253,253,254,254,254,254,254,255,255,255,255,255, 255,255,255,255,255,255,255,255,255,254,254,254,254,254,253, 253,253,253,252,252,251,251,251,250,250,249,249,248,248,247, 247,246,246,245,244,244,243,242,242,241,240,239,239,238,237, 236,235,234,234,233,232,231,230,229,228,227,226,225,224,223, 222,221,219,218,217,216,215,214,213,211,210,209,208,206,205, 204,203,201,200,199,197,196,195,193,192,190,189,188,186,185, 183,182,180,179,177,176,175,173,172,170,168,167,165,164,162, 161,159,158,156,155,153,151,150,148,147,145,144,142,140,139, 137,136,134,132,131,129,128};

#define uchar unsigned char #define uint8 unsigned char

2012-9-25 21:43:25

-2-

#define uint16 unsigned int

sbit LED1=P1^1; sbit LED2=P1^2; sbit LED3=P1^3; sbit LED4=P1^4;

500 个点.把定时间隔设为 0.05ms,每中断一次输出一个点.经过计算,如果步长为 1,则可以得到最低频率 40HZ,如果将步长调整为 25 的话则可以得到 1KHZ 的频 率.这样,频率变化的步长就是 40HZ.

显示仍采用循环动态显示的方法.扫描的时间间隔设为 4ms 经过实验,证明这 样的间隔可以得到很好的效果.人眼感觉不到这种动态效果.

简易波形发生器实验报告

一、实验目的

1、了解电子系统的设计方法。 2、通过实验,熟悉和掌握 AT89S52 单片机的外围电路。 3、掌握单片机和数码管、键盘的接口电路和数码管的驱动方式。 4、掌握数模转换器 DAC0800 的原理、使用方法以及和单片机的接口。 5、掌握 DDFS(直接数字频率合成)的原理和其在单片机内的实现方法。 6、学会用 EDA 软件(Protel99se 或 ORCAD)进行电路原理图和 PCB 图 的绘制。

运算放大器 OP07

1

电位器 5k

1

按键

3

发光二极管

3

晶振 24M

1

八位排阻 510 欧 1

电阻 1k/10k

1/2

510 欧电阻

3

电解电容 22uF 1 电解电容 10uF 3 瓷片电容 30pF 2 瓷片电容 0.1uF 15

1000Pf

1

5.1k 电阻

4

四、实验完成具体情况

1)程序设计简单思路: 为实现波形输出,我们采用的无疑也是 DFS.正弦波和三角波我们都是取了

uchar code tri[]={250,249,248,247,246,245,244,243,242,241,240,239, 238,237,236,235,234,233,232,231,230,229,228,227,226,225,224,223,

222,221,220,219,218,217,216,215,214,213,212,211,210,209,208, 207,206,205,204,203,202,201,200,199,198,197,196,195,194,193, 192,191,190,189,188,187,186,185,184,183,182,181,180,179,178, 177,176,175,174,173,172,171,170,169,168,167,166,165,164,163, 162,161,160,159,158,157,156,155,154,153,152,151,150,149,148, 147,146,145,144,143,142,141,140,139,138,137,136,135,134,133, 132,131,130,129,128,127,126,125,124,123,122,121,120,119,118, 117,116,115,114,113,112,111,110,109,108,107,106,105,104,103, 102,101,100,99,98,97,96,95,94,93,92,91,90,89,88, 87,86,85,84,83,82,81,80,79,78,77,76,75,74,73, 72,71,70,69,68,67,66,65,64,63,62,61,60,59,58, 57,56,55,54,53,52,51,50,49,48,47,46,45,44,43, 42,41,40,39,38,37,36,35,34,33,32,31,30,29,28 , 27,26,25,24,23,22,21,20,19,18,17,16,15,14,13, 12,11,10,9,8,7,6,5,4,3,2,1,0, 1, 2, 3,4,5,6,7,8,9,10,11,12,13,14,15,16, 17,18,19,20,21,22,23,24,25,26,27,28,29,30,31, 32,33,34,35,36,37,38,39,40,41,42,43,44,45,46, 47,48,49,50,51,52,53,54,55,56,57,58,59,60,61, 62,63,64,65,66,67,68,69,70,71,72,73,74,75,76, 77,78,79,80,81,82,83,84,85,86,87,88,89,90,91, 92,93,94,95,96,97,98,99,100,101,102,103,104,105,106, 107,108,109,110,111,112,113,114,115,116,117,118,119,120,121, 122,123,124,125,126,127,128,129,130,131,132,133,134,135,136, 137,138,139,140,141,142,143,144,145,146,147,148,149,150,151, 152,153,154,155,156,157,158,159,160,161,162,163,164,165,166, 167,168,169,170,171,172,173,174,175,176,177,178,179,180,181, 182,183,184,185,186,187,188,189,190,191,192,193,194,195,196, 197,198,199,200,201,202,203,204,205,206,207,208,209,210,211, 212,213,214,215,216,217,218,219,220,221,222,223,224,225,226, 227,228,229,230,231,232,233,234,235,236,237,238,239,240,24;//键盘 sbit key2=P1^6; sbit key3=P1^7;

uint8 step=1;//步进,随频率变化 uint16 temp=0;//相位 uchar aaa=0;//波的种类 uint16 fre;//波的频率

#define sendwave P2//波形送出口 #define display P0//显示内容输出端口 #define sltld P1//选通 LED 所用变量

uchar code sin[]={127,126,124,123,121,119,118,116,115,113,111,110,108, 107,105,104,102,100,99,97,96, 94, 93,91, 90, 88, 87, 85,

83, 82, 80, 79, 78, 76, 75, 73, 72, 70, 69, 67, 66, 65, 63, 62, 60, 59, 58, 56, 55, 54, 52, 51, 50, 49, 47, 46, 45, 44, 42, 41, 40, 39, 38, 37, 36, 34, 33, 32, 31, 30, 29, 28, 27, 26, 25, 24, 23, 22, 21, 21, 20, 19, 18, 17, 16, 16, 15, 14, 13, 13, 12, 11, 11, 10, 9, 9, 8, 8, 7, 7, 6, 6, 5, 5, 4, 4, 4, 3, 3, 2, 2, 2, 2, 1, 1, 1, 1, 1, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 1, 1, 1, 1, 1, 2, 2, 2, 2, 3, 3, 3, 4, 4, 5, 5, 5, 6, 6, 7, 7, 8, 9, 9, 10, 10, 11, 12, 12, 13, 14, 15, 15, 16, 17, 18, 18, 19, 20, 21, 22, 23, 24, 25, 26, 27, 28, 29, 30, 31, 32, 33, 34, 35, 36, 37, 38, 39, 41, 42, 43, 44, 45, 47, 48, 49, 50, 52, 53, 54, 56, 57, 58, 60, 61, 62, 64, 65, 67, 68, 70, 71, 72, 74, 75, 77, 78, 80, 81, 83, 84, 86, 87, 89, 90, 92, 93, 95, 97, 98, 100,101,103,104,106,108 , 109 ,111,112,114,115,117,119,121,122,123,125,127,128,130,132 , 133,135,136,138,140,141,143,144,146,147,149,151,152,154,155, 157,158,160,162,163,165,166,168,169,171,172,174,175,177,178, 180,181,183,184,185,187,188,190,191,193,194,195,197,198,199, 201,202,203,205,206,207,208,210,211,212,213,214,216,217,218, 219,220,221,222,223,224,225,226,227,228,229,230,231,232,233, 234,235,236,237,237,238,239,240,240,241,242,243,243,244,245, 245,246,246,247,248,248,249,249,250,250,250,251,251,252,252,