二进制码转换为十进制(BCD)码

BCD码

BCD码(Binary-Coded Decimal)亦称二进码十进数或二-十进制代码。

用4位二进制数来表示1位十进制数中的0~9这10个数码。

是一种二进制的数字编码形式,用二进制编码的十进制代码。

BCD码这种编码形式利用了四个位元来储存一个十进制的数码,使二进制和十进制之间的转换得以快捷的进行。

这种编码技巧最常用于会计系统的设计里,因为会计制度经常需要对很长的数字串作准确的计算。

相对于一般的浮点式记数法,采用BCD码,既可保存数值的精确度,又可免却使电脑作浮点运算时所耗费的时间。

此外,对于其他需要高精确度的计算,BCD编码亦很常用。

即BCD代码。

Binary-Coded Decimal?,简称BCD,称BCD码或二-十进制代码,亦称二进码十进数。

是一种二进制的数字编码形式,用二进制编码的十进制代码。

这种编码形式利用了四个位元来储存一个十进制的数码,使二进制和十进制之间的转换得以快捷的进行。

这种编码技巧,最常用于会计系统的设计里,因为会计制度经常需要对很长的数字串作准确的计算。

相对于一般的浮点式记数法,采用BCD码,既可保存数值的精确度,又可免却使电脑作浮点运算时所耗费的时间。

此外,对于其他需要高精确度的计算,BCD编码亦很常用。

由于十进制数共有0、1、2、……、9十个数码,因此,至少需要4位二进制码来表示1位十进制数。

4位二进制码共有2^4=16种码组,在这16种代码中,可以任选10种来表示10个十进制数码,共有N=16!/(16-10)!约等于2.9乘以10的10次方种方案。

常用的BCD代码列于末。

常用BCD编码方式最常用的BCD编码,就是使用"0"至"9"这十个数值的二进码来表示。

这种编码方式,在中国大陆称之为“8421码”。

除此以外,对应不同需求,各人亦开发了不同的编码方法,以适应不同的需求。

这些编码,大致可以分成有权码和无权码两种:有权BCD码,如:8421(最常用)、2421、5421…无权BCD码,如:余3码、格雷码…以下为三种常见的BCD编码的比较。

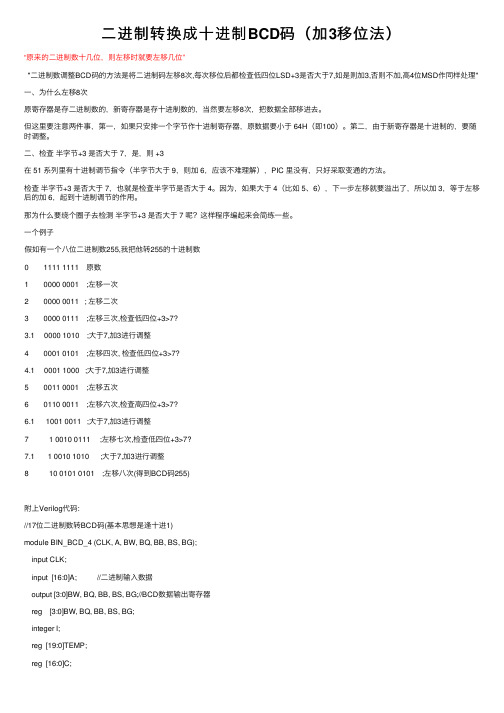

二进制转换成十进制BCD码(加3移位法)

⼆进制转换成⼗进制BCD码(加3移位法)“原来的⼆进制数⼗⼏位,则左移时就要左移⼏位”"⼆进制数调整BCD码的⽅法是将⼆进制码左移8次,每次移位后都检查低四位LSD+3是否⼤于7,如是则加3,否则不加,⾼4位MSD作同样处理"⼀、为什么左移8次原寄存器是存⼆进制数的,新寄存器是存⼗进制数的,当然要左移8次,把数据全部移进去。

但这⾥要注意两件事,第⼀,如果只安排⼀个字节作⼗进制寄存器,原数据要⼩于 64H(即100)。

第⼆,由于新寄存器是⼗进制的,要随时调整。

⼆、检查半字节+3 是否⼤于 7,是,则 +3在 51 系列⾥有⼗进制调节指令(半字节⼤于 9,则加 6,应该不难理解),PIC ⾥没有,只好采取变通的⽅法。

检查半字节+3 是否⼤于 7,也就是检查半字节是否⼤于 4。

因为,如果⼤于 4(⽐如 5、6),下⼀步左移就要溢出了,所以加 3,等于左移后的加 6,起到⼗进制调节的作⽤。

那为什么要绕个圈⼦去检测半字节+3 是否⼤于 7 呢?这样程序编起来会简练⼀些。

⼀个例⼦假如有⼀个⼋位⼆进制数255,我把他转255的⼗进制数0 1111 1111 原数1 0000 0001 ;左移⼀次2 0000 0011 ; 左移⼆次3 0000 0111 ;左移三次,检查低四位+3>7?3.1 0000 1010 ;⼤于7,加3进⾏调整4 0001 0101 ;左移四次, 检查低四位+3>7?4.1 0001 1000 ;⼤于7,加3进⾏调整5 0011 0001 ;左移五次6 0110 0011 ;左移六次,检查⾼四位+3>7?6.1 1001 0011 ;⼤于7,加3进⾏调整7 1 0010 0111 ;左移七次,检查低四位+3>7?7.1 1 0010 1010 ;⼤于7,加3进⾏调整8 10 0101 0101 ;左移⼋次(得到BCD码255)附上Verilog代码://17位⼆进制数转BCD码(基本思想是逢⼗进1)module BIN_BCD_4 (CLK, A, BW, BQ, BB, BS, BG);input CLK;input [16:0]A; //⼆进制输⼊数据output [3:0]BW, BQ, BB, BS, BG;//BCD数据输出寄存器reg [3:0]BW, BQ, BB, BS, BG;integer I;reg [19:0]TEMP;reg [16:0]C;always @ (posedge CLK)beginC=A;TEMP=0;for (I=1; I<17; I=I+1)begin{TEMP, C}={TEMP[18:0], C, 1'b0};//左移⼀位 if (TEMP[3:0]>4'b0100)beginTEMP[3:0]=TEMP[3:0]+3; // >4则加3endif (TEMP[7:4]>4'b0100)beginTEMP[7:4]=TEMP[7:4]+3;endif (TEMP[11:8]>4'b0100)beginTEMP[11:8]=TEMP[11:8]+3;endif (TEMP[15:12]>4'b0100)beginTEMP[15:12]=TEMP[15:12]+3;endif (TEMP[19:16]>4'b0100)beginTEMP[19:16]=TEMP[19:16]+3;end{BW, BQ, BB, BS, BG}={TEMP[18:0], A[0]}; endendendmodule。

二进制码转BCD码原理

⼆进制码转BCD码原理有时候没有采⽤BCD计数器,⼜需要⽤⼗进制形式显⽰⼆进制数据,最常⽤的⽅法是编码转换:将⼆进制码转换成BCD码(8421)。

8421码:8421码⼜称⼗进制码,它只选⽤了四位⼆进制码中前10组代码,4个码表达10个数,即⽤0000~1001分别代表它所对应的⼗进制数,余下的六组代码不⽤。

如果要我将⼆进制码转成BCD码,我会看看他们何时分道扬镳,以此观察⼆者的区别。

对于BCD计数器,当计数到1001时,下⼀次计数要进位,得到0001_0000。

对于⼆进制计数器,下⼀次计数得到的是1010。

不可能重新计⼀次数来得到BCD码,太浪费时间了,但是直接让我转我也束⼿⽆策。

我们很快发现按位重建的话,消耗的时钟周期数是⼆进制位数,还可以接受。

深⼊思考⼀下,发现是可⾏的。

就像标准LSB乘法⼀样,从⼆进制⾼位开始重建,⽤⼀个寄存器每个周期进⾏shift-add操作。

如果不⼲其他的,花费n个周期即可重建出n-bit⼆进制数。

这个⼯作量已经是⼀个⽐特串⾏乘法器了,结果肯定是原来的⼆进制数不会错。

每4个bit分为⼀组BCD码,对于任意⼀组在任意⼀个周期状态下,只要数据≥5,那么下⼀次移位就会超出BCD码范围,对于BCD 计数器来说需要进位。

为使4位⼆进制码进位,要满⾜逢16进⼀。

由于BCD码是逢10进⼀,直接给当前组4bit数据补上差距3即可。

下⼀次移位的时候,差距扩⼤为6,如果BCD码应该进位,那么⼆进制码也会进位,同步进位,⽬的达成。

寄存器中的编码已经是BCD码了,但是这个BCD码代表的值和⼆进制代表的值是⼀样的。

⼆进制重建可以进⾏shift-add操作,BCD码重建同样可以进⾏shift-add操作,只不过BCD码有⾃⼰的规则,在shift-add的时候要进⾏⼀点修正罢了。

在任意周期,重建出来的⼆进制码和BCD码表⽰的值都是⼀样的。

所以最终重建出来的BCD码是正确的。

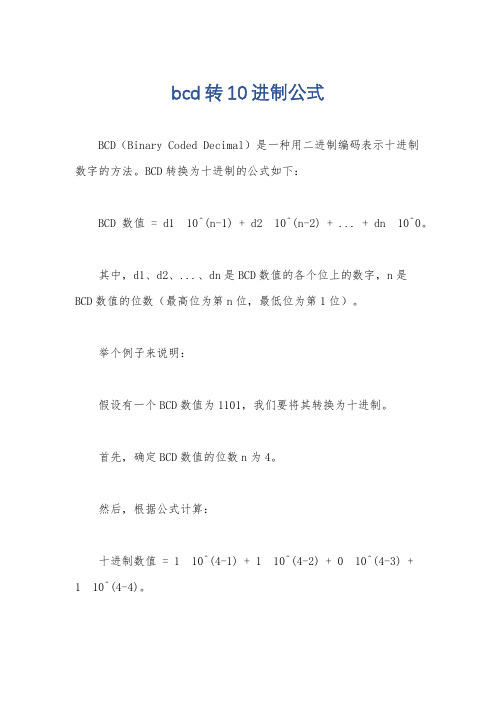

bcd转10进制公式

bcd转10进制公式

BCD(Binary Coded Decimal)是一种用二进制编码表示十进制

数字的方法。

BCD转换为十进制的公式如下:

BCD数值 = d1 10^(n-1) + d2 10^(n-2) + ... + dn 10^0。

其中,d1、d2、...、dn是BCD数值的各个位上的数字,n是BCD数值的位数(最高位为第n位,最低位为第1位)。

举个例子来说明:

假设有一个BCD数值为1101,我们要将其转换为十进制。

首先,确定BCD数值的位数n为4。

然后,根据公式计算:

十进制数值 = 1 10^(4-1) + 1 10^(4-2) + 0 10^(4-3) +

1 10^(4-4)。

= 1000 + 100 + 0 + 1。

= 1101。

所以,BCD数值1101转换为十进制为1101。

需要注意的是,BCD数值的每个位上的数字只能是0~9之间的

整数。

如果BCD数值的某个位上的数字超过了9,那么该BCD数值

就不是有效的BCD数值。

希望以上解答对你有帮助。

如果你还有其他问题,请随时提问。

二进制转BCD码

⼆进制转BCD码应⽤:⽤fpga实现对数码管显⽰,以前通常的⽅法是进⾏整除和取余进⾏运算,但是fpga并不擅长乘法除法运算,所以可以⽤BCD码来转换。

BCD码:通俗的可以理解为⽤四位⼆进制数表⽰⼀位⼗进制数字。

例如,256就可以⽤bcd码表⽰为:0010_1001_0110因此在数码管显⽰中,也就是把256各位分出来,就可以⽤bcd码来表⽰,下⾯说⼀种⼆进制转换bcd码的⽅法。

加3移位法:bcd码中只有0~9⼗进制数,但是在四位⼆进制中是16进制进1,因此在移位过程中要对⼆进制进⾏判断,当在移位之后的状态Qn+1⼤于9,要对Qn加6才可以。

例如1000移位⼤于9加6为0001_0110,对应bcd码中的16。

我们也可以在移位之前进⾏判断,如果移位之前的Qn数据⼤于4,说明Qn+1会溢出,所以可以+3再进⾏移位,例如1000⼤于4,加3为1011然后再进⾏移位0001_0110,16和刚才结果是⼀样的。

简单的说,判断的⽬的是防⽌下⼀次移位,发⽣数据溢出的情况思路:代码可以总结为三个部分:移位,加⼆进制数,判断(最后⼀次不需要判断)例如15 --- 1111(1)移位 0000_0000 加 0000_0001 判断 0000_0001(2)移位 0000_0010 加 0000_0011 判断 0000_0011(3)移位 0000_0110 加 0000_0111 判断 0000_1010(4)移位 0001_0100 加 0001_0101/*********************************功能:实现对6位⼗进制数以内的bcd码转换time: 2017/4/29vision:1.0*********************************/`define data_in_num 19`define data_bcd_num 23module pro_bcd(clk,rst_n,data_in,data_bcd);input clk;input rst_n;input [`data_in_num :0] data_in;output [`data_bcd_num:0] data_bcd;reg [`data_bcd_num:0] data_bcd_r;reg [1:0] state;reg [5:0] shift_cnt;always @(posedge clk or negedge rst_n)if(!rst_n)begindata_bcd_r <= 0;state <= 0;shift_cnt <= 0;endelsecase(state)2'd0:beginshift_cnt <= 0;data_bcd_r <= 0;state <= state + 1;end2'd1:begin //移位if(shift_cnt < `data_in_num + 1)begindata_bcd_r <= data_bcd_r<<1;shift_cnt <= shift_cnt + 1;state <= state + 1;endelsestate <= 0;end2'd2:begin //相加data_bcd_r <= data_bcd_r + data_in[`data_in_num + 1 - shift_cnt];state <= state + 1;end2'd3:begin //判断if(data_bcd_r[3:0] > 4 ) //1data_bcd_r <= data_bcd_r + 3;if(data_bcd_r[7:4]>4) //2data_bcd_r[7:4] <= data_bcd_r[7:4] + 3;if(data_bcd_r[11:8]>4) //3data_bcd_r[11:8] <= data_bcd_r[11:8] + 3;if(data_bcd_r[15:12]>4) //4data_bcd_r[15:12] <= data_bcd_r[15:12] + 3;if(data_bcd_r[19:16]>4) //5data_bcd_r[19:16] <= data_bcd_r[19:16] + 3;if(data_bcd_r[`data_bcd_num:20]>4) //6data_bcd_r[`data_bcd_num:20] <= data_bcd_r[`data_bcd_num:20] + 3;state <= 1;enddefault:state <= 0;endcaseassign data_bcd = (state == 3)&&(shift_cnt == `data_in_num + 1) ? data_bcd_r : data_bcd; endmodule。

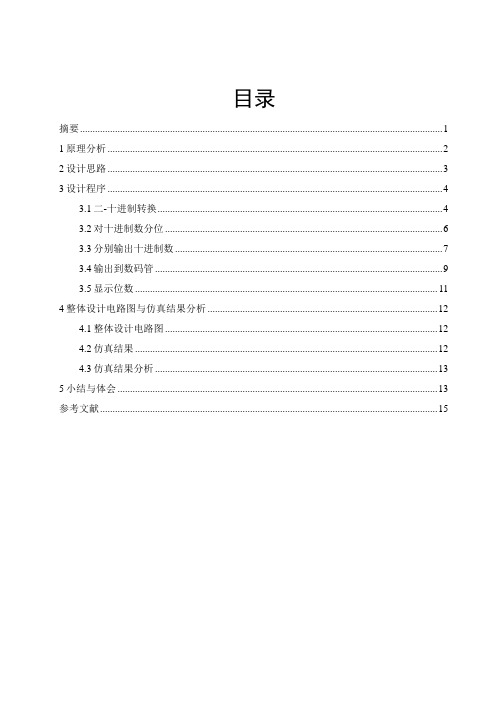

2进制-10进制40;BCD码41;数码转换器设计

目录摘要 (1)1原理分析 (2)2设计思路 (3)3设计程序 (4)3.1二-十进制转换 (4)3.2对十进制数分位 (6)3.3分别输出十进制数 (7)3.4输出到数码管 (9)3.5显示位数 (11)4整体设计电路图与仿真结果分析 (12)4.1整体设计电路图 (12)4.2仿真结果 (12)4.3仿真结果分析 (13)5小结与体会 (13)参考文献 (15)摘要BCD码亦称二进码十进数或二-十进制代码.用4位二进制数来表示1位十进制数中地0~9这10个数码.是一种二进制地数字编码形式,用二进制编码地十进制代码.BCD码这种编码形式利用了四个位元来储存一个十进制地数码,使二进制和十进制之间地转换得以快捷地进行.本文就是在quartus软件环境下利用VHDL语言将输入地八位二进制转换为BCD十进制数并且在数码管中显示出来.关键词:二--十进制转换器,BCD码,quartus,VHDL.2进制-10进制(BCD码)数码转换器设计1原理分析BCD 码这种编码形式利用了四个位元来储存一个十进制地数码,使二进制和十进制之间地转换得以快捷地进行.这种编码技巧,最常用于会计系统地设计里,因为会计制度经常需要对很长地数字串作准确地计算.相对于一般地浮点式记数法,采用BCD码,既可保存数值地精确度,又可免却使电脑作浮点运算时所耗费地时间.此外,对于其他需要高精确度地计算,BCD编码亦很常用.此处要介绍地是八位二进制转BCD码地硬件实现,采用左移加3地算法,具体描述如下:(1)、左移要转换地二进制码1位(2)、左移之后,BCD码分别置于百位、十位、个位(3)、如果移位后所在地BCD码列大于或等于5,则对该值加3(4)、继续左移地过程直至全部移位完成举例:将八位二进制码11111111转换成BCD码,其真值表如表1-1所示表1-1八位二进制码11111111转换成BCD码真值表2设计思路本次设计并没有用到左移地原理进行操作,直接对输出芯片地输出进行定义,虽然较为繁琐,但是原理却简单,所以才用此种方法,具体原理如下:2进制-10进制(BCD码)地转换可以通过一个芯片实现,即输入地八位二进制码通过编程输出十进制码,八位二进制能表示地最大地数为“255”,即输出地十进制为三位数,此时输出地BCD码就要有12位,每四位代表一个数,此时可再利用一个芯片把输出地12位数重新分配到三个输出管脚中,每个管脚代表一位数,时钟信号每输变一次,输出数字地位也会变一次,即个、十、百位分别输出,同时芯片地selout输出端输出时钟信号地数字到下一个芯片地接收端,通过编程实现000对应110,001对应101,010对应011,即输出0地位置可以表示数码管中所显示数字地位,然后再通过芯片输出到七段数码管进行显示,具体流程图如图2-1所示:图2-1 设计总流程图3设计程序3.1二-十进制转换原理图如图3-1所示:图3-1二进制到十进制转换原理图具体程序语言如下:library ieee。

verilog实现二进制与bcd码的转换算法

verilog实现二进制与bcd码的转换算法Verilog是一种硬件描述语言,常用于数字电路设计和硬件描述。

在数字电路设计中,二进制和BCD码之间的转换是一个常见的问题。

本文将介绍如何使用Verilog实现二进制与BCD码的转换算法。

首先,我们需要了解二进制和BCD码的基本概念。

二进制是一种基于2的数字系统,只包含0和1两个数字。

而BCD码是一种二进制编码形式,用4位二进制数表示一个十进制数的每一位。

例如,十进制数12用BCD码表示为0001 0010。

在Verilog中,我们可以使用模块化的方式来实现二进制与BCD码的转换算法。

首先,我们需要定义输入和输出端口。

输入端口是一个二进制数,输出端口是对应的BCD码。

```verilogmodule binary_to_bcd(input [3:0] binary,output [7:0] bcd);```接下来,我们可以使用组合逻辑来实现转换算法。

对于二进制数的每一位,我们可以使用除法和取余运算来计算对应的BCD码。

具体实现如下:```verilogalways @(*) beginbcd = 8'b00000000;if (binary >= 10) begin bcd[7] = 1;binary = binary - 10; endif (binary >= 8) begin bcd[6] = 1;binary = binary - 8; endif (binary >= 4) begin bcd[5] = 1;binary = binary - 4; endif (binary >= 2) begin bcd[4] = 1;binary = binary - 2; endif (binary >= 1) beginbcd[3] = 1;binary = binary - 1;endif (binary >= 0.5) beginbcd[2] = 1;binary = binary - 0.5;endif (binary >= 0.25) beginbcd[1] = 1;binary = binary - 0.25;endif (binary >= 0.125) beginbcd[0] = 1;endend```在上述代码中,我们首先将输出端口bcd初始化为全0。

二、进位制数之间的转换 1、二进制数转换成十进制数 根据

⑴ 汉字的输入编码 直接用西文键盘输入汉字,通常采用以下三类: ① 数字编码

常用的是国标区位码,用数字串代表一个汉字输入, 以国 家颁布的两级汉字为例。6763个两级汉字分为94个区,每个区 分94位,例如“中”字位于第54区48位,则他的区位码是5448。

GB2312分成94行×94列,行号称为区号,列号称为位号。

取整数

16 3

4

4.1250

0

3

6.875

B.0000

B

结果 (843.6875)10 = (34B.B)16 通常,先将十进制数转换成二进制数,再由二进制数转换成

8进或16进制数。

7、八进制数与二进制数之间的转换

一位八进制数相当于3位二进制数,所以八进制数转 换成二进制数,或二进制数转换成八进制数很方便。

⑶ 正数的反码与原码相同 例如: [+105]原= 01101001

[+105]反= 01101001 ⑷ 负数的反码 :该负数的原码按位(除符号位外)

取反 例如: x= -1101001B= -105

[-105]原 = 11101001 [-105]反= ( 28 – 1 )+ x =11111111 - 1101001

①正数补码运算 与原码运算相同

②负数补码运算

用补码可以将二进制数的减法运算转换为加法运算。

[X+Y]补 = [X]补 + [Y]补

[X - Y]补 =[X]补 +[-Y]补= [X]补 - [Y]补

补码的减法运算,可以归纳为:先求[X]补 、再求 [-Y]补 ,然后进行补码的加法运算。

补码加减法的结果仍然是补码,要得到结果的真值 ,必须求它对应的原码,再按定义展开相加。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

二进制码转换为十进制(BCD)码

转换原理

对于一个8位二进制码bn-1bn-2……b1b0,,其在十进制编码方式下的值为

把上式写出套乘的形式:

式中的每项乘2,相当于将寄存器中的二进制码左移1位,这就意味着利用移位寄存器可以完成二进制与8421BCD的转换。

[2]

在移位的过程中,当现态Sn<5时,次态不变。

当现态Sn=5、6、7时,左移一次,其次态Sn+1将会超过9,对于一个BCD码来说,这样的状态属于禁用状态。

而当Sn=8、9时,左移1位,则会向高1位的BCD码输入一个进位的信号 ,由于二进制和BCD码权不一致,当发生进位时,虽然码元只是左移1位,但次态Sn+1将减少6。

基于上面这两种情况,在B/BCD转换时需要对转换结果加以校正。

校正过程如下:当Sn>=5时,我们让Sn先加上3,然后再左移1位,次态 Sn+1=2(Sn+3)=2Sn+6,正好补偿由于进位而减少的数值,并且向后一个变换单元送入一个进位信号,这个方法叫“加3移位法”。

注意:现态和次态都是指BCD码,即用4位二进制表示的1位BCD码。

我们对Sn=8、9时举个例子:BCD码的1000(8)乘以2为0001_0110(16),但是左移后变为0001_0000,减少了6。

所以需要加上6,这里的方法是加3左移一位,相当于加上6。

转换方法

首先,先了解二进制与BCD码的位数对应关系,比如一个8位二进制码,可以表示的最大十进制数为255,转换成BCD码为 0010_0101_0101,共需12位,其中每4位组成一个BCD单元,有三个BCD单元,分别表示百位(hundreds)、十位(tens)和个位(units)。

n位二进制码转换成D位BCD码的n~D 对应关系表见表1。

表1 n~D对应关系

以8位二进制转换为3位BCD码为例,转换步骤是:将待转换的二进制码从最高位开始左移BCD的寄存器(从高位到低位排列),每移一次,检查每一位BCD码是否大于4,是则加上3,否则不变。

左移8次后,即完成了转换。

需要注意的是第八次移位后不需要检查是否大于5。

注意:为什么检查每一个BCD码是否大于4,因为如果大于4(比如5、6),下一步左移就要溢出了,所以加3,等于左移后的加6,起到十进制调节的作用。

表2给出了一个二进制码11101011转换成8421BCD码的时序。

表2 B/BCD时序

Verilog 代码

/*功能: 8位二进制转3位BCD码

输入参数:输入时钟clk,输入二进制数据dat

输出参数:个位units,十位tens,百位hundreds

备注:二进制转BCD码的实现方法很多,本例采用的是“加3移位法”

本例实现的是8位二进制转3位BCD码的例子,例如输入2’b11111111(255),输出0010_0101_0101(BCD)*/

module BIN_to_BCD(clk,dat,units,tens,hundreds);

input clk;

input[7:0] dat; //二进制输入数据

output[3:0] units;

output[3:0] tens;

output[3:0] hundreds;

reg[3:0] units_r,tens_r,hundreds_r;//BCD数据输出寄存器

reg[7:0] dat_r;

reg[11:0] temp; //中间寄存器

integer i;

assign units = units_r;

assign tens = tens_r;

assign hundreds = hundreds_r;

always @(posedge clk)

begin

dat_r = dat;

temp = 0;

for(i = 0;i < 7;i = i + 1) //循环7次,注意不是8次,因为第八次不需要修正

begin

temp = {temp[10:0],dat_r[7]}; //左移一位

if(temp[3:0] > 4'd4) //大于4,加三

temp[3:0] = temp[3:0]+4'd3;

if(temp[7:4] > 4'd4) //大于4,加三

temp[7:4] = temp[7:4]+4'd3;

if(temp[11:8] > 4'd4) //大于4,加三

temp[11:8] = temp[11:8]+4'd3;

dat_r=dat_r<<1; //最高变为原来dat_r的第六位

{hundreds_r,tens_r,units_r}={temp[10:0],dat[0]};//最后一次(第8次)不用修正end

end

endmodule

波形仿真报告说明

图1 输入二进制1111_1111(255)的波形仿真报告

分析综合报告说明

图2 8位二进制转BCD码的分析综合报告

待转换二进制位数(n)越大,锁消耗的LE的越多,当n大于8时,采用上面算法的Verilog HDL 代码会消耗大量的LE。