(实验二)二进制码转换为BCD码实验报告

EDA实验报告实验二:二进制码转换成BCD码

实验二二进制转换成BCD码

一、实验目的

设计并实现一个4位二进制码转换成BCD码的转换器。

二、实验仪器

SOPC实验箱、Quartus II软件

三、实验原理

对于不同代码之间的转换,有用硬件实现的,也有用软件实现的。

对于硬件实现,可以用一般的组合逻辑电路实现,也可以用译码器、编码器或只读存储器来实现。

本实验的原理见表3-1所示。

四、实验内容

1、启动Quartus II 建立一个空白工程,然后命名。

2、新建VHDL源程序文件并命名,输入程序代码并保存,进行综合编译,若在编译过程中发现错误,则找出并更正错误,直至编译成功为止。

3、新建仿真文件,对各模块设计进行仿真,验证设计结果。

打印仿真结果。

五、实验步骤

1.各模块程序:

1)用文本输入法实现秒的计时,程序如下:

module BCD(D,B);

output [4:0] B;

input [3:0] D;

reg [4:0] B;

always@ (D)

begin

if(D<4'b1010) begin B[3:0]=D[3:0];B[4]=1'b0;end

else begin B[3:0]=D[3:0]-4'b1010;B[4]=1'b1;end

end

endmodule

2.建立工作库文件夹,输入设计项目原理图或vorilog代码并存盘。

3.生成RTL图。

4.进行波形仿真,仿真后波形如下:

六、实验结果与现象验证

输入任何一个十六进制数产生了与二进制码转换成BCD码的转换真值表相对于的BCD码.。

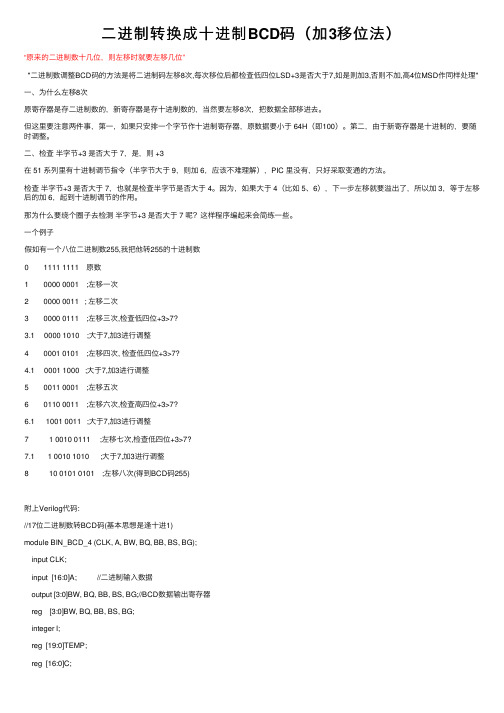

二进制转换成十进制BCD码(加3移位法)

⼆进制转换成⼗进制BCD码(加3移位法)“原来的⼆进制数⼗⼏位,则左移时就要左移⼏位”"⼆进制数调整BCD码的⽅法是将⼆进制码左移8次,每次移位后都检查低四位LSD+3是否⼤于7,如是则加3,否则不加,⾼4位MSD作同样处理"⼀、为什么左移8次原寄存器是存⼆进制数的,新寄存器是存⼗进制数的,当然要左移8次,把数据全部移进去。

但这⾥要注意两件事,第⼀,如果只安排⼀个字节作⼗进制寄存器,原数据要⼩于 64H(即100)。

第⼆,由于新寄存器是⼗进制的,要随时调整。

⼆、检查半字节+3 是否⼤于 7,是,则 +3在 51 系列⾥有⼗进制调节指令(半字节⼤于 9,则加 6,应该不难理解),PIC ⾥没有,只好采取变通的⽅法。

检查半字节+3 是否⼤于 7,也就是检查半字节是否⼤于 4。

因为,如果⼤于 4(⽐如 5、6),下⼀步左移就要溢出了,所以加 3,等于左移后的加 6,起到⼗进制调节的作⽤。

那为什么要绕个圈⼦去检测半字节+3 是否⼤于 7 呢?这样程序编起来会简练⼀些。

⼀个例⼦假如有⼀个⼋位⼆进制数255,我把他转255的⼗进制数0 1111 1111 原数1 0000 0001 ;左移⼀次2 0000 0011 ; 左移⼆次3 0000 0111 ;左移三次,检查低四位+3>7?3.1 0000 1010 ;⼤于7,加3进⾏调整4 0001 0101 ;左移四次, 检查低四位+3>7?4.1 0001 1000 ;⼤于7,加3进⾏调整5 0011 0001 ;左移五次6 0110 0011 ;左移六次,检查⾼四位+3>7?6.1 1001 0011 ;⼤于7,加3进⾏调整7 1 0010 0111 ;左移七次,检查低四位+3>7?7.1 1 0010 1010 ;⼤于7,加3进⾏调整8 10 0101 0101 ;左移⼋次(得到BCD码255)附上Verilog代码://17位⼆进制数转BCD码(基本思想是逢⼗进1)module BIN_BCD_4 (CLK, A, BW, BQ, BB, BS, BG);input CLK;input [16:0]A; //⼆进制输⼊数据output [3:0]BW, BQ, BB, BS, BG;//BCD数据输出寄存器reg [3:0]BW, BQ, BB, BS, BG;integer I;reg [19:0]TEMP;reg [16:0]C;always @ (posedge CLK)beginC=A;TEMP=0;for (I=1; I<17; I=I+1)begin{TEMP, C}={TEMP[18:0], C, 1'b0};//左移⼀位 if (TEMP[3:0]>4'b0100)beginTEMP[3:0]=TEMP[3:0]+3; // >4则加3endif (TEMP[7:4]>4'b0100)beginTEMP[7:4]=TEMP[7:4]+3;endif (TEMP[11:8]>4'b0100)beginTEMP[11:8]=TEMP[11:8]+3;endif (TEMP[15:12]>4'b0100)beginTEMP[15:12]=TEMP[15:12]+3;endif (TEMP[19:16]>4'b0100)beginTEMP[19:16]=TEMP[19:16]+3;end{BW, BQ, BB, BS, BG}={TEMP[18:0], A[0]}; endendendmodule。

八位二进制——BCD码转换器

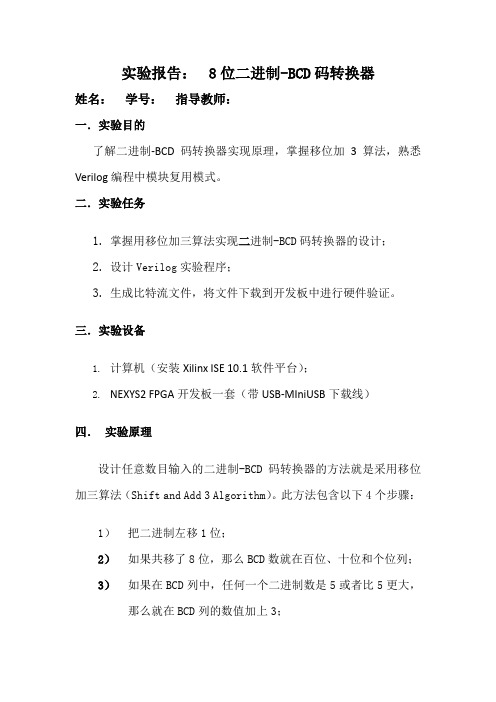

实验报告:8位二进制-BCD码转换器姓名:学号:指导教师:一.实验目的了解二进制-BCD码转换器实现原理,掌握移位加3算法,熟悉Verilog编程中模块复用模式。

二.实验任务1.掌握用移位加三算法实现二进制-BCD码转换器的设计;2.设计Verilog实验程序;3.生成比特流文件,将文件下载到开发板中进行硬件验证。

三.实验设备1.计算机(安装Xilinx ISE 10.1软件平台);2.NEXYS2 FPGA开发板一套(带USB-MIniUSB下载线)四.实验原理设计任意数目输入的二进制-BCD码转换器的方法就是采用移位加三算法(Shift and Add 3 Algorithm)。

此方法包含以下4个步骤:1)把二进制左移1位;2)如果共移了8位,那么BCD数就在百位、十位和个位列;3)如果在BCD列中,任何一个二进制数是5或者比5更大,那么就在BCD列的数值加上3;4)回到步骤1)。

其工作过程如图1所示:图1. 一个8位的二进制数转换成BCD码的步骤五.实验内容在Xilinx ISE 10.1上完成8位二进制-BCD码转换器设计,输入设计文件,仿真后,生成二进制码流文件下载到FPGA开发板上进行验证;1)依照实验1的方式,在Xilinx ISE 10.1中新建一个工程example02;2)在工程管理区任意位置单击鼠标右键,在弹出的快捷菜单中选择“New Source”命令,弹出新建源代码对话框,这里我们选择“Verilog Module”类型,输入Verilog文件名“binbcd8.v”,完整代码如下:module binbcd8(input [7:0] b,output reg [9:0] p);reg [17:0] z;integer i;always @(*)beginfor (i=0;i<=17;i=i+1)z[i]=0;z[10:3]=b;repeat(5) //重复5次beginif (z[11:8]>4)z[11:8]=z[11:8]+3;if (z[15:12]>4)z[15:12]=z[15:12]+3;z[17:1]=z[16:0];endp=z[17:8];endendmodule3)设计相应的7段显示管程序,将相应的十进制数在开发板的显示管上显示出来。

数字逻辑转换实验报告

一、实验目的1. 理解和掌握数字逻辑转换的基本原理和方法。

2. 掌握将不同编码形式的数字信号相互转换的技巧。

3. 通过实验验证数字逻辑转换电路的正确性和性能。

二、实验原理数字逻辑转换是指将一种数字信号转换为另一种数字信号的过程。

常见的数字逻辑转换包括BCD码与二进制码之间的转换、格雷码与二进制码之间的转换、8421码与余3码之间的转换等。

本实验主要涉及以下几种转换:1. BCD码与二进制码之间的转换:BCD码(Binary-Coded Decimal)是一种用4位二进制数表示1位十进制数的编码方式。

将BCD码转换为二进制码时,只需将每一位BCD码直接转换为对应的二进制码即可。

2. 格雷码与二进制码之间的转换:格雷码(Gray Code)是一种循环码,相邻两个码字之间只有一个位码发生改变。

将格雷码转换为二进制码时,只需将格雷码的最低位取反即可。

3. 8421码与余3码之间的转换:8421码是一种有权码,从左到右,第一位1代表2,第二位1代表4,第三位1代表2,第四位1代表1。

余3码是由8421BCD码加上0011形成的一种无权码。

将8421码转换为余3码时,只需将8421码的每一位加3即可。

三、实验设备与器材1. 数字逻辑实验箱2. 数字逻辑转换电路模块3. 示波器4. 信号发生器5. 电源四、实验步骤1. 连接实验电路:根据实验要求,连接数字逻辑转换电路模块,并确保电路连接正确。

2. 设置输入信号:使用信号发生器产生待转换的数字信号,并将其输入到转换电路中。

3. 观察转换结果:使用示波器观察转换电路的输出信号,记录实验数据。

4. 比较理论值与实验值:根据实验原理,计算理论值,并与实验值进行比较。

5. 分析实验数据:分析实验数据,总结实验结果,验证数字逻辑转换电路的正确性和性能。

五、实验数据及分析1. BCD码与二进制码之间的转换输入BCD码:0011理论转换结果:0001 0011实验转换结果:0001 00112. 格雷码与二进制码之间的转换输入格雷码:1100理论转换结果:1110实验转换结果:11103. 8421码与余3码之间的转换输入8421码:0101理论转换结果:0110实验转换结果:0110通过实验数据的对比分析,可以得出以下结论:1. 实验电路能够正确实现BCD码与二进制码、格雷码与二进制码、8421码与余3码之间的转换。

单片机bcd码转换

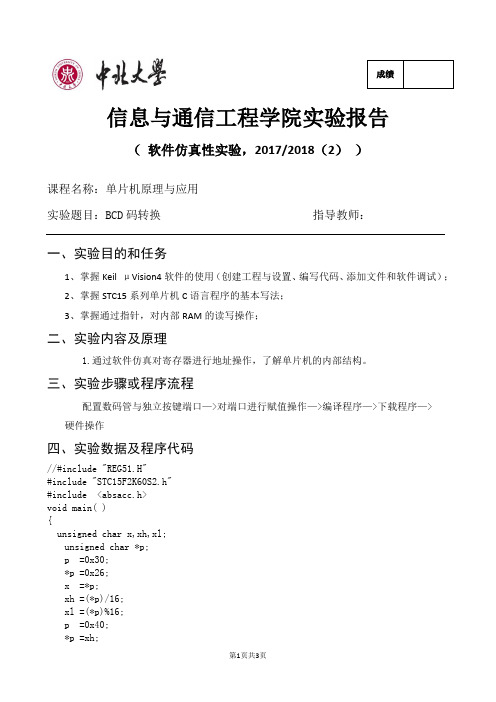

(软件仿真性实验,2017/2018(2))课程名称:单片机原理与应用实验题目:BCD码转换指导教师:一、实验目的和任务1、掌握Keil μVision4软件的使用(创建工程与设置、编写代码、添加文件和软件调试);2、掌握STC15系列单片机C语言程序的基本写法;3、掌握通过指针,对内部RAM的读写操作;二、实验内容及原理1.通过软件仿真对寄存器进行地址操作,了解单片机的内部结构。

三、实验步骤或程序流程配置数码管与独立按键端口—>对端口进行赋值操作—>编译程序—>下载程序—> 硬件操作四、实验数据及程序代码//#include "REG51.H"#include "STC15F2K60S2.h"#include <absacc.h>void main( ){unsigned char x,xh,xl;unsigned char *p;p =0x30;*p =0x26;x =*p;xh =(*p)/16;xl =(*p)%16;p =0x40;*p =xh;p =p+1;*p =xl;while(1){;}}五、实验数据分析及处理通过对试验箱的观察,结合程序的编程,能够实现对数码管的正确操作,对寄存器地址进行直接分配,实现端口的配置,深刻了解BCD原理并结合实验。

图1.1 BCD码转换图1.2 BCD码转换六、实验结论与感悟(或讨论)了解keil的仿真原理,掌握了对单片机寄存器的操作,明白其工作原理,并能正确的实现其功能,对BCD码有了更深刻的了解,能够开发实验应用操作。

能够学以致用。

二进制转BCD码

⼆进制转BCD码应⽤:⽤fpga实现对数码管显⽰,以前通常的⽅法是进⾏整除和取余进⾏运算,但是fpga并不擅长乘法除法运算,所以可以⽤BCD码来转换。

BCD码:通俗的可以理解为⽤四位⼆进制数表⽰⼀位⼗进制数字。

例如,256就可以⽤bcd码表⽰为:0010_1001_0110因此在数码管显⽰中,也就是把256各位分出来,就可以⽤bcd码来表⽰,下⾯说⼀种⼆进制转换bcd码的⽅法。

加3移位法:bcd码中只有0~9⼗进制数,但是在四位⼆进制中是16进制进1,因此在移位过程中要对⼆进制进⾏判断,当在移位之后的状态Qn+1⼤于9,要对Qn加6才可以。

例如1000移位⼤于9加6为0001_0110,对应bcd码中的16。

我们也可以在移位之前进⾏判断,如果移位之前的Qn数据⼤于4,说明Qn+1会溢出,所以可以+3再进⾏移位,例如1000⼤于4,加3为1011然后再进⾏移位0001_0110,16和刚才结果是⼀样的。

简单的说,判断的⽬的是防⽌下⼀次移位,发⽣数据溢出的情况思路:代码可以总结为三个部分:移位,加⼆进制数,判断(最后⼀次不需要判断)例如15 --- 1111(1)移位 0000_0000 加 0000_0001 判断 0000_0001(2)移位 0000_0010 加 0000_0011 判断 0000_0011(3)移位 0000_0110 加 0000_0111 判断 0000_1010(4)移位 0001_0100 加 0001_0101/*********************************功能:实现对6位⼗进制数以内的bcd码转换time: 2017/4/29vision:1.0*********************************/`define data_in_num 19`define data_bcd_num 23module pro_bcd(clk,rst_n,data_in,data_bcd);input clk;input rst_n;input [`data_in_num :0] data_in;output [`data_bcd_num:0] data_bcd;reg [`data_bcd_num:0] data_bcd_r;reg [1:0] state;reg [5:0] shift_cnt;always @(posedge clk or negedge rst_n)if(!rst_n)begindata_bcd_r <= 0;state <= 0;shift_cnt <= 0;endelsecase(state)2'd0:beginshift_cnt <= 0;data_bcd_r <= 0;state <= state + 1;end2'd1:begin //移位if(shift_cnt < `data_in_num + 1)begindata_bcd_r <= data_bcd_r<<1;shift_cnt <= shift_cnt + 1;state <= state + 1;endelsestate <= 0;end2'd2:begin //相加data_bcd_r <= data_bcd_r + data_in[`data_in_num + 1 - shift_cnt];state <= state + 1;end2'd3:begin //判断if(data_bcd_r[3:0] > 4 ) //1data_bcd_r <= data_bcd_r + 3;if(data_bcd_r[7:4]>4) //2data_bcd_r[7:4] <= data_bcd_r[7:4] + 3;if(data_bcd_r[11:8]>4) //3data_bcd_r[11:8] <= data_bcd_r[11:8] + 3;if(data_bcd_r[15:12]>4) //4data_bcd_r[15:12] <= data_bcd_r[15:12] + 3;if(data_bcd_r[19:16]>4) //5data_bcd_r[19:16] <= data_bcd_r[19:16] + 3;if(data_bcd_r[`data_bcd_num:20]>4) //6data_bcd_r[`data_bcd_num:20] <= data_bcd_r[`data_bcd_num:20] + 3;state <= 1;enddefault:state <= 0;endcaseassign data_bcd = (state == 3)&&(shift_cnt == `data_in_num + 1) ? data_bcd_r : data_bcd; endmodule。

实验一_二进制转BCD码实验

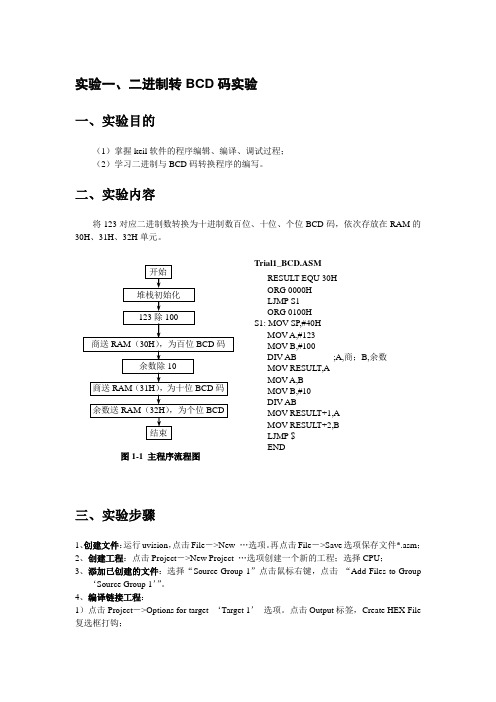

实验一、二进制转BCD 码实验 一、实验目的(1)掌握keil 软件的程序编辑、编译、调试过程; (2)学习二进制与BCD 码转换程序的编写。

二、实验内容将123对应二进制数转换为十进制数百位、十位、个位BCD 码,依次存放在RAM 的30H 、31H 、32H 单元。

三、实验步骤1、创建文件:运行uvision ,点击File ->New …选项。

再点击File ->Save 选项保存文件*.asm ;2、创建工程:点击Project ->New Project …选项创建一个新的工程;选择CPU ;3、添加已创建的文件:选择“Source Group 1”点击鼠标右键,点击 “Add Files to Group ‘Source Group 1’”。

4、编译链接工程:1)点击Project ->Options for target ‘Target 1’ 选项。

点击Output 标签,Create HEX File 复选框打钩;Trial1_BCD.ASMRESULT EQU 30H ORG 0000H LJMP S1 ORG 0100H S1: MOV SP,#40H MOV A,#123 MOV B,#100DIV AB ;A,商;B,余数 MOV RESULT,A MOV A,B MOV B,#10 DIV ABMOV RESULT+1,A MOV RESULT+2,B LJMP $ END图1-1 主程序流程图2)点击Project->Build target …;5、检错、纠错;6、调试工程:1)点击Debug->Start/Stop Debug Session进入/退出调试状态。

2)运行程序后,观察RAM 30~32H单元存放的数据:View->Memory Window->Address:d:30H(RAM);c:0100H(ROM);四、实验结果五、思考题1、用C51编写源程序,实现本实验要求的功能。

实验二报告

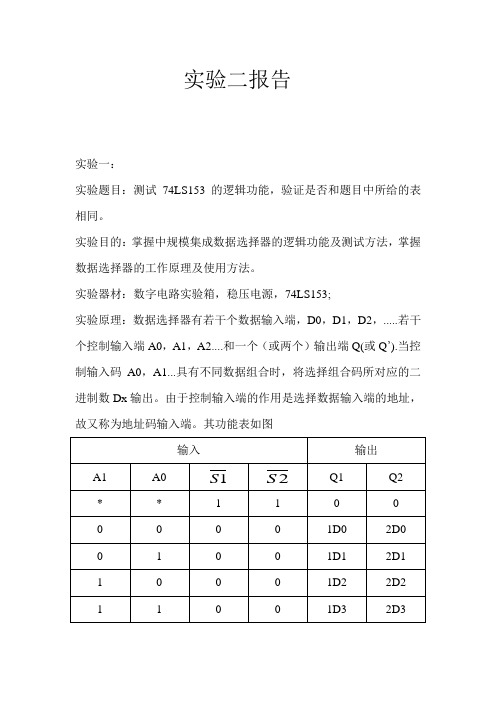

实验二报告实验一:实验题目:测试74LS153的逻辑功能,验证是否和题目中所给的表相同。

实验目的:掌握中规模集成数据选择器的逻辑功能及测试方法,掌握数据选择器的工作原理及使用方法。

实验器材:数字电路实验箱,稳压电源,74LS153;实验原理:数据选择器有若干个数据输入端,D0,D1,D2,.....若干个控制输入端A0,A1,A2....和一个(或两个)输出端Q(或Q’).当控制输入码A0,A1...具有不同数据组合时,将选择组合码所对应的二进制数Dx输出。

由于控制输入端的作用是选择数据输入端的地址,故又称为地址码输入端。

其功能表如图输入输出A1 A0 1S Q1 Q2S2* * 1 1 0 00 0 0 0 1D0 2D00 1 0 0 1D1 2D11 0 0 0 1D2 2D21 1 0 0 1D3 2D3实验内容:将74LS153插入实验箱中,按照原理图用导线进行连接,最后将输出与一个LED灯相连,根据LED灯的亮灭来判断逻辑功能是否正确。

实验结果:实验测得的真值表与题目所给的真值表相同。

实验二:实验题目:用多路选择器设计一个8421-BCD非法码检测电路,使得当输入端为非法码组合是输出1,否则为0。

二进制数与BCD码的对应关系如表所示。

写出函数Y的表达式,并进行化简,然后画出电路图,接线调试电路,用发光二极管显示输出结果,观察是否与表相符。

设Y=0表示发光二极管熄灭,Y=1表示发光二极管点亮。

二进制B BCD码B3 B2 B1 B0 Q3 Q2 Q1 Q0 Y0 0 0 0 0 0 0 0 00 0 0 1 0 0 0 1 00 0 1 0 0 0 1 0 00 0 1 1 0 0 1 1 00 1 0 0 0 1 0 0 00 1 0 1 0 1 0 1 00 1 1 0 0 1 1 0 00 1 1 1 0 1 1 1 01 0 0 0 1 0 0 0 01 0 0 1 1 0 0 1 01 0 1 0 0 0 0 0 1 1 0 1 1 0 0 0 1 1 1 1 0 0 0 0 1 0 1 1 1 0 1 0 0 1 1 1 1 1 1 0 0 1 0 0 1 1111111实验目的:掌握数据选择器的工作原理,会设计简单的数据选择器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验二二进制码转换为 BCD 码

一、实验目的

1、掌握数码转换基本方法,加深对数码的理解。

2、用于十进制BCD 码显示。

二、实验内容

将AX 的内容转换为十进制BCD 码。

三、

实验程序框图

四、实验步骤

脱机模式:

(1)在 P.态,按 SCAL 键,输入 2CE0,按 EXEC 键。

(2)复位 RST 键,由于 AX 中给定数为 0FFFF,查看 BCD 码结果保留在 4100H ~ 4104H

单元中,故其值应为06、 05、05、 03、05。

联机模式:

( 1)在 PC 机和实验系统联机状态下,运行该实验程序,可用鼠标左键单击菜单栏“文件”

或工具栏“打开图标”,弹出“打开文件”的对话框,然后打开8kAsm 文件夹,点击S2.ASM

文件,单击“确定”即可装入源文件,再单击工具栏中编译,即可完成源文件自动编译、

装载目标代码功能,再单击“调试”中“连续运行”或工具图标运行,即开始运行程序。

( 2)复位“系统复位” 键,由于 AX 中给定数为 0FFFF,查看 BCD 码结果保留在 4100H ~4104H 单元中,故其值应为 06、 05、 05、 03、 05。

注:操作过程参照“实验一二进制多位加法运算”。

五、实验程序清单

X:\DICE-8086K3微机原理与接口实验箱CDROM\CODE\86kasm\S2.ASM

;将 AX 拆为 5 个 BCD码 , 并存入 Result 开始的 5 个单元

DATA SEGMENT AT 0;S2.ASM,BIN-->BCD

ORG 4000H

RESULT DB 5 DUP(?)

DATA ENDS

CODE SEGMENT

ASSUME CS:CODE, DS:DATA

ORG 2CE0H

START PROC NEAR

MOV AX, DATA

MOV DS, AX

MOV DX,0000H

MOV AX, 65535

MOV CX, 10000

DIV CX

MOV RESULT, AL;除以 10000,得 WAN位数

MOV AX,DX

MOV DX,0000H

MOV CX, 1000

DIV CX

MOV RESULT+1, AL;除以 1000,得 QIAN位数

MOV AX,DX

MOV DX,0000H

MOV CX, 100

DIV CX

MOV RESULT+2, AL;除以 100,得 BAI 位数

MOV AX,DX

MOV DX,0000H

MOV CX, 10

DIV CX

MOV RESULT+3, AL;除以 10,得 SHI 位数

MOV RESULT+4, DL;得 GE位数

JMP $

CODE ENDS

END START。