verilog hdl实验报告

数电实验报告2.1—基于Verilog HDL显示译码器设计

<基于Verilog HDL显示译码器设计>实验报告学生姓名:班级学号:指导老师:<实验报告内容>一、实验名称:基于Verilog HDL 显示译码器设计二、实验学时:4学时 三、实验目的:进一步掌握QuartusII 软件逻辑电路设计环境及Verilog HDL 的基本语法,熟悉设计流程及思路。

掌握显示译码器的工作原理及应用。

(提示:本实验将涉及到verilog 的条件语句(如if …else, case ….end case, for ….等)、赋值语句(如assign 等)和二进制变量位宽的定义等内容,请大家实验前做好本部分预习和自学,可参考本课本第九章内容,也可自行查找有关Verilog 设计基础的相关内容,推荐参考书:北京航空航天出版社,夏宇闻编著 )。

通过对所设计逻辑电路功能仿真,分析所设计电路逻辑功能是否正确,掌握逻辑功能仿真的方法。

四、实验内容:基于verilog 的显示译码器逻辑设计及功能仿真五、实验原理:(1)半导体发光二极管(LED )数码显示器:半导体发光二极管数码显示器由7(或8)个LED 排成“日”字形,称为七段(或八段),封装成数码管,如错误!未找到引用源。

所示。

LED 数码管内部有共阴极和共阳极两种接法。

如错误!未找到引用源。

(2)常用显示译码器管脚功能(74LS148):LCD —七段显示译码器:介绍常用的74LS148七段显示译码器,图 3为74LS4874LS48(a )图 1 图 2 CC fg a bcd e BI 7123456图 3(3)74LS48的逻辑功能:如表1:表1其译码器输出(Ya~Yg)是高电平有效,适用于驱动共阴极LED数码管,显示的字形表中所示。

因其译码器输出端的内部有上拉电阻(是2K的限流电阻),因此在与LED管连接时无需再外接限流电阻。

具体功能介绍及内部设计图,请自行上网查阅74LS48的DATASHEET。

VerilogHDL实验报告

VerilogHDL实验报告实验一Modelsim仿真软件的使用一、实验目的(1)熟悉Modelsim 软件(2)掌握Modelsim 软件的编译、仿真方法(3)熟练运用Modelsim 软件进行HDL 程序设计开发二、实验内容1、实验要求用Verilog HDL 程序实现一个异或门,Modelism仿真,观察效果。

2、步骤1、建立工程2、添加文件到工程3、编译文件4、查看编译后的设计单元5、将信号加入波形窗口6、运行仿真3、方法moduleyihuo (a,b,c);inputa,b;output c;assign c=a^b;endmodule测试程序:module t_yihuo;reg a,b; wire c;initial begin a=0; forever #20 a=~a; end initial begin b=0; forever #30 b=~b; endyihuou1(a,b,c);endmodule二、实验结果波形图:三、分析和心得通过这次的实验,我基本熟悉Modelsim软件,掌握了Modelsim软件的编译、仿真方法。

同时在编写程序的过程中,加深了我对课上所讲的HDL的语法的认识。

实验二简单组合电路设计一、实验目的(1)掌握基于Modelsim的数字电路设计方法(2)熟练掌握HDL 程序的不同实现方法二、实验内容1、实验要求设计一个三人表决器(高电平表示通过),实验内容如下:(1)三个人,一个主裁判,两个副裁判;(2)规则:只要主裁判同意,输出结果为通过;否则,按少数服从多数原则决定是否通过。

使用 Verilog HDL 程序实现上述实验内容,并使用modelsim 仿真。

2、方法module test(a,b,c,s);inputa,b,c;output s;assign s=c|(b&a);endmodulemodulet_test;rega,b,c;wire s;initialbegina=0;forever#10 a=~a;endinitialbeginb=0;forever #20 b=~b;endinitialbeginc=0;forever#40 c=~c;endtest u1(a,b,c,s);endmodule三、实验结果四、分析和心得通过本次实验,我掌握基于Modelsim的简单数字电路设计方法,且尝试了用不同方法实现功能,三人表决器可以通过testbench测试程序实现,也可以利用always模块实现,可见程序的设计思想是很重要的。

数字系统设计与Verilog HDL实验报告(五)

《数字系统设计与Verilog HDL》实验报告(五)班级: 自动1003班**: **学号: ********实验五、自动售饮料机系统设计一、实验目的1、了解及掌握状态机的基本构成用法;二、通过ModelSim软件编写程序, 用状态机可以编程设计简单的自动控制系统。

三、实验内容四、设计一个自动售饮料机。

假定每瓶饮料售价为2.5元, 可使用两种硬币, 即5角和1元, 机器有找零功能。

五、机器设计有2个投币孔, 可用2个按键来代替。

还设有2个输出孔, 分别输出饮料和找零, 提示用户取走饮料和零钱。

六、实验步骤及源程序新建工程及文件, 分别添加设计程序及测试程序, 进行编译及纠错, 编译通过后运行程序仿真进行调试得出结果。

设计模块:module sell(yi_yuan,wu_jiao, get,half_out,sell_out,reset,clk);parameter idle=0, half=1, one=2,two=3,three=4;input yi_yuan,wu_jiao,reset,clk;output get,half_out,sell_out;reg get,half_out,sell_out;reg[2:0] s;always @(posedge clk)beginif(reset)beginsell_out=0; get=0; half_out=0; s=idle;endelsecase(s)idle: beginsell_out=0; get=0; half_out=0;if(wu_jiao) s=half;else if(yi_yuan)s=one;endhalf: beginif(wu_jiao) s=one;else if(yi_yuan)s=two;endone: beginif(wu_jiao) s=two;else if(yi_yuan)s=three;endtwo: beginif(wu_jiao) s=three;else if(yi_yuan)beginsell_out=1;get=1; s=idle;endendthree: beginif(wu_jiao)beginsell_out=1; get=1; s=idle;endelse if(yi_yuan)beginsell_out=1;get=1;half_out=1; s=idle;endenddefault:beginsell_out=0; get=0; half_out=0; s=idle; endendcaseendendmodule测试模块:`timescale 1ns/1nsmodule sell_top;reg yi_yuan,wu_jiao,reset,CLK;wire get,half_out,sell_out;always #50 CLK=~CLK;initialbeginCLK =0; reset=1;#100 reset=0;yi_yuan=0;wu_jiao=0;endalways@(posedge CLK)beginwu_jiao={$random}%2;#50 wu_jiao=0;endalways@(posedge CLK)beginif(!wu_jiao)yi_yuan=1;#50 yi_yuan=0;endsell m(.yi_yuan(yi_yuan),.wu_jiao(wu_jiao), .get(get),.half_out(half_out),.sell_out(sell_out),.reset(reset),.clk(CLK));endmodule七、实验结果八、实验心得体会由于老师在实验前已经很详细的为我们讲解了这次实验的要点和要注意的问题, 所以这次实验我们完成的还是很成功的。

Verilog HDL实验报告

HDL实验报告专业电子科学与技术姓名学号指导老师1 实验一Modelsim仿真软件的使用1.1 实验目的(1)熟悉Modelsim 软件;(2)掌握Modelsim 软件的编译、仿真方法;(3)熟练运用Modelsim 软件进行HDL 程序设计开发。

1.2 实验步骤(1)学习使用Modelsim软件;(2)分析原理及功能;(3)用Verilog HDL编写程序;(4)编写测试程序进行仿真;(4)观察波形,分析仿真结果是否正确。

1.3 实验内容用Verilog HDL 程序实现一个异或门,Modelsim 仿真,观察效果。

1.4.1 程序module my_xor(ina,inb,out);input ina,inb;output out;assign out=ina^inb;endmodulemodule t_xor;reg ina,inb;wire out;initialbeginina=1'b0;forever #20 ina=~ina;endinitialbegininb=1'b0;forever #10 inb=~inb;endmy_xor tt(.ina(ina),.inb(inb),.out(out));endmodule2 实验二简单组合电路设计2.1 实验目的(1)掌握基于Modelsim 的数字电路设计方法;(2)熟练掌握HDL 程序的不同实现方法2.2 实验步骤(1)分析原理及功能;(2)根据原理用Verilog HDL编写程序;(3)编写测试程序进行仿真;(4)观察波形,分析仿真结果是否正确。

2.3 实验内容设计一个三人表决器(高电平表示通过) ,实验内容如下:(1)三个人,一个主裁判,两个副裁判;(2)规则:只要主裁判同意,输出结果为通过;否则,按少数服从多数原则决定是否通过。

使用Verilog HDL 程序实现上述实验内容,并使用modelsim 仿真(要求:至少使用两种方法实现上述实验内容和testbench)。

Verilog HDL硬件描述语言实验报告

Verilog HDL实验报告学院:应用科学学院班级:电科13-2班姓名:学号:实验一组合逻辑电路设计(1)实验目的(1)熟悉FPGA设计流程;(2)熟悉DE2开发板的基本元件使用(开关、发光二极管);(3)学习基本组合逻辑元件的Verilog HDL设计以及实现(数据选择器);(4)掌握连续赋值语句使用;实验内容本实验的目的是学习如何连接一个简单的外部输入、输出器件到FPGA 芯片以及如何在FPGA器件上实现逻辑电路控制简单外部器件。

考虑使用DE2开发板上拨动开关SW17-0(toggle Switch)作为电路的输入。

使用发光二极管(Light Emitt-ing Diodes,LEDs)和7段显示数码管(7-segment Display)作为电路的输出。

第1部分连续赋值语句步骤1、新建Quartus II工程,选择Cyclone II EP2C35F672C6作为目标芯片,该芯片是DE2开发板上的FPGA芯片;2、编写Verilog HDL代码加入到Quaruts II工程;3、引脚分配,并编译工程该工程;4、将编译好的电路下载到FPGA器件。

扳动拨动开关观察相应的发光二极管显示,验证电路功能是否正确;代码module part1(input wire[2:0]SW,output wire LEDR);wire r_g,s_g,qa,qb;and u1(r_g, SW[0], SW[1]);and u2(s_g, SW[1], SW[2]);nor u3(qa, r_g, qb);nor u4(qb, qa, s_g);assign LEDR = qa;endmodule第2部分简单的数据选择器步骤1 .新建Quartus II工程;2.在工程中加入8位宽的2选1数据选择器Verilog HDL代码。

使用DE2开发板上的SW17作为输入s,开关SW7-0作为输入X,SW15-8作为输入Y。

Verilog HDL 实验报告

Verilog实验报告班级:学号:姓名:实验1 :用 Verilog HDL 程序实现直通线1 实验要求:(1) 编写一位直通线的 Veirlog HDL 程序.(2) 编写配套的测试基准.(3) 通过 QuartusII 编译下载到目标 FPGA器件中进行验证.(4) 建议用模式 52 试验程序:module wl(in,out);input in;output out;wire out;assign out=in;endmodule3 测试基准:`include “wl.v”module wl_tb;reg in_tb;wire out_tb;initialbeginin_tb =0;#100 in_tb =1;#130 in_tb =0;endendmodule4 仿真图形:实验2 :用 Verilog HDL 程序实现一位四选一多路选择器1实验要求:(1) 编写一位四选一多路选择器的 Veirlog HDL 程序.(2) 编写配套的测试基准.(3) 通过 QuartusII 编译下载到目标 FPGA器件中进行验证.(4)建议用模式 52 试验程序:module mux4_to_1 (out,i0,i1,i2,i3,s1,s0);output out;input i0,i1,i2,i3;input s1, s0;reg out;always @ (s1 or s0 or i0 or i1 or i2 or i3)begincase ({s1, s0})2'b00: out=i0;2'b01: out=i1;2'b10: out=i2;2'b11: out=i3;default: out=1'bx;endcaseendendmodule3 测试基准:`include "mux4_to_1.v"module mux4_to_1_tb1;reg ain,bin,cin,din;reg[1:0] select;reg clock;wire outw;initialbeginain=0;bin=0;cin=0;din=0;select=2'b00;clock=0;endalways #50 clock=~clock;always @(posedge clock)begin#1 ain={$random} %2;#3 bin={$random} %2;#5 cin={$random} %2;#7 din={$random} %2;endalways #1000 select[0]=!select[0];always #2000 select[1]=!select[1];mux4_to_1 m(.out(outw),.i0(ain),.i1(bin),.i2(cin),.i3(din),.s1(select[1]),.s0(select[0])); endmodule4 仿真图形:实验3:用 Verilog HDL 程序实现十进制计数器1实验要求:(1) 编写十进制计数器的 Veirlog HDL 程序. 有清零端与进位端, 进位端出在输出为 9 时为高电平.(2) 编写配套的测试基准.(3) 通过 QuartusII 编译下载到目标 FPGA器件中进行验证.(4) 自行选择合适的模式2 实验程序:module counter_10c (Q, clock, clear, ov);output [3:0] Q;output ov;input clock, clear;reg [3:0] Q;reg ov;initial Q=4'b0000;always @ (posedge clear or negedge clock)beginif (clear)Q<=4'b0;else if (Q==8)beginQ<=Q+1;ov<=1'b1;endelse if (Q==9)beginQ<=4'b0000;ov<=1'b0;endelsebeginQ<=Q+1;ov<=1'b0;endendendmodule3 测试基准:`include"./counter_10c.v"module counter_10c_tb;wire[3:0] D_out;reg clk,clr;wire c_out;reg[3:0] temp;initialbeginclk=0;clr=0;#100 clr=1;#20 clr=0;endalways #20 clk=~clk;counter_10c m_1(.Q(D_out),.clear(clr),.clock(clk),.ov(c_out)); endmodule4 仿真波形:实验4 :用 Verilog HDL 程序实现序列检测器1 实验要求:、(1) 编写序列检测器的 Veirlog HDL 程序. 检测串行输入的数据序列中是否有目标序列5'b10010, 检测到指定序列后, 用一个端口输出高电平表示.(2) 编写配套的测试基准.(3) 通过 QuartusII 编译下载到目标 FPGA器件中进行验证.(4) 自行选择合适的模式2试验程序:module e15d1_seqdet( x, z, clk, rst);input x,clk, rst;output z;reg [2:0] state;wire z;parameter IDLE = 3 'd0,A = 3'd1,B = 3'd2,C = 3'd3,D = 3'd4,E = 3'd5,F = 3'd6,G = 3'd7;assign z =(state==D && x==0)?1:0;always @(posedge clk or negedge rst)if(!rst)beginstate<=IDLE;endelsecasex(state)IDLE: if(x==1)state<=A;else state<=IDLE;A: if (x==0)state<=B;else state<=A;B: if (x==0)state<=C;else state<=F;C: if(x==1)state<=D;else state<=G;D: if(x==0)state<=E;else state<=A;E: if(x==0)state<=C;else state<=A;F: if(x==1)state<=A;else state<=B;G: if(x==1)state<=F;else state <=G;default: state<=IDLE;endcaseendmodule3测试基准:`include"e15d1_seqdet.v"`timescale 1ns/1ns`define halfperiod 20module e15d1_seqdet_tb;reg clk, rst;reg [23:0] data;wire z;reg x;initialbeginclk =0;rst =1;#2 rst =0;#30 rst =1;data= 20 'b1100_1001_0000_1001_0100;#(`halfperiod*1000) $stop;endalways #(`halfperiod) clk=~clk;always @ (posedge clk)begin#2 data={data[22:0],data[23]};x=data[23];ende15d1_seqdet m(.x(x),.z(z),.clk(clk),.rst(rst)); endmodule4仿真波形:。

verilog实验报告

verilog实验报告Verilog实验报告引言:Verilog是一种硬件描述语言(HDL),用于设计和模拟数字电路。

它是一种高级语言,能够描述电路的行为和结构,方便工程师进行数字电路设计和验证。

本实验报告将介绍我在学习Verilog过程中进行的实验内容和所获得的结果。

实验一:基本门电路设计在这个实验中,我使用Verilog设计了基本的逻辑门电路,包括与门、或门和非门。

通过使用Verilog的模块化设计,我能够轻松地创建和组合这些门电路,以实现更复杂的功能。

我首先创建了一个与门电路的模块,定义了输入和输出端口,并使用逻辑运算符和条件语句实现了与门的功能。

然后,我创建了一个测试模块,用于验证与门的正确性。

通过输入不同的组合,我能够验证与门的输出是否符合预期。

接下来,我按照同样的方法设计了或门和非门电路,并进行了相应的测试。

通过这个实验,我不仅学会了使用Verilog进行基本门电路的设计,还加深了对逻辑电路的理解。

实验二:时序电路设计在这个实验中,我学习了如何使用Verilog设计时序电路,例如寄存器和计数器。

时序电路是一种具有状态和时钟输入的电路,能够根据时钟信号的变化来改变其输出。

我首先设计了一个简单的寄存器模块,使用触发器和组合逻辑电路实现了数据的存储和传输功能。

然后,我创建了一个测试模块,用于验证寄存器的正确性。

通过输入不同的数据和时钟信号,我能够观察到寄存器的输出是否正确。

接下来,我设计了一个计数器模块,使用寄存器和加法电路实现了计数功能。

我还添加了一个复位输入,用于将计数器的值重置为初始状态。

通过测试模块,我能够验证计数器在不同的时钟周期内是否正确地进行计数。

通过这个实验,我不仅学会了使用Verilog设计时序电路,还加深了对触发器、寄存器和计数器的理解。

实验三:组合电路设计在这个实验中,我学习了如何使用Verilog设计组合电路,例如多路选择器和加法器。

组合电路是一种没有状态和时钟输入的电路,其输出只取决于当前的输入。

Verilog实验报告

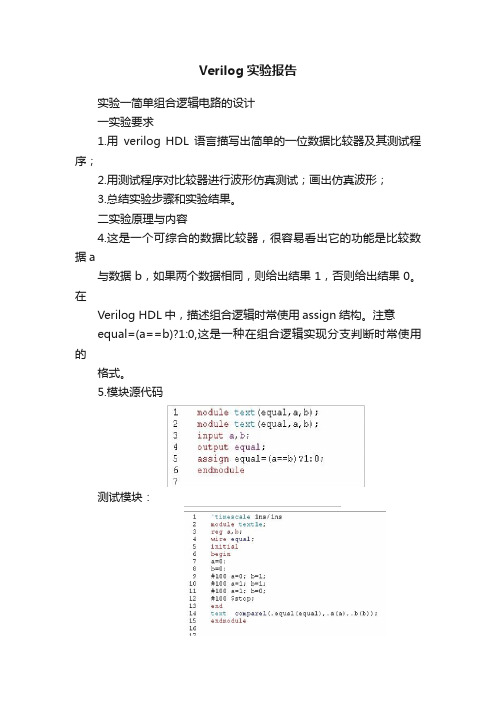

Verilog实验报告实验一简单组合逻辑电路的设计一实验要求1.用verilog HDL语言描写出简单的一位数据比较器及其测试程序;2.用测试程序对比较器进行波形仿真测试;画出仿真波形;3.总结实验步骤和实验结果。

二实验原理与内容4.这是一个可综合的数据比较器,很容易看出它的功能是比较数据a与数据b,如果两个数据相同,则给出结果1,否则给出结果0。

在Verilog HDL中,描述组合逻辑时常使用assign结构。

注意equal=(a==b)?1:0,这是一种在组合逻辑实现分支判断时常使用的格式。

5.模块源代码测试模块:6.波形图:四结实验步骤和实验结果由图可看出,每当输入的电位值不同时输出为0,这与实验要求一致,相同时输出为1,故此程序是可行的。

实验三在verilog HDL中使用函数一实验要求1.掌握函数在模块中的使用2.用测试程序进行波形仿真测试;画出仿真波形3.总结实验步骤和实验结果二实验原理与内容与一般的程序设计语言一样;verilog HDL也可以使用函数已是应对不同变量采取同一运算的操作。

verilog HDL函数在综合时被理解成具有独立运算功能的电路,每调用一次函数相当于改变这部分电路的输入以得到相应的计算结果。

模块源代码:module ex3(clk,n,result,reset);output[31:0] result;input[3:0] n;input reset,clk;reg[31:0] result;always @(posedge clk)beginif(!reset)result <= 0;elsebeginresult <= n*factorial(n)/((n*2)+1);endendfunction[31:0] factorial;input[3:0] operand;reg[3:0] index;beginfactorial = operand ? 1:0;for(index = 2;index <= operand;index = index+1) factorial = index*factorial;endendfunctionendmodule`timescale 1ns/100ps`define clk_cycle 50module ex3_t();reg[3:0] n,i;reg reset,clk;wire[31:0] result;initialbeginn=0;reset=1;clk=0;#100 reset=0;#100 reset = 1;for(i=0;i <= 15;i=i+1)begin#200 n=i;end#100 $stop;endalways #`clk_cycle clk =~ clk;ex3 ex30(.clk(clk),.n(n),.result(result),.reset(reset)); always @(negedge clk)$display("at n=%d,result=%d",n,result);endmodule波形图:实验四在verilog HDL中使用任务一实验要求1.掌握任务在结构化verilog HDL设计中的应用2.用测试程序进行波形仿真测试;画出仿真波形3.总结实验步骤和实验结果二实验原理与内容仅有函数并不能满足verilog HDL中的运算需求。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

verilog hdl实验报告

《Verilog HDL实验报告》

Verilog HDL(硬件描述语言)是一种用于描述电子系统的硬件的语言,它被广泛应用于数字电路设计和硬件描述。

本实验报告将介绍Verilog HDL的基本概念和使用方法,并通过实验展示其在数字电路设计中的应用。

实验目的:

1. 了解Verilog HDL的基本语法和结构

2. 掌握Verilog HDL的模块化设计方法

3. 熟悉Verilog HDL的仿真和综合工具的使用

实验内容:

1. Verilog HDL的基本语法和结构

Verilog HDL是一种硬件描述语言,其语法和结构类似于C语言。

它包括模块定义、端口声明、信号赋值等基本元素。

在本实验中,我们将学习如何定义Verilog模块,并使用端口声明和信号赋值描述数字电路的行为。

2. Verilog HDL的模块化设计方法

Verilog HDL支持模块化设计,可以将复杂的电路分解为多个模块,每个模块描述一个子电路的行为。

在本实验中,我们将学习如何设计和实现Verilog模块,并将多个模块组合成一个完整的数字电路。

3. Verilog HDL的仿真和综合工具的使用

Verilog HDL可以通过仿真工具进行功能验证,也可以通过综合工具生成实际的硬件电路。

在本实验中,我们将使用Verilog仿真工具对设计的数字电路进行功能验证,并使用综合工具生成对应的硬件电路。

实验步骤:

1. 学习Verilog HDL的基本语法和结构

2. 设计一个简单的数字电路,并实现Verilog模块描述其行为

3. 使用仿真工具对设计的数字电路进行功能验证

4. 使用综合工具生成对应的硬件电路

实验结果:

通过本实验,我们学习了Verilog HDL的基本概念和使用方法,并成功设计和实现了一个简单的数字电路。

我们使用仿真工具对设计的数字电路进行了功能验证,并使用综合工具生成了对应的硬件电路。

实验结果表明,Verilog HDL在数字电路设计中具有重要的应用价值。

结论:

Verilog HDL是一种强大的硬件描述语言,它可以帮助工程师们更好地描述和设计数字电路。

通过本实验,我们对Verilog HDL有了更深入的理解,并掌握了其在数字电路设计中的应用方法。

希望通过本实验报告的学习,读者们能够更好地掌握Verilog HDL的使用技巧,为自己的数字电路设计工作提供更多的帮助和支持。