verilog实验60进制计数器

VHDL60进制计数器加法器设计实验

实验四、计数器设计实验1、实验目的1)学习计数器不同设计方法。

2)学习掌握VHDL中不同输出类型在具体应用时的区别(OUT、INOUT、BUFFER)。

3)学习掌握时序电路仿真方法。

2、实验内容1)采用VHDL设计方法,设计一个60进制计数器,采用BCD码输出。

2)给出上述设计的仿真结果。

3、实验设备1)清华同方PⅣ2.4G\256M60G2)ISE 6.2i—Windows软件系统4、实验步骤1)创建工程2)VHDL输入3)检查语法4)建立测试激励波形进行仿真5、实验程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY COUNT ISPORT( CLK,EN,CR :IN STD_LOGIC;LD :IN STD_LOGIC;D :IN STD_LOGIC_VECTOR(7 DOWNTO 0); CO :OUT STD_LOGIC;Q :OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); END COUNT;ARCHITECTURE A OF COUNT ISSIGNAL QN :STD_LOGIC_VECTOR(7 DOWNTO 0);BEGINCO<='1' WHEN(QN=X"59" AND EN='1')ELSE'0';PROCESS(CLK,CR)BEGINIF(CR='0')THENQN<=X"00";ELSEIF(CLK'EVENT AND CLK='1') THENIF (LD='0') THENQN<=D;ELSIF(EN='1') THENIF QN(3 DOWNTO 0)=9 THENQN(3 DOWNTO 0)<="0000";IF QN(7 DOWNTO 4)=5 THENQN(7 DOWNTO 4)<="0000";ELSEQN(7 DOWNTO 4)<= QN(7 DOWNTO 4)+1;END IF;ELSEQN(3 DOWNTO 0)<= QN(3 DOWNTO 0)+1;END IF ;END IF;END IF ;END IF;END PROCESS;Q<=QN;END A;6、仿真结果1)测试激励波形 2)仿真结果从仿真结果来看输出q从00000000逐渐加1变化到01011001,然后又变回到00000000,由此可以看出上述电路完成了六十进制计数器的功能。

实验60进制计数器

实验六60进制计数器

实验目的:

掌握集成计数器、译码器和七段显示器应用。

实验任务:

用2片4bit计数器实现一个带数码显示的60进制计数器。

提示:高4bit计数器输出送给一个数码管显示,低4bit计数器输出送给一个数码管显示。

CP脉冲接Basys2板载1Hz时钟。

实验原理:

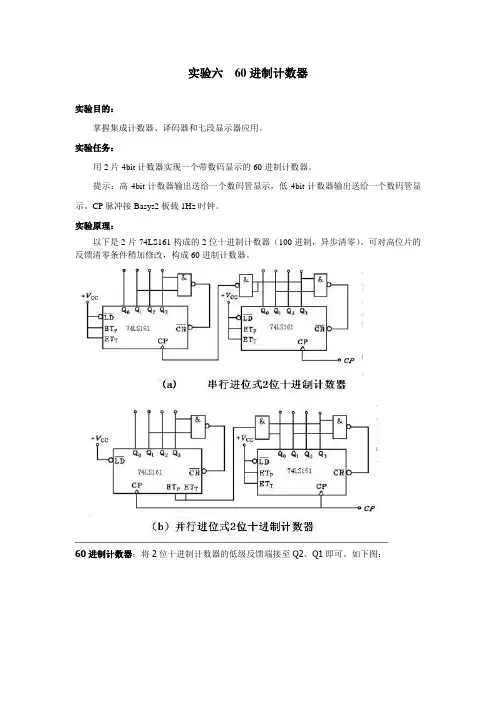

以下是2片74LS161构成的2位十进制计数器(100进制,异步清零)。

可对高位片的反馈清零条件稍加修改,构成60进制计数器。

60进制计数器:将2位十进制计数器的低级反馈端接至Q2、Q1即可。

如下图:

实验要求:

1,进行60进制计数显示实验,记录现象,完成实验报告;

2,相关代码烧录到Basys2板子的PROM中,使得该计数器可脱离电脑的ISE环境。

即Basys2掉电后,恢复供电,仍能够自行运行计数程序。

思考题:如何用8bit计数器构成60进制计数器。

verilog实现60计数器

input load,clk,reset;input[7:0] data;

output reg[7:0] qout; output cout;

always @(posedge clk)

begin

if(reset) qout<=0;

count60 mycount(qout,cout,data,load,reset,clk);

always #(DELY/2) clk=~clk;

initial

begin clk=0;reset=0 ;load=0 ;data=58;

#DELY reset=1;

#DELY reset=0;

#DELY load=1;

end

end

assign cout=(qout==8'd59)?1:0;

endmodule

`include "count60.v"

module count;

reg clk,reset,load;

reg[7:0] data;

wire [7:0]qout;

wire cout;

parameter DELY=100;

verilog实现60计数器 modulecount60(qout,cout,data,load,reset,clk); input load,clk,reset;input[7:0] data; output reg[7:0] qout; output cout; always @(posedge clk) begin if(reset) qout<=0; else if(load) qout<=data; else begin if(qout[3:0]==9) begin qout[3:0]<=0; if(qout[7:4]==5) qout[7:4]<=0; else qout[7:4]<=qout[7:4]+1; end else qout[3:0]<=qout[3:0]+1; end end assign cout=(qout==8?d59)?1:0; endmodule `include "count60.v" module count; reg clk,reset,load; reg[7:0] data; wire [7:0]qout; wire cout; parameter dely=100; count60 mycount(qout,cout,data,load,reset,clk); always #(dely/2) clk=~clk; initial begin clk=0;reset=0 ;load=0 ;data=58; #dely reset=1; #dely reset=0; #dely load=1; #dely load=0; #(dely*60) $finish; end initial $monitor($time,,,"clk=%d reset=%d load=%d qout=%d cout=%d clk,reset,load,cout,qout);endmodule `timescale 1ns/1ns `include "vote.v" module vote; reg wirepass; parameter dely=100; vote vt(a,b,c,pass); initial begin #dely$finish; end initial $monitor($time,,,"a=%b pass=%b",a,b,c,pass);endmodule crx110

VHDL 六十进制计数器

use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity count60 isport(clk,clk0,cin,bcd1wr,bcdswr:in std_logic;datain:in std_logic_vector(3 downto 0);co:out std_logic;a,b,c,d,e,f,g: out std_logic;sel:out std_logic_vector(2 to 0));end count60;architecture art of count60 issignal bcd1n:std_logic_vector(3 downto 0); signal bcdsn:std_logic_vector(2 downto 0); signal outda:std_logic_vector(6 downto 0);beginprocess(clk,bcd1wr)beginif(bcd1wr='1') thenbcd1n<=datain;elsif(clk'event and clk='1') thenif(cin='1') thenif(bcd1n=9) thenbcd1n<="0000";elsebcd1n<=bcd1n+1;end if;end if;end if;end process;process(clk,bcdswr)beginif(bcdswr='1') thenbcdsn<=datain(2 downto 0);elsif(clk'event and clk='1') thenif(cin='1' and bcd1n=9) thenif(bcdsn=5) thenbcdsn<="000";else bcdsn<=bcdsn+1;end if;end if;end if;process(bcd1n,bcdsn,cin)beginif(bcd1n=9 and bcdsn=5 and cin='1') thenco<='1';elseco<='0';end if;end process;process(clk0,bcd1n,bcdsn)beginif clk0='1' then sel<="000";case bcd1n iswhen "0000"=>outda<="1111110";when "0001"=>outda<="0110000";when "0010"=>outda<="1101101";when "0011"=>outda<="1111001";when "0100"=>outda<="0110011";when "0101"=>outda<="1011011";when "0110"=>outda<="1011111";when "0111"=>outda<="1110000";when "1000"=>outda<="1111111";when "1001"=>outda<="1111011";when others=>outda<="0000000";end case;else sel<="110";case bcdsn iswhen "000"=>outda<="1111110";when "001"=>outda<="0110000";when "010"=>outda<="1101101";when "011"=>outda<="1111001";when "100"=>outda<="0110011";when "101"=>outda<="1011011";when others=>outda<="0000000";end case;end if;a<=outda(6);b<=outda(5);c<=outda(4);d<=outda(3);e<=outda(2);f<=outda(1);g<=outda(0);end process;end art;。

VHDL写的60进制计数器

VHDL写的60进制计数器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY COUNTC ISPORT(CLK,CLK0,R,BCD1WR,BCD10WR:IN STD_LOGIC;A:IN STD_LOGIC_VECTOR(3 DOWNTO 0);Y:OUT STD_LOGIC_VECTOR(6 DOWNTO 0);SEL:OUT STD_LOGIC_VECTOR(2 DOWNTO 0));END COUNTC;ARCHITECTURE ONE OF COUNTC ISSIGNAL BCD1N:STD_LOGIC_VECTOR(3 DOWNTO 0); SIGNAL BCD10N:STD_LOGIC_VECTOR(2 DOWNTO 0); BEGINP1:PROCESS(CLK,BCD1WR)BEGINIF R='1' THENBCD1N<="0000";ELSIF BCD1WR='1' THENBCD1N<=A;ELSIF CLK'EVENT AND CLK='1' THENIF BCD1N="1001" THENBCD1N<="0000";ELSE BCD1N<=BCD1N+1;END IF;END IF;END PROCESS P1;P2:PROCESS(CLK,BCD10WR)BEGINIF R='1' THENBCD10N<="000";ELSIF BCD10WR='1' THENBCD10N<=A(2 DOWNTO 0);ELSIF CLK'EVENT AND CLK = '1' THENIF(BCD1N = "1001") THENIF BCD10N="101" THENBCD10N<="000";ELSE BCD10N<=BCD10N+1;END IF;END IF;END IF;END PROCESS P2;P3:PROCESS(CLK0,BCD1N,BCD10N) BEGINIF CLK0 = '1' THENSEL <= "001";CASE BCD1N ISWHEN "0000"=>Y<="0111111"; WHEN "0001"=>Y<="0000110"; WHEN "0010"=>Y<="1011011"; WHEN "0011"=>Y<="1001111"; WHEN "0100"=>Y<="1100110"; WHEN "0101"=>Y<="1101101"; WHEN "0110"=>Y<="1111101"; WHEN "0111"=>Y<="0000111"; WHEN "1000"=>Y<="1111111"; WHEN "1001"=>Y<="1101111"; WHEN "1010"=>Y<="1110111"; WHEN "1011"=>Y<="1111100"; WHEN "1100"=>Y<="0111001"; WHEN "1101"=>Y<="1011110"; WHEN "1110"=>Y<="1111001"; WHEN "1111"=>Y<="1110001"; WHEN OTHERS => NULL;END CASE;ELSE SEL <="010";CASE BCD10N ISWHEN "000"=>Y<="0111111"; WHEN "001"=>Y<="0000110"; WHEN "010"=>Y<="1011011"; WHEN "011"=>Y<="1001111"; WHEN "100"=>Y<="1100110"; WHEN "101"=>Y<="1101101"; WHEN "110"=>Y<="1111101"; WHEN "111"=>Y<="0000111"; WHEN OTHERS => NULL;END CASE;END IF;END PROCESS P3;END ONE;。

60进制计数器verilog原理

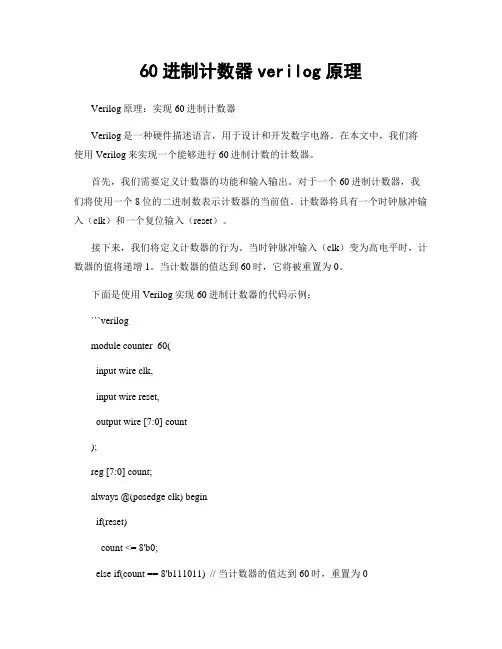

60进制计数器verilog原理Verilog原理:实现60进制计数器Verilog是一种硬件描述语言,用于设计和开发数字电路。

在本文中,我们将使用Verilog来实现一个能够进行60进制计数的计数器。

首先,我们需要定义计数器的功能和输入输出。

对于一个60进制计数器,我们将使用一个8位的二进制数表示计数器的当前值。

计数器将具有一个时钟脉冲输入(clk)和一个复位输入(reset)。

接下来,我们将定义计数器的行为。

当时钟脉冲输入(clk)变为高电平时,计数器的值将递增1。

当计数器的值达到60时,它将被重置为0。

下面是使用Verilog实现60进制计数器的代码示例:```verilogmodule counter_60(input wire clk,input wire reset,output wire [7:0] count);reg [7:0] count;always @(posedge clk) beginif(reset)count <= 8'b0;else if(count == 8'b111011) // 当计数器的值达到60时,重置为0count <= 8'b0;elsecount <= count + 1;endendmodule```以上代码中,我们使用`reg`关键字声明了一个8位的寄存器`count`,用于存储计数器的当前值。

`always @(posedge clk)`表示在时钟上升沿触发时执行以下代码块。

在代码块中,我们首先检查复位信号(reset)是否为高电平。

如果是,计数器的值将被重置为0。

接下来,我们使用一个条件语句判断计数器的值是否为59(8'b111011)。

如果是,计数器的值将重置为0。

否则,计数器的值递增1。

最后,我们将计数器的值作为输出wire `count`进行输出。

通过将以上代码编译为Verilog硬件描述语言的通用代码格式,我们可以在FPGA或ASIC芯片上实现一个用于60进制计数的计数器。

60计数器实验报告

VHDL语言的英文全名是Very High Speed Integrated Circuit Hardware Description Language,即超高速集成电 路硬件描述语言.HDL发展的技术源头是:在HDL形成发展之 前,已有了许多程序设计语言,如汇

以HDL语言表达设计意图,以FPGA作为硬件实现载体,以计算机为设计开发工具,以EDA软件为开发环境的现代电 子设计方法日趋成熟.在这里,笔者认为,要振兴我国电子产 业,需要各相关专业的人士共同努力.HDL语言的语法语义学 研究与半导体工艺相关联的编译映射关系的研究,深亚微米 半导体工艺与EDA设计工具的仿真,验证及方法的研究,这需 要半导体专家和操作系统专家共同努力,以便能开发出更加 先进的EDA工具软件.软件,硬件协同开发缩短了电子设计周 期,加速了电子产品更新换代的步伐.毫不夸张地说,EDA工 程是电子产业的心脏起搏器,是电子产业飞速发展的原动力 本书从应用的角度向国内广大读者介绍VHDL编程技术,让大

编,C,Pascal,Fortran,Prolog等.这些语言运行在不同

硬件平台和不同的操作环境中,它们适合于描述过程和算法 不适合作硬件描述.CAD的出现,使人们可以利用计算机进行 建筑,服装等行业的辅助设计,电子辅助设计也同步发展起 来.在从CAD工具到EDA工具的进化过程中,电子设计工具的 人机界面能力越来越高.在利用EDA工具进行电子设计时,逻 辑图,分立电子原件作为整个越来越复杂的电子系统的设计 已不适应.任何一种EDA工具,都需要一种硬件描述语言来作 为EDA工具的工作语言.这些众多的EDA工具软件开发者,各 自推出了自己的HDL语言.

电子设计自动化(electronic design automation,EDA)技术的理论基础,设计工具,设计器件应是这样的关系:设计 师用硬件描述语言HDL描绘出硬件的结构或硬件的行为,再 用设计工具将这些描述综合映射成与半导体工艺有关的硬 件配置文件,半导体器件FPGA则是这些硬件配置文件的载体 当这些FPGA器件加载,配置上不同的文件时,这个器件便具 有了相应的功能.在这一系列的设计,综合,仿真,验证,配置 的过程中,现代电子设计理论和现代电子设计方法贯穿于其 中.

六十进制计数器

实验五考核实验——六十进制计数

一、实验目的

1、了解可编程数字系统设计的流程

2、掌握Quartus II 软件的使用方法

3、掌握Quartus II 软件的使用方法

4、掌握Quartus II 软件的使用方法

二、实验设备

1、计算机:Quartus II 软件

2、掌握Quartus II 软件的使用方法

3、集成电路:74LS161,任意与非门等。

三、实验原理

1、74LS161:异步清零、同步置数四位二进制计数器

2、引脚定义

3、74LS161功能表

四、实验内容

1、实现60进制计数,计数器用74LS161(2片),其它器件任选

2、七段码显示00、01、02、03 、…、57、58、59

要求:

(1)用原理图输入方式完成

(2)给出仿真波形

(3)计数脉冲CLK接BUTTON0,计数结果接7段码HEX1和HEX0显示

五、实验结果

1、实验原理图:

2、实验波形仿真图

3、引脚分配图

六、实验心得

1、同步异步计数器区分:同步计数器的触发信号是同一个信号。

具体来说,每一级的触发器接的都是同一个CLK信号。

异步计数器的触发信号时不同的,例如第一集的输出Q'作为第二级的触发信号。

几进制的区分:看数据输出端得接线方法,当接线满足拿个计数时会导致“清零”端或者是“置数端”满足工作状态。

2、异步计数器中第二级如果采用置数法,就需要置数的时候给该级提供相应的时钟信号,否则不能完成置数。

EDA硬件描述语言训练——60进制计数器设计

实验题目:硬件描述语言训练—计数器设计一、设计任务:1、用VHDL语言实现一个六十禁止计数器,该计数器有计数允许端EN,清零端CLR和进位输出端CY。

档EN=1时,计数器正常计数;当CLR=1时,计数器清零。

2、将上述计数器下载到FPGA芯片中,利用实验板验证电路的正确性。

二、设计过程:1、设计思路:当“CLR=1且EN=0”时,qh,ql置零,即“qh=0000,ql=0000”。

当“CLR=0且en=1,clk=1”时,ql<=ql+1;若ql=1001,则ql=0000,qh<=qh+1;若qh=0101,则qh<=qh+1。

2、设计方案:将列写出的状态转换图用VHDL语言表达出来,设计好相应的输入输出端口及功能过程,进行设计处理,编译文件,修改其中的错误,再用波形图进行编辑仿真描述,以便检查其功能是否正确,最后下载链接到硬件设备上检查其功能。

3、设计步骤:(1)、列出各输入端口的功能:表1 六十进制计数器输入端口功能表(3)、配置芯片并下载。

先进行引脚的锁定,定义输入输出端口对应芯片上的引脚,然后将实验开发板与PC机通过JTAG下载电缆连接,并通电,拨动开关就检查数据选择器的相关功能。

4、程序:libraryieee;use ieee.std_logic_1164.all;useieee.std_logic_unsigned.all;entityjsq isport(clk,clr,en:instd_logic;cy:outstd_logic;qh,ql:bufferstd_logic_vector(3 downto 0));endjsq;architecture behave of jsq isbegincy<='1' when(qh="0101" and ql="1001") else '0';process(clk,clr,en)beginif(clr='0' or en='1') thenqh<="0000";ql<="0000";elsif (clk'event and clk='1') thenif (ql=9) then ql<="0000";if (qh=5) then qh<="0000";else qh<=qh+1;end if;else ql<=ql+1;end if;end if;end process;end behave;三、结论:仿真波形图:图1 六十进制计数器波形图芯片资源占用情况:图2 六十进制计数器芯片资源占用情况图四、总结:1、VHDL语言中对时序逻辑电路的基本描述:(1)、process中列出时钟信号:process (时钟信号名)beginif(时钟信号变化条件)then顺序语句;end if;end process;时钟信号上升沿:if (clk' event andclk= '1' ) then …wait untilrising_edge (clk);时钟信号下降沿:if clk' event and clk= '0' then …wait untilfalling_edge (clk)(2)、同步复位信号:process (复位信号名,时钟信号名)beginif(时钟信号变化条件)thenif (复位信号变化条件) then状态复位语句;else顺序语句;end if;end if;end process;(3)、异步复位信号:process (复位信号名,时钟信号名)beginif (复位信号变化条件) then状态复位语句;elsif(时钟信号变化条件)then顺序语句;end if;end process;2、VHDL语言描述时序逻辑电路的基本步骤:1、根据实验的具体要求列出输入端口的功能表和状态转换图。

数字电子实验——60进制计数器

综合性、设计性实验报告电子技术实验(数字电子部分)报告分数:学期:班级:姓名:日期:1. 实验目的1)学习仿真软件Multisim的使用方法;2)学习、掌握时序电路的设计方法;3)掌握常用电子元器件的使用方法;4)熟练运用用已有集成计数器(M进制)构成任意进制计数器(N进制),M < N 时,多片级联实现的方法;5)熟悉由555定时器构成的多谐振荡器产生时钟脉冲;6)了解反馈置数法和反馈清零法的特点及区别,并能熟练运用这两种方法。

2. 预习要求1)阅读《数字电子技术基础》相关内容,了解集成计数器的原理及功能;2)熟悉集成计数器74LS161及七段数码显示管的各引脚功能;3)了解555定时器构成的多谐振荡器产生脉冲的基本原理;4)对于反馈清零法和反馈置数法有基本的了解。

3. 实验内容1)在Multisim集成环境中用74LS161和555定时器设计60进制计数器,要求能够实现暂停和置数的功能,并完成其仿真;2)在模块化电子技术综合实验箱上完成电路搭接与调试;4. 实验原理4.1 个位模块(1)利用反馈置数法,U2(74LS161D)为低位片即个位模块,用A、B、C、D四个输入端的高低电平实现个位预置数;(2)用开关控制U2的EP使能端高低电平实现暂停功能;(3)U2的CP脉冲端连接555定时器构成的多谐振荡器的矩形脉冲输出端;(4)U2的使能端ET始终接有效的高电平,清零端CR始终接无效的高电平;因为用的是反馈置数法,U2实现0(0000)~9(1001)的十进制循环,U2的QD和QA段用作二输入与非门U5A(74LS00D)的输入端,其输出端连接到U2的LD上。

(5)U2的四个输出端QD、QC、QB、QA连接U4数码管的D、C、B、A输入端,从而显示0~9这十个状态。

图1 个位模块原理图4.2 十位模块(1)利用反馈置数法,U1(74LS161D)为高位片即十位模块,用A、B、C 三个输入端的高低电平实现十位预置数;(2)U1的CP脉冲端连接555定时器构成的多谐振荡器的矩形脉冲输出端;(3)U1的使能端ET、EP始终接有效的高电平,清零端CR始终接无效的高电平;(4)因为用的是反馈置数法,U1实现0(0000)~5(0101)的六进制循环,U1的QC和QA端与个位数的QD和QA端用作四输入与非门U6A(74LS20D)的输入端,其输出端连接到U1的LD上。