课程设计基于FPGA的半整数分频器设计

FPGA_ASIC-基于CPLD、FPGA的半整数分频器的设计

基于CPLD/FPGA的半整数分频器的设计王蓉 李伟民(九江职业技术学院,江西 九江 332007)摘要:简要介绍了CPLD/FPGA器件的特点和应用范围,并以分频比为2.5和1.5的分频器的设计为例,介绍了在MaxPlusII开发软件下,利用VHDL硬件描述语言以及原理图的输入方式来设计数字逻辑电路的过程和方法。

该设计具有结构简单、实现方便、便于系统升级的特点。

关键词:FPGA; 2.5分频器 ;1.5分频器;半整数分频器。

中图分类号:TN772 文献标识码:B 文章编号:The design of the Half-integer Frequency Divider Based on CPLD/FPGAWANG RONG LI Wei-min(Jiujiang V ocational & Technical College ,Jiujiang City ,Jiangxi Province ,332007) Abstract: Introduced briefly the CPLD/FPGA component characteristic and the application scope, and take the frequency division ratio as 2.5 and 1.5 frequency divider designs are examples, introduced under the MaxPlusII development software, designs the numeral logic circuit using the VHDL hardware description language as well as the schematic diagram input way the process and the method.This design has the structure simply, the realization convenient, is advantageous for the characteristic which the system promotes.Keywords: FPGA; 2.5 frequency dividers; 1.5 frequency dividers; Half-integer frequency divider.1 引言FPGA(Field programmable Gates Array,现场可编程门阵列)适合于时序、组合等逻辑电路的应用,具有设计开发周期短、可编程和实现方案容易改动以及质量稳定等特点[1]。

基于FPGA分频器的研究与设计

基于FPGA分频器的设计摘要:分频器是数字系统设计中的基本电路,在复杂数字逻辑电路设计中,根据不同设计的需要,会遇到偶数分频、奇数分频、半整数分频等,有时要求等占空比,也有要求非等占空比。

在同一个设计中有时要求多种形式的分频,通常由计数器或计数器的级联构成各种形式的偶数分频和奇数分频,实现较为简单,但是对半整数分频实现较为困难。

设计师希望有一种比较方便实用的设计方法,根据情况的需要,在实验室就能设计分频器并且可以马上检测使用,只需要更改频率系数而不修改其他器件或是电路板。

因此,本文利用verilog硬件描述语言,通过开发平台,使用FPGA,设计了一种能满足上述情况的通用分频器。

只要在分频器的输入端输入相应的分频系数,就可以得到所需的频率。

关键词:分频器;偶数;奇数;半整数;分频系数;FPGASeparate frequency inverter based on FPGA designAbstract:Points are the frequency of an digital system design, the basic circuit in complex digital logic circuit design, according to different design needs, will meet even points frequency, an odd number of points frequency, half integer points frequency etc, sometimes require 390v, such as the request 390v. In the same design sometimes require multiple forms of points frequency, usually by a counter or counter cascade constitute various forms of the frequency and the odd points even points, to achieve comparatively simple frequency, but half-and-half integer points frequency division frequency realize more difficult. Designers hope to have a more convenient and practical design methods, according to the needs of the laboratory condition, can design points frequency device and can immediately detection using, only need to change frequency coefficients and not modify other device or circuit board. Therefore, this paper use verilog hardware description language, through the development platform, use the FPGA, design a kind of can meet the above situation of practical points frequency device. As long as the frequency of an in points corresponding points input input frequency coefficients, can get frequency required.Keywords: Points, frequency, manometers, Even, Odd, Half an integer, Points frequency coefficients, FPGA目录第一章绪论 (1)1.1 FPGA简介 (1)1.2 选题的意义和目的 (2)1.3 国内外应用现状及研究现状 (3)1.3.1 应用现状 (3)1.3.2 研究现状 (4)1.4 本文组织结构 (5)第二章几类分频器的设计及其分频原理 (7)2.1 偶数倍分频 (7)2.1.1 分频原理 (7)2.1.2 软件简介 (7)2.1.3 软件仿真 (7)2.2 奇数倍分频 (9)2.2.1 分频原理 (9)2.2.2 软件仿真 (10)2.3 半整数分频 (12)2.4 小数分频器 (13)2.4.1 积分分频器 (13)2.4.2 累加器分频 (14)2.4.3 小数分频器的应用 (15)2.5 本章小结 (17)第三章通用分频器的设计 (18)3.1 设计方案 (18)3.1.1 设计方案一 (18)3.1.2 设计方案二 (18)3.2 系统设计 (19)3.2.1 电路工作流程图及部分程序 (20)3.2.2时钟输出流程图及部分程序 (23)3.3 通用分频器的应用 (25)3.3.1 等占空比的奇数分频器 (25)3.3.2 任意占空比的奇、偶数分频 (25)3.3.3 等占空比的偶数分频器 (26)3.3.4 半整数分频器 (26)3.4 本章小结 (26)结论 (27)致谢 (28)参考文献 (29)第一章绪论1.1 FPGA简介FPGA是现场可编程门阵列的简称,是可编程逻辑器件(PLD)问世以来的第四代产品,适合于时序、组合等逻辑电路的应用。

基于FPGA的分频器设计研究

FPGA结课论文学院:专业:班级:姓名:目录1、引言 (3)2、2N分频器的设计 (3)3、任意整数N分频器的设计 (4)4、半整数分频器设计 (5)5、由分频方法直接获得秒脉冲的设计方法 (6)6、总结 (7)基于FPGA的分频器设计)1 引言分频器是数字系统中常用来对某个给定时钟的频率进行再分频,以得到所需之各种信号频率的常用基本电路之一。

广泛应用于工业控制中的变频需要,电声技术的转化等。

基于FPGA 实现的分频电路一般有两种方法:一是使用FPGA 芯片内部提供的锁相环电路,如 ALTERA 提供的 PLL(Phase Locked Loop),Xilinx 提供的 DLL(Delay Locked Loop);二是使用硬件描述语言,如VHDL、Verilog HDL 等。

使用锁相环电路有许多优点,如可以实现倍频、相位偏移、占空比可调等。

但 FPGA 提供的锁相环个数极为有限,不能灵活满足使用要求。

而用硬件描述语言实现的分频电路消耗不多的逻辑单元就可以实现对时钟的操作,具有成本低、灵活可编程等优点。

2 2N分频器的设计分频系数为2N的分频器的实现最简单,可采用二进制加或减法计数器的设计来实现。

计数器可直接从Altera公司提供的宏功能模块LPM中调用,也可文本输入或原理图输入方式构成。

以一个4bit的二进制加法计数器为例进行分析说明。

以原理图输入方式设计四位二进制加法计数器如图1所示,经编译、时序模拟后得到仿真波形如图2所示:图1 四位二进制加法计数器图2 四位二进制加法计数器仿真波形从仿真波形可以看出分别由Q0、Q1、Q2、Q3得到的脉冲波形频率正是时钟信号CP的1/2、1/4、1/8和1/16。

亦即分频系数是2、4、8和16。

假设FPGA的CP所接石英晶体是20MHz,则不同引脚所得到的频率分别为10 MHz、5 MHz、2.5 MHz和1.25 MHz。

由上讨论推广可知,N位二进制计数器输出端的每一位输出信号其占空比为50%,从低到高排列分频系数正好为21、22、23、24……。

基于CPLDFPGA的半整数分频器的设计

基于CPLDFPGA的半整数分频器的设计1 引言在数字逻辑电路设计中,分频器是一种基本电路。

通常用来对某个给定频率进行分频,以得到所需的频率。

整数分频器的实现非常简单,可采用标准的计数器,也可以采用可编程逻辑器件设计实现。

但在某些场合下,时钟源与所需的频率不成整数倍关系,此时可采用小数分频器进行分频。

比如:分频系数为2.5、3.5、7.5等半整数分频器。

笔者在模拟设计频率计脉冲信号时,就用了半整数分频器这样的电路。

由于时钟源信号为50MHz,而电路中需要产生一个20MHz的时钟信号,其分频比为2.5,因此整数分频将不能胜任。

为了解决这一问题,笔者利用VIDL硬件描述语言和原理图输入方式,通过MAX plus II开发软件和ALTERA公司的FLEX系列EPF10K10LC84-4型FPGA方便地完成了半整数分频器电路的设计。

2 小数分频的基本原理小数分频的基本原理是采用脉冲吞吐计数器和锁相环技术先设计两个不同分频比的整数分频器,然后通过控制单位时间内两种分频比出现的不同次数来获得所需要的小数分频值。

如设计一个分频系数为10.1的分频器时,可以将分频器设计成9次10分频,1次11分频,这样总的分频值为:F=(9×10 1×11)/(9 1)=10.1从这种实现方法的特点可以看出,由于分频器的分频值不断改变,因此分频后得到的信号抖动较大。

当分频系数为N-0.5(N为整数)时,可控制扣除脉冲的时间,以使输出成为一个稳定的脉冲频率,而不是一次N分频,一次N-1分频。

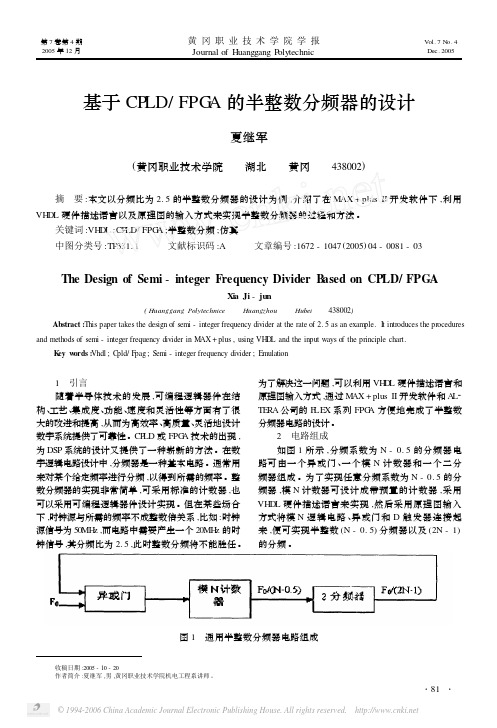

图2 模3计数器仿真波形 3 电路组成分频系数为N-0.5的分频器电路可由一个异或门、一个模N计数器和一个二分频器组成。

在实现时,模N计数器可设计成带预置的计数器,这样可以实现任意分频系数为N-0.5的分频器。

图1给出了通用半整数分频器的电路组成。

采用VHDL硬件描述语言,可实现任意模N的计数器(其工作频率可以达到160MHz以上),并可产生模N逻辑电路。

基于FPGA的半整数分频器的设计

基于FPGA的半整数分频器的设计

高凡;贾磊磊

【期刊名称】《科技信息》

【年(卷),期】2010(000)019

【摘要】简要介绍了FPGA器件的特点和应用范围,并以分频比为7.5的半整数分频器的设计为例,介绍了在MAX+plus Ⅱ开发软件下,利用VHDL硬件描述语言以及原理图的输入方式来设计数字逻辑电路的过程和方法.

【总页数】2页(P133-134)

【作者】高凡;贾磊磊

【作者单位】桂林航天工业高等专科学校,广西,桂林,541004;桂林航天工业高等专科学校,广西,桂林,541004

【正文语种】中文

【相关文献】

1.基于CPLD/FPGA的半整数分频器的设计 [J], 林海波

2.基于FPGA的半整数及整数分频器的参数化设计 [J], 古良玲;杨永明;郭巧惠

3.基于CPLD/FPGA的半整数分频器的设计 [J], 夏继军

4.基于CPLD/FPGA的半整数分频器的设计 [J], 王蓉;李伟民

5.基于CPLD/FPGA的半整数分频器的设计 [J], 汪霞

因版权原因,仅展示原文概要,查看原文内容请购买。

实验5指导书 基于FPGA的分频器的设计

实验5 基于FPGA的分频器设计预习内容阅读《电工电子实验教程》第6.6节中触发器及时序逻辑电路的内容。

预先学习Quartus II软件的使用方法。

预习实验的内容,自拟实验步骤和数据表格,选择使用器件,完成电路设计,画出原理电路,手写预习报告。

一、实验目的1.了解EDA软件在电子设计当中的重要作用。

2.熟悉并掌握Quartus II开发软件的基本使用方法。

3.运用图解法设计分频器电路,并进行电路仿真。

二、知识要点FPGA(Field-Programmable Gate Array)是一种可编程器件,即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。

它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

FPGA主要生产厂商有:Altera、Xilinx、Actel、Lattice。

FPGA的开发软件包括Altera公司的Quartus II、Xilinx 公司的ISE、Lattice 公司的isplever Base。

Quartus II是Altera公司的第四代可编程逻辑器件集成开发环境,提供从设计输入到器件编程的全部功能。

Quartus II可以产生并识别EDIF网表文件、VHDL网表文件和Verilog HDL网表文件,为其它EDA工具提供了方便的接口;可以在Quartus II集成环境中自动运行其它EDA工具。

利用Quartus II软件的开发流程可概括为以下几步:设计输入、设计编译、设计定时分析、设计仿真和器件编程。

用户通过开发软件提供的设计工具实现自己的电路设计以及相应的配置,当用户通过仿真验证结论后,便可把设计下载至FPGA中,实现设定功能。

三、实验内容设计一个分频电路(使用74LS161和必要的门电路)。

要求得到8分频(输出频率为输入频率的八分之一)信号和32分频信号。

基于CPLDFPGA的半整数分频器的设计

基于CP LD/FPG A 的半整数分频器的设计夏继军(黄冈职业技术学院 湖北 黄冈 438002)摘 要:本文以分频比为2.5的半整数分频器的设计为例,介绍了在M AX +plus II 开发软件下,利用VH D L 硬件描述语言以及原理图的输入方式来实现半整数分频器的过程和方法。

关键词:VH D L ;CP LD/FPG A ;半整数分频;仿真中图分类号:TP331.1 文献标识码:A 文章编号:1672-1047(2005)04-0081-03The Design of Semi -integer Frequency Divider B ased on CPLD/FPGAXia Ji -jun(Huanggang Polytechnice Huangzhou Hubei 438002)Abstract :This paper takes the design of semi -integer frequency divider at the rate of 2.5as an example.It introduces the procedures and methods of semi -integer frequency divider in M AX +plus ,using VH D L and the input ways of the principle chart.K ey w ords :Vhdl ;C pld/F pag ;Semi -integer frequency divider ;Emulation 1 引言随着半导体技术的发展,可编程逻辑器件在结构、工艺、集成度、功能、速度和灵活性等方面有了很大的改进和提高,从而为高效率、高质量、灵活地设计数字系统提供了可靠性。

CP LD 或FPG A 技术的出现,为DSP 系统的设计又提供了一种崭新的方法。

在数字逻辑电路设计中,分频器是一种基本电路。

FPGA_ASIC-基于FPGA的通用分频器设计

基于FPGA的通用分频器设计周子昂,王福源,魏军辉(郑州大学信息工程学院,河南郑州450052)摘要:本文介绍了一种能够完成半整数和各种占空比的奇/偶数和的通用的分频器设计,并给出了本设计在Altera公司的FLEX10K系列EPF10K10LC84-3型FPGA芯片中实现后的测试数据和设计硬件的测试结果,结果表明了设计的正确性和可行性。

由于设计采用VHDL硬件描述语言实现,用户可以自行裁减和设置分频器的功能,所以有很广泛的应用价值。

关键词: 通用分频器; 占空比; 半整数;中图分类号:TN772 文献标识码:ADesign of universal frequency divider based on FPGAZHOU zi ang, WANG fu yuan,WEI jun hui(College of information, Zhengzhou University, Zhengzhou, Henan, 450052)Abstract: This paper presents an algorithm for designing a universal frequency divider which can realize different duty cycle either odd and even divider number. Experiments and hardware test onAltera PF10K10LC84-3 chip of FLEX10K series are given to show that the design is successful. Depending on the VHDL realization of this algorithm the design is of design flexibility and widely applications.Keywords: universal frequency divide; half duty cycle; half integer;1.概述分频器是数字系统设计的基本电路。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

课程设计报告设计名称EDA(VHDL)课程设计专业班级电子0942姓名姬鹏冲学号0904451213成绩评定电气与信息工程学院二0一二年一月课程设计要求和成绩考核办法(要求和成绩考核办法在封皮背面打印)1.不允许在教室或实验室内吸烟、吃零食,不准带无关人员到教室或实验室活动,否则扣平时表现分。

2.凡病事假超过3天(每天7小时),或迟到早退三次以上,或旷课两次(1天)以上,不得参加本次考核,按不及格处理,本次课程设计不能通过。

3.病事假必须有请假条,需经班主任或有关领导批准,否则按旷课处理。

4.课程设计的考核由指导教师根据设计表现(出勤、遵守纪律情况等)、设计报告、设计成果、答辩等几个方面,给出各项成绩或权重,综合后给出课程设计总成绩。

该设计考核须经教研室主任审核,主管院长审批备案。

5.成绩评定采用五级分制,即优、良、中、及格和不及格。

6.课程设计结束一周内,指导教师提交成绩和设计总结。

7.设计过程考核和成绩在教师手册中要有记载。

实习报告要求实习报告内容、格式各专业根据实习(设计)类别(技能实习、认识实习、生产实习、毕业实习等)统一规范,经教研室主任审核、主管院长审批备案。

注意:1.课程设计任务书和指导书在课程设计前发给学生,设计任务书放置在设计报告封面后和正文目录前。

2.为了节省纸张,保护环境,便于保管设计报告,统一采用A4纸,课程设计报告建议双面打印(正文采用宋体五号字)或手写,左侧装订,订两个钉。

基于FPGA的半整数分频器设计一、系统设计任务及功能概述本系统是利用VHDL硬件描述语言和原理图输入方式,通过MUX+PLUSⅡ开发软件和ALTER 公司的FLEX系列EPF10K10LC84-4型FPGA方便的完成了半整数分频器电路的设计。

本系统是通过控制单位时间内两种分频比出现的不同次数来获得所需要的小数分频值。

二、系统设计方案和程序设计1.系统设计方案我们采用脉冲吞吐计数器和锁相环技术,先设计两个不同分频比的整数分频器,然后通过控制单位时间内两种分频比出现的不同次数来获得所需要的5.5分频值。

该分频器电路可由一个异或门、一个模6数器和二分频器组成。

这样可以实现分频系数为5.5分频器以及11分频。

设计框图如下所示2.VHDL程序设计(1)模6计数器VHDL描述设计该计数器可产生一个分频系数为5.5分频器,并产生一个默认的逻辑符号cont6。

其输入端口为rst、en和clk;输出端口为qa,qb,qc。

下面给出模6数器的VHDL描述代码:libraryieee;use ieee.std_logic_1164.all;useieee.std_logic_unsigned.all;entity cont6 isport(clk:instd_logic;rst:instd_logic;en:instd_logic;qa,qb,qc:outstd_logic);end entity cont6;architecturewode of cont6 issignalcount:std_logic_vector(2 downto 0);beginprocess(clk,rst,en)isbeginifrst='1'then count<="000";elsifclk'event and clk='1'thenif en='1'thenif count="101" then count<="000";else count<=count+1;end if;end if;end if;end process;qa<=count(0);qb<=count(1);qc<=count(2);end architecture wode;模六计数器原件生成图如下:图一模六计数器原件生成上面的程序经编译、时序模拟在MAX+PLUSⅡ中可得到如图所示的仿真波形:图2模6计数器仿真波形(2)半整数分频器设计现在通过设计一个分频系数为5.5的分频器给出用FPGA设计半整数分频器的一般方法。

该5.5分频器由前面设计的模6计数器、异或门和D触发器组成,利用图形设计方法构造如图所示的5.5分频器电路原理图。

图3 5.5分频器电路原理图3.将cont6、异或门和D触发器通过图3所示的电路建立逻辑连接关系,并用原理图输入方式调入图形编辑器,然后经过逻辑综合即可得到如图4所示的仿真波形。

图4 5.5分频器仿真波形图三.通过用VHDL语言描述模N计数器,然后进行波形仿真,原理图仿真等,了解了半整数分频器的工作原理。

试验中遇到了好多不会的通过查书,请教老师,请教同学一一解决了。

通过这次的实验认识了把课本的知识用到生活实践中,来解决问题很好的培养了自己的动手能力和学习能力。

四.参考文献[1] 谭会生,张昌凡.EDA技术及应用. 西安:西安电子科技大学出版社,2006,12.[2] 郭振武,从红霞。

EDA实验教程. 天津:南开大学出版社,2011,8[3] 杨晓慧,杨永健.基于FPGA的EDA/SOPC技术与VHDL.北京:国防工业出版社,2007,7.[4] 皱其宏 EDA实验技术教程。

北京:中国电力出版社。

2009.5.[5] 陈雪松,滕立中编著.VHDL入门与应用.北京:人民邮电出版社. 2000.99分钟定时器的VHDL设计一.系统设计任务及功能概述1.系统设计任务任务要求:通过设计,定时器可以整体清零;可以定时最高到99MIN;以秒速度递增至预定时间,以秒速度递减至零。

2.系统功能概述本系统是一个99分钟的定时器,具有以下功能:具有整体清零(reset)功能,定时99分钟。

以秒速度递增至99分钟停止,启动报警(cout)5秒钟。

具有置位(cn)控制,即cn高电平时,clk脉冲上升沿到来,计数加一;cn 低电平时,置位结束,进入倒计时阶段,以秒速度使输出计数减一至零结束,并同时报警(cout)5秒钟。

时钟信号提供秒信号(1HZ);四位数码管静态显示,高位high(3 downto 0)显示分,低位low(3 downto 0)显示秒。

二.系统设计方案和程序设计1.系统设计方案通过记数器控制中心输入秒信号,并输出两个四位的BCD码,可分别来表示各位与十位,也可整体复位清零。

通过该记数器实现以秒速度递增至清零,该记数器以秒的速度递增至99来实现置位,而以秒的速度递减至零以实现定时功能。

当以秒速度递增至99分钟停止,启动报警(cout)5秒钟。

cn低电平时,置位结束,进入倒计时阶段,以秒速度使输出计数减一至零结束时也同时报警(cout)5秒钟。

通过二选一选择器对个位和十位进行扫描输出,并将输出送到译码器,通过译码器对输入的四位BCD码进行七段码编译,然后输出到数码管。

2.VHDL程序设计Aaa控制计数模块,是该定时器的核心部分.res为复位端,用来清零,采用异步复位方式;cn用于置位,高电平有效。

cout端将在定时结束时产生高电平。

Low和high为四位BCD 码输出端口,可用于显示。

当cn有效时,clk脉冲上升沿到来,计数加1;当cn为低电平时,置位结束,进入计时阶段,每1个时钟周期发出一个脉冲,使输出记数减1,直到记时结束,令cout位为高电平为止。

该模块的源程序如下:libraryieee;use ieee.std_logic_1164.all;useieee.std_logic_unsigned.all;entityjsq isport (cn,res,clk:instd_logic;cout :out std_logic;flow,fhigh,mlow,mhigh:outstd_logic_vector(3 downto 0));endjsq;architecture art of jsq issignalfdisplow,fdisphigh,mdisplow,mdisphigh:std_logic_vector(3 downto 0); --定义信号分别表示分钟和秒钟的十位和个位beginprocess(clk,cn,res)beginif(res='1')thenmdisplow<="0000";mdisphigh<="0000";fdisplow<="0000";fdisphigh<="0000";cout<='0'; --res高电平执行复位elsif (clk'event and clk='1')thenifcn='1'thenifmdisplow<9 thenmdisplow<=mdisplow+1;--秒钟个位数小于9时执行计数加1cout<='0';elsifmdisplow="1001" and mdisphigh<5 thenmdisplow<="0000";mdisphigh<=mdisphigh+1;--秒钟十位进位加1elsifmdisphigh="0101" and fdisplow<9 thenmdisplow<="0000";mdisphigh<="0000";fdisplow<=fdisplow+1;--满59秒后分钟个位加1elsiffdisplow="1001" and fdisphigh<9 thenmdisplow<="0000";mdisphigh<="0000";fdisplow<="0000";fdisphigh<=fdisphigh+1;--满9分59秒后分钟十位加1elsiffdisplow="1000" and fdisphigh="1001" thenmdisplow<="0000";mdisphigh<="0000";fdisplow<="1001";--计时至99分停止elsiffdisplow="1001" and fdisphigh="1001" thencout<='1';--计时停止cout变为高电平end if;elsifcn='0' then --cn为0进入倒计时ifmdisplow>0 thenmdisplow<=mdisplow-1;--秒钟减1cout<='0';elsifmdisplow="0000" and mdisphigh>0 thenmdisplow<="1001";mdisphigh<=mdisphigh-1;--个位0时十位减1elsifmdisphigh="0000" and fdisplow>0 thenmdisplow<="1001";mdisphigh<="0101";fdisplow<=fdisplow-1;--分减1elsiffdisplow="0000" and fdisphigh>0 thenmdisplow<="1001";mdisphigh<="0101";fdisplow<="1001";fdisphigh<=fdisphigh-1;--分减10elsiffdisphigh="0000"and fdisplow="0000"and mdisphigh="0000"and mdisplow="0000"thencout<='1';--倒计时结束cout变为高电平end if;end if;end if;end process;mhigh<=mdisphigh;mlow<=mdisplow;fhigh<=fdisphigh;flow<=fdisplow;end art;该计数器生成的原件如下图所示:图一计数器原件生成图计数器波形仿真图如下图所示:图二计数器波形仿真报警器模块:主要功能是计数器以秒速度递增至99分钟停止时启动报警(cout)5秒钟。