(完整版)FPGA课程设计(最终版)

FPGA综合实验期末课程设计

FPGA综合实验期末课程设计一、课程目标知识目标:1. 理解FPGA的基本原理,掌握FPGA芯片的结构、工作流程和编程方法;2. 学会运用硬件描述语言(HDL)进行数字电路设计和验证;3. 掌握FPGA设计中常见的时序分析、资源优化和接口技术;4. 了解FPGA在嵌入式系统、信号处理和人工智能等领域的应用。

技能目标:1. 能够运用所学知识独立完成FPGA基础实验,具备基本的FPGA编程能力;2. 能够运用HDL语言设计简单的数字电路,并进行功能仿真与验证;3. 能够对FPGA设计进行调试和优化,提高数字电路的性能;4. 能够针对实际问题,提出基于FPGA的解决方案,并进行设计和实现。

情感态度价值观目标:1. 培养学生对FPGA技术及电子工程的兴趣,激发学生主动探索新知识的精神;2. 培养学生的团队协作意识和沟通能力,提高学生在项目实践中的合作能力;3. 培养学生严谨的科学态度和良好的工程素养,使学生具备解决实际问题的信心和责任感;4. 引导学生关注FPGA技术在我国科技发展中的应用,激发学生的爱国情怀和科技创新精神。

本课程针对高年级电子信息类专业的学生,结合课程性质、学生特点和教学要求,明确以上课程目标,旨在帮助学生将理论知识与实际应用相结合,提高学生的实践能力和创新能力,为未来从事相关领域工作打下坚实基础。

二、教学内容本章节教学内容主要包括以下几部分:1. FPGA基本原理与结构:介绍FPGA的发展历程、基本组成、工作原理以及编程模型,结合课本第二章内容进行讲解。

2. 硬件描述语言(HDL):学习Verilog和VHDL两种硬件描述语言的基础知识,包括语法、数据类型、运算符等,参考课本第三章内容。

3. 数字电路设计:运用HDL语言设计组合逻辑电路和时序逻辑电路,进行功能仿真与验证,结合课本第四章内容。

4. FPGA设计流程:介绍FPGA设计的整个流程,包括设计输入、综合、布局布线、仿真和下载等,以课本第五章为参考。

FPGA课程设计

FPGA课程论文学生姓名学号院系指导教师二O一O年六月七日一、硬件语言描述1. Verilog HDL简介Verilog HDL是一种硬件描述语言,用于从算法级、门级到开关级的多种抽象设计层次的数字系统建模。

被建模的数字系统对象的复杂性可以介于简单的门和完整的电子数字系统之间。

数字系统能够按层次描述,并可在相同描述中显式地进行时序建模。

Verilog HDL 语言具有下述描述能力:设计的行为特性、设计的数据流特性、设计的结构组成以及包含响应监控和设计验证方面的时延和波形产生机制。

所有这些都使用同一种建模语言。

此外,Verilog HDL语言提供了编程语言接口,通过该接口可以在模拟、验证期间从设计外部访问设计,包括模拟的具体控制和运行。

Verilog HDL语言不仅定义了语法,而且对每个语法结构都定义了清晰的模拟、仿真语义。

因此,用这种语言编写的模型能够使用Verilog仿真器进行验证。

语言从C编程语言中继承了多种操作符和结构。

Verilog HDL提供了扩展的建模能力。

2.Verilog HDL和VHDL的比较Verilog HDL和VHDL都是用于逻辑设计的硬件描述语言,并且都已成为IEEE标准。

VHDL是在1987年成为IEEE标准,Verilog HDL则在1995年才正式成为IEEE标准。

Verilog HDL和VHDL作为描述硬件电路设计的语言,其共同的特点在于:能形式化地抽象表示电路的行为和结构、支持逻辑设计中层次与范围的描述、可借用高级语言的精巧结构来简化电路行为的描述、具有电路仿真与验证机制以保证设计的正确性、支持电路描述由高层到低层的综合转换、硬件描述与实现工艺无关(有关工艺参数可通过语言提供的属性包括进去)、便于文档管理、易于理解和设计重用。

但是Verilog HDL和VHDL又各有其自己的特点。

由于Verilog HDL早在1983年就已推出,至今已有近二十年的应用历史,因而Verilog HDL拥有更广泛的设计群体,成熟的资源也远比VHDL丰富。

fpga技术课程设计

fpga技术课程设计一、教学目标本课程的教学目标分为三个维度:知识目标、技能目标和情感态度价值观目标。

1.知识目标:通过本课程的学习,学生将掌握FPGA技术的基本概念、原理和应用,了解FPGA技术的发展趋势及其在电子工程领域的广泛应用。

2.技能目标:学生将能够熟练使用FPGA开发工具,如ISE、Vivado等,掌握FPGA编程语言,如VHDL、Verilog等,并具备一定的FPGA硬件设计和验证能力。

3.情感态度价值观目标:培养学生对FPGA技术的兴趣和热情,使其认识到了解和掌握FPGA技术对于个人职业发展的重要性,树立正确的科学态度和创新精神。

二、教学内容教学内容将根据课程目标进行选择和,确保内容的科学性和系统性。

教学大纲如下:1.FPGA技术概述:介绍FPGA的基本概念、工作原理和分类,以及FPGA技术的发展历程和趋势。

2.FPGA硬件描述语言:讲解VHDL和Verilog两种主流的FPGA硬件描述语言,包括基本语法、语句结构和常用库函数。

3.FPGA设计与验证:介绍FPGA设计的基本流程,包括设计输入、综合、布局布线和仿真验证等环节。

4.FPGA应用案例:分析典型的FPGA应用案例,如数字信号处理、网络通信、嵌入式系统等,使学生了解FPGA技术在实际工程中的应用。

5.FPGA开发工具:介绍FPGA常用的开发工具,如ISE、Vivado等,以及这些工具的使用方法和技巧。

三、教学方法为了激发学生的学习兴趣和主动性,本课程将采用多种教学方法,包括讲授法、讨论法、案例分析法和实验法等。

1.讲授法:教师通过讲解、演示和举例等方式,向学生传授FPGA技术的基本概念、原理和应用。

2.讨论法:学生针对FPGA技术的相关话题进行讨论,培养学生的思考能力和团队协作精神。

3.案例分析法:分析典型的FPGA应用案例,使学生了解FPGA技术在实际工程中的应用,提高学生的实践能力。

4.实验法:安排学生进行FPGA实验,让学生亲自动手操作,巩固所学知识,提高实际操作能力。

fpga语言的课程设计

fpga语言的课程设计一、课程目标知识目标:1. 理解FPGA的基本概念,掌握FPGA的设计流程和原理;2. 学习并掌握FPGA编程语言(如VHDL/Verilog)的基本语法和结构;3. 掌握FPGA设计中常用的逻辑元件和模块的使用方法;4. 了解FPGA在实际工程中的应用案例,理解其优势和局限性。

技能目标:1. 能够运用FPGA编程语言编写简单的程序代码,实现基本的数字逻辑功能;2. 能够使用FPGA设计软件进行电路设计、仿真和调试;3. 能够分析FPGA设计中的问题和错误,并进行相应的优化和修改;4. 培养学生的动手实践能力,使其能够独立完成简单的FPGA项目设计。

情感态度价值观目标:1. 培养学生对FPGA技术及电子工程的兴趣,激发其探索精神和创新意识;2. 培养学生团队合作意识,学会与他人共同解决问题,提高沟通与协作能力;3. 培养学生严谨、细致的学习态度,养成认真负责、精益求精的工作作风;4. 增强学生的国家意识,认识到FPGA技术在我国电子产业发展中的重要性,激发其为国家技术进步贡献力量的责任感。

二、教学内容1. FPGA基本概念:FPGA的原理、结构、优势与应用领域;教材章节:第一章 概述2. FPGA设计流程:设计输入、综合、布局布线、仿真与实现;教材章节:第二章 设计流程3. FPGA编程语言:VHDL/Verilog基本语法、程序结构、数据类型;教材章节:第三章 编程语言基础4. 常用逻辑元件与模块:逻辑门、触发器、计数器、寄存器等;教材章节:第四章 基本逻辑元件与模块5. 电路设计与仿真:使用FPGA设计软件进行电路设计、仿真和调试;教材章节:第五章 电路设计与仿真6. FPGA项目实践:分析案例,设计并实现简单的数字逻辑功能;教材章节:第六章 项目实践7. 优化与修改:分析FPGA设计中可能出现的问题,进行优化和修改;教材章节:第七章 优化与修改8. 动手实践:指导学生进行实际操作,培养动手实践能力;教材章节:第八章 动手实践教学内容按照以上大纲进行安排,确保课程的科学性和系统性,使学生能够逐步掌握FPGA的设计与应用。

fpga课程设计报告

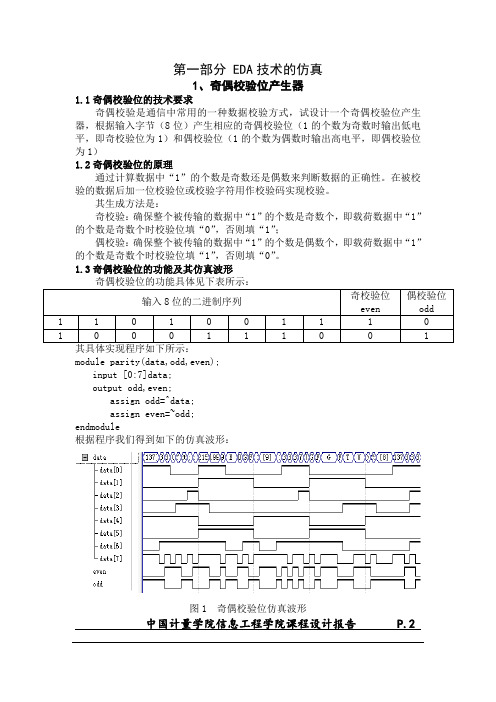

第一部分 EDA技术的仿真1、奇偶校验位产生器1.1奇偶校验位的技术要求奇偶校验是通信中常用的一种数据校验方式,试设计一个奇偶校验位产生器,根据输入字节(8位)产生相应的奇偶校验位(1的个数为奇数时输出低电平,即奇校验位为1)和偶校验位(1的个数为偶数时输出高电平,即偶校验位为1)1.2奇偶校验位的原理通过计算数据中“1”的个数是奇数还是偶数来判断数据的正确性。

在被校验的数据后加一位校验位或校验字符用作校验码实现校验。

其生成方法是:奇校验:确保整个被传输的数据中“1”的个数是奇数个,即载荷数据中“1”的个数是奇数个时校验位填“0”,否则填“1”;偶校验:确保整个被传输的数据中“1”的个数是偶数个,即载荷数据中“1”的个数是奇数个时校验位填“1”,否则填“0”。

1.3奇偶校验位的功能及其仿真波形奇偶校验位的功能具体见下表所示:输入8位的二进制序列奇校验位even偶校验位odd1 1 0 1 0 0 1 1 1 0 1 0 0 0 1 1 1 0 0 1其具体实现程序如下所示:module parity(data,odd,even);input [0:7]data;output odd,even;assign odd=^data;assign even=~odd;endmodule根据程序我们得到如下的仿真波形:图1 奇偶校验位仿真波形中国计量学院信息工程学院课程设计报告P.22、十六位数据选择器2.1数据选择器的原理在多路数据传送过程中,能够根据需要将其中任意一路选出来的电路,叫做数据选择器,数据选择器(MUX)的逻辑功能是在地址选择信号的控制下,从多路数据中选择一路数据作为输出信号。

在数据选择器中,我们设定一个控制输入端ENA ,当ENA=1时,电路不能工作,输出Y=0;而当ENA=0时,电路才处于工作状态。

由于我们设计的是16选1数据选择器,因而其有4个数据控制端,即S0,S1,S2,S3,根据这4个控制端的状态有选择性的输出。

文华学院FPGA课课程设计

文华学院FPGA课课程设计一、教学目标本课程的教学目标是使学生掌握FPGA的基本原理、设计和应用方法。

通过本课程的学习,学生将能够:1.理解FPGA的基本概念、结构和特点。

2.掌握FPGA的设计流程,包括硬件描述语言的编写、逻辑综合、布局布线和编程下载等。

3.熟悉FPGA的应用领域,如数字信号处理、嵌入式系统、网络通信等。

4.培养学生动手实践能力和团队协作精神。

二、教学内容本课程的教学内容主要包括以下几个部分:1.FPGA的基本原理:介绍FPGA的起源、发展历程、工作原理和主要性能指标。

2.FPGA的结构与特点:讲解FPGA的内部结构、编程方式及其与ASIC、ASIP的区别。

3.硬件描述语言(HDL):学习Verilog和VHDL两种常用硬件描述语言的基本语法和编程技巧。

4.FPGA设计流程:熟悉FPGA的设计流程,包括需求分析、硬件描述语言编写、逻辑综合、布局布线和编程下载等。

5.FPGA应用案例:分析数字信号处理、嵌入式系统、网络通信等领域的FPGA应用实例。

6.实践环节:进行FPGA实验,锻炼学生的动手实践能力和实际问题解决能力。

三、教学方法为了达到本课程的教学目标,将采用以下几种教学方法:1.讲授法:讲解FPGA的基本原理、结构和设计方法。

2.案例分析法:分析具体的FPGA应用案例,让学生了解FPGA在实际工程中的应用。

3.实验法:安排FPGA实验,让学生动手实践,巩固所学知识。

4.讨论法:学生进行小组讨论,培养团队协作精神和沟通能力。

四、教学资源为了支持本课程的教学,将准备以下教学资源:1.教材:选用权威、实用的教材,如《FPGA原理与应用》。

2.参考书:提供相关的参考书籍,以便学生深入研究。

3.多媒体资料:制作PPT、视频等多媒体教学资料,丰富教学手段。

4.实验设备:准备FPGA开发板、编程器等实验设备,确保学生能够动手实践。

5.在线资源:推荐一些在线教程、论坛和学术资源,方便学生自主学习。

fpga课程设计

课题一一,设计一个可控的100进制可逆计数器,要求用实验箱下载。

(1)计数器的时钟输入信号周期为200ns。

(2)以十进制形式显示。

(3)有一个复位端clr和两个控制端plus和minus,在这些控制信号的作用下,计数器具有复位、增或减计数、暂停功能。

二,设计思路:由题目可知,可逆计数器有四种工作模式,即清零,加计数,减计数和暂停。

由此,我想到有case语句,这也是整个程序的核心。

三,源代码moduleupdown_count(qout,reset,clk,plus,minus);output[7:0] qout;/*定义一个8位的输出,其目的是低四位和高四位分别表示计数器的个位和十位。

*/input clk,plus,minus,reset;//定义四个输入,时钟,加计数,减计数和清零reg[7:0] qout;//qout的数据类型为寄存器型always @(posedgeclk)//当clk上升沿到来时执行一遍下列程序beginif(!reset) qout<=0;//当reset为低电平时,计数器执行清零功能,否则跳过elsebegincase({minus,plus})//case语句模块,包含加,减和暂停四个模块2'b10:if (qout[3:0]==0)//判断个位是否为零,若不为零,跳到个位减一beginqout[3:0]<=9;//给个位赋值if(qout[7:4]==0) qout[7:4]<=9;//判断十位是否为零,并且给十位赋值elseqout[7:4]<=qout[7:4]-1;//由于个位赋9,相当于向十位借一,因而十位减一endelseqout[3:0]<=qout[3:0]-1;//个位减一/*这一部分是减计数模块,其思路是:首先判断个位是否为零,若为零,则执行后面的程序,个位直接赋9,并且十位减一;否则个位减一*/ 2'b01:if (qout[3:0]==9)//判断个位是否为9,否则跳到个位加一beginqout[3:0]<=0;//若上面个位为9判断成立,则给个位赋值if(qout[7:4]==9) qout[7:4]<=0;//判断十位是否为9,若为9,则赋0elseqout[7:4]<=qout[7:4]+1;//若十位不为9,十位加一endelseqout[3:0]<=qout[3:0]+1;//个位加一/*这一部分是加计数模块,首先判断个位是否为9,若不为9,个位加1;否侧,再判断十位是否为9,若为9,十位赋0,否侧十位加1。

fpga数字系统设计课程设计

fpga数字系统设计课程设计一、课程目标知识目标:1. 掌握FPGA数字系统设计的基本原理,理解数字系统的组成及功能;2. 学会使用硬件描述语言(HDL)进行数字电路设计和描述;3. 了解FPGA器件的结构、编程原理以及配置方法;4. 熟悉数字系统的测试与验证方法,掌握基本故障排查技巧。

技能目标:1. 能够运用所学知识,独立完成简单的数字系统设计;2. 掌握使用FPGA开发工具进行代码编写、仿真和调试;3. 学会使用示波器、逻辑分析仪等仪器进行数字电路测试与分析;4. 提高团队协作能力,学会在项目中分工合作,共同解决问题。

情感态度价值观目标:1. 培养学生对数字系统设计的兴趣,激发创新意识;2. 培养学生严谨的科学态度,养成良好的实验习惯;3. 增强学生的自信心和自主学习能力,培养面对挑战的勇气;4. 提高学生的团队合作意识,学会尊重他人,共同进步。

本课程针对高年级学生,结合学科特点,注重理论与实践相结合,旨在培养学生的实际操作能力和创新能力。

课程要求学生在掌握基本理论知识的基础上,通过实际操作,提高数字系统设计能力,为今后从事相关领域工作打下坚实基础。

课程目标的设定,既符合学生特点,又满足了教学要求,为后续教学设计和评估提供了明确的方向。

二、教学内容1. 数字系统设计基础:包括数字逻辑基础、组合逻辑设计、时序逻辑设计等,对应教材第1章至第3章内容。

- 数字逻辑基础:逻辑门、逻辑表达式、逻辑函数化简;- 组合逻辑设计:编码器、译码器、多路选择器、算术逻辑单元;- 时序逻辑设计:触发器、计数器、寄存器、状态机。

2. 硬件描述语言(HDL):以Verilog HDL为例,学习语法、数据类型、运算符、过程语句等,对应教材第4章内容。

- 语法基础:模块定义、端口声明、信号声明;- 数据类型和运算符:基本数据类型、运算符及其优先级;- 过程语句:顺序语句、并行语句、赋值语句。

3. FPGA器件结构与编程:介绍FPGA器件的结构、编程原理、配置方法等,对应教材第5章内容。

fpga数字系统设计课程设计

fpga数字系统设计课程设计一、教学目标本课程的教学目标是使学生掌握FPGA数字系统设计的基本理论、方法和技术,培养学生进行数字系统分析和设计的能力。

具体目标如下:1.知识目标:学生能够理解并掌握FPGA的基本结构、工作原理和编程方法;了解数字系统设计的基本流程,掌握常用的数字电路设计方法。

2.技能目标:学生能够熟练使用FPGA设计工具,进行数字系统的分析和设计;能够独立完成数字电路的仿真、验证和编程。

3.情感态度价值观目标:培养学生对新技术的敏感性和好奇心,增强学生的创新意识和团队协作精神。

二、教学内容教学内容主要包括以下几个部分:1.FPGA的基本原理:介绍FPGA的结构、工作原理和编程方法。

2.数字系统设计方法:讲解数字系统设计的基本流程,包括需求分析、系统设计、电路设计、仿真验证等。

3.常用数字电路设计方法:包括组合逻辑电路、时序逻辑电路、数字信号处理器等的设计方法。

4.FPGA设计工具的使用:介绍常用的FPGA设计工具,如VHDL、Verilog等,以及如何进行数字电路的仿真、验证和编程。

三、教学方法为了提高教学效果,将采用多种教学方法相结合的方式进行教学:1.讲授法:通过讲解FPGA的基本原理、数字系统设计方法和常用数字电路设计方法,使学生掌握基本知识。

2.案例分析法:通过分析具体的数字电路设计案例,使学生了解并掌握数字电路设计的实际过程。

3.实验法:通过实验操作,使学生熟悉FPGA设计工具的使用,提高学生的实际操作能力。

四、教学资源为了支持教学内容和教学方法的实施,将准备以下教学资源:1.教材:《FPGA数字系统设计》。

2.参考书:提供相关的数字电路设计参考书籍,供学生自主学习。

3.多媒体资料:制作课件、实验视频等,以丰富教学手段,提高学生的学习兴趣。

4.实验设备:准备FPGA开发板、示波器等实验设备,供学生进行实验操作。

五、教学评估为了全面、客观地评估学生的学习成果,将采用多种评估方式相结合的方法:1.平时表现:通过课堂参与、提问、讨论等方式,评估学生的学习态度和理解程度。

fpga技术课程设计

fpga技术课程设计一、课程目标知识目标:1. 理解FPGA的基本概念、结构与工作原理,掌握FPGA在数字系统设计中的应用。

2. 学会使用硬件描述语言(如VHDL/Verilog)进行数字电路设计,并能将设计成功地在FPGA上实现。

3. 掌握FPGA设计流程,包括设计输入、综合、布局布线、仿真和下载等环节。

技能目标:1. 能够运用所学知识,设计简单的数字系统,具备基本的FPGA编程与调试能力。

2. 培养学生动手实践和问题解决能力,提高团队协作和沟通能力,形成良好的工程素养。

情感态度价值观目标:1. 培养学生对FPGA技术及数字系统设计的兴趣,激发学生的求知欲和创新精神。

2. 强化质量意识,培养学生严谨、细致的工作态度,形成良好的职业道德观念。

3. 增强学生的国家意识,认识到FPGA技术在我国电子产业发展中的重要性,激发学生的爱国情怀。

本课程针对高年级学生,结合学科特点,注重理论与实践相结合,以培养学生的实际操作能力和创新精神为核心。

课程目标具体、可衡量,旨在让学生在学习过程中明确学习成果,为后续教学设计和评估提供依据。

二、教学内容1. FPGA基本原理:包括FPGA的结构、工作原理、配置与编程方法等,对应教材第1章内容。

2. 硬件描述语言基础:以VHDL/Verilog为例,讲解基本语法、数据类型、运算符和基本电路描述方法,对应教材第2章内容。

3. 数字电路设计与实现:介绍组合逻辑电路和时序逻辑电路的设计方法,以及FPGA上的实现过程,对应教材第3章内容。

4. FPGA设计流程:讲解设计输入、综合、布局布线、仿真和下载等环节的操作方法和注意事项,对应教材第4章内容。

5. 实践项目:结合教材附录中的实例,进行FPGA编程与调试实践,提高学生的动手能力。

6. 课程拓展:介绍FPGA在人工智能、大数据等领域的应用,激发学生的创新意识。

教学内容安排和进度如下:1. 第1周:FPGA基本原理及配置方法学习。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

课程设计任务书学生姓名:专业班级:指导教师:工作单位:信息工程学院题目: 电子琴的设计课程设计目的:《FPGA原理与应用》课程设计的目的是为了让学生熟悉基于VHDL语言进行FPGA开发的全流程,并且利用FPGA设计进行专业课程理论知识的再现,让学生体会EDA技术的强大功能,为今后使用FPGA进行电子设计奠定基础。

课程设计内容和要求设计内容:(1)设计一个八音电子琴。

(2)由键盘输入控制音响,同时可自动演奏乐曲。

(3)用户可以将自己编制的乐曲存入电子琴,演奏时可选择键盘输入乐曲或者已存入的乐曲。

要求每个学生单独完成课程设计内容,并写出课程设计说明书、说明书应该包括所涉及到的理论部分和充足的实验结果,给出程序清单,最后通过课程设计答辩。

时间安排:指导教师签名:年月日系主任(或责任教师)签名:年月日目录摘要 (1)Abstract (2)1设计意义和要求 (3)1.1设计意义 (3)1.2功能要求 (3)2方案论证及原理分析 (4)2.1实现方案比较 (4)2.2乐曲实现原理 (4)2.3系统组成及工作原理 (6)3系统模块设计 (8)3.1顶层模块的设计 (8)3.2乐曲自动演奏模块的设计 (8)3.3音阶发生器模块的设计 (9)3.4数控分频器模块的设计 (9)4程序设计 (11)4.1VHDL设计语言和ISE环境简介 (11)4.2顶层模块的程序设计 (12)4.3乐曲自动演奏模块的程序设计 (13)4.4音阶发生器模块的程序设计 (13)4.5数控分频模块的程序设计 (14)5设计的仿真与实现 (15)5.1乐曲自动演奏模块仿真 (15)5.2音调发生模块仿真 (18)5.3数控分频模块仿真 (19)5.4电子琴系统的仿真 (20)5.5设计的实现 (22)5.6查看RTL视图 (23)5.7查看综合报告 (25)6心得体会 (31)7参考文献 (32)8附录 (33)摘要随着基于FPGA的EDA技术的发展和应用领域的扩大与深入,EDA技术在电子信息、通信、自动控制用计算机等领域的重要性日益突出。

EDA技术就是以计算机为工具,设计者在EDA软件平台上,用硬件描述语言HDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。

利用EDA工具,电子设计师可以从概念、算法、协议等开始设计电子系统,大量工作可以通过计算机完成,并可以将电子产品从电路设计、性能分析到设计出IC版图或PCB版图的整个过程的计算机上自动处理完成。

此次设计主要是基于VHDL文本输入法设计乐曲演奏电路,运用VHDL语言对简易电子琴的各个模块进行设计,并使用EDA工具对各模块进行仿真验证。

该系统基于计算机中时钟分频器的原理,采用自顶向下的设计方法来实现,通过按键输入来控制音响或者自动演奏已存入的歌曲。

系统由乐曲自动演奏模块、音调发生模块和数控分频模块三个部分组成。

选择手动弹奏模式按键时,按下音符键后就会选通相应的频率输出;选择自动演奏模式按键时,储存器会将编写好的音符信息依次取出,去选通各个对应的频率输出,实现自动演奏。

系统实现是用硬件描述语言VHDL按模块化方式进行设计,然后进行编程、时序仿真、电路功能验证,奏出美妙的乐曲(当然由于条件限制,暂不进行功能验证,只进行编程和时序仿真)。

关键词:EDA,VHDL,电子琴,自动演奏AbstractWith the expansion and further FPGA-based EDA technology development and applications, the importance of EDA technology in the field of electronic information, communication, computer and other automatic control have become increasingly prominent. EDA technology is to the computer as a tool designer in the EDA software platform, hardware description language HDL complete the design file and then automatically done by computer logic compilation, simplification, segmentation, integration, optimization, placement, routing and simulation, until for specific target chip adapter compilation, mapping and logic programming download work.Use of EDA tools, electronic designers from concept, algorithms, protocols, and so began the design of electronic systems, a lot of work can be done by computer and electronic products can be from the circuit design, performance analysis to the entire process of IC layout design or layout of the PCB automatic processing is completed on the computer.The design is mainly based on VHDL text input music performance circuit design, each module using VHDL language of simple flower design, and the use of EDA tools for simulation of each module. The system is based on the principle of the computer clock divider, using top-down design approach to achieve, through the key input to control the sound or song to automatically play has been deposited. System from automatically playing music module, tone generator module and NC divider module three parts. When you select the manual mode after the play button, it will note is pressed the corresponding frequency strobe output; Select Auto Play mode button, the reservoir will be removed in order to write good music information, each corresponding to the frequency of the strobe output, automatic playing. System implementation is hardware description language VHDL by a modular approach to design, and then programming, timing simulation, circuit functional verification, play wonderful music (of course, due to constraints, they will not perform functional verification, and timing simulation program only) .Key words: EDA, VHDL, electronic organ, automatic play1设计意义和要求1.1设计意义电子琴作为音乐与科技的产物,在电子化和信息化的时代,为音乐的大众化做出了很大的贡献,歌曲的制作大多数都要由电子琴来完成,然后通过媒介流传开来,电视剧和电影的插曲、电视节目音效、甚至手机铃声,都很可能包含电子琴的身影。

电子琴是数字电路中的一个典型应用。

然而在实际的硬件设计中用到的器件非常多,连线比较复杂,同时会产生比较大的延时,从而造成测量误差较大,可靠性不好。

以EDA工具作为开发手段,运用VHDL硬件描述语言可以使使整个系统大大简化,提高了电子琴整体的性能和可靠性。

1.2功能要求1)设计一个八音电子琴;2)由键盘输入控制音响,同时可自动演奏乐曲;3)用户可以将自己编制的乐曲存入电子琴,演奏时可选择键盘输入乐曲或者已存入的乐曲。

2方案论证及原理分析2.1实现方案比较方案一:采用数字逻辑电路制作,用IC拼凑焊接实现。

其特点是直接用现成的IC 组合而成,简单方便,但本系统需用到许多分频器,这就使得需要用到相当多的IC,从而造成了体积过于庞大,而且连线也会比较复杂。

方案二:由单片机来完成设计。

可用单片机控制键盘的输入,以及产生相应的频率信号作为输出。

目前,单片机的功能已比较强大,集成度日益增高且其设计和控制比较容易。

但是由于在传统的单片机设计系统中必须使用许多分立元件组成单片机的外围电路,如锁存器,译码器等都需要单独的电路,因此整个系统显得十分复杂,抗干扰性差,在运行过程中容易死机或进入死循环,可靠性降低,而功耗费用增高。

方案三:采用可编程逻辑器件(FPGA)来完成该设计,将所有器件集成在一块芯片上,大大减小了电子琴的体积,可靠性和精度都比较好。

用VHDL编程实现时更加方便,而且易于进行功能扩展,并可调试仿真,制作时间大大缩短。

综合分析后我认为,方案三采用FPGA的方法来实现,不仅可以实现按键播放音乐和自动播放音乐的要求,有较高的灵敏度和可靠性。

并且原理方法和模块结构清晰,制作方案比较容易实现,所以我采用方案三作为具体实现方案。