数字电子技术基础(第五版)阎石课件

合集下载

关于数电第五版阎石课件

转换步骤:

(1)写出已有触发器和待求触发器的特性方程。

(2)变换待求触发器的特性方程,使之形式与已有 触发器的特性方程一致。

(3)比较已有和待求触发器的特性方程,根据两个 方程相等的原则求出转换逻辑。

(4)根据转换逻辑画出逻辑电路图。

JK 触发器→RS触发器

变换RS触发器的特性方程,使之形式与 JK触发器的特性 方程一致:

1 1

J=1 K=1 时, Q=0,G 7 输出0,主触发器置1,CLK↓,Q *=1; Q=1,G 8 输出0,主触发器置0,CLK↓,Q *=0。

Q *=Q′

JK 触发器的特性表

JKQ

Q*

0

0

0

0

0

0

1

1

0

1

0

0

0

1

1

0

1

0

0

1

1

0

1

1

1

1

0

1

1

1

1

0

功能

Q* ? Q

保持

Q* ? 0 置 0

例5.4.3

第二三个CLK==1 1期期间间,, Q=10,,J=J0=,KK==11,, 主触发 发器器被被置置1,0虽;然虽然CLK C下L降K沿下到降达沿时到又达回时到 又J=0回, 从到触K=发0器, 但保从持触输 发出器Q *输=1出。Q *=0.

1 0 11 0

四、边沿触发的触发器

1.用两个电平触发 D触发器组成的边沿触发器

CP

CP D Q2

5.6 触发器的逻辑功能及其描述方法

一、触发器按逻辑功能的分类

按 逻

SR触发器

辑

功

JK 触发器

课件数字电技术基础第五版教学课件清华大学阎石王红.ppt

D Q Q*

0 0

1 1

0 1

0 1

0 0

1 1

2.特性方程 : Q* D

3.状态转换图

4.符号

。。。。

《数字电子技术基础》第五版

逻辑功能: 是 Q * 与输入及 Q 在CLK作用后稳态之间的关系 (RS, JK, D, T)

电路结构形式: 具有不同的动作特点(转换状态的动态过程) (同步,主从,边沿)

《数字电子技术基础》第五版

( 5 )有异步置1,置0端

二、动作特点 Q * 变化发生在 clk的上升沿(或下降沿) , Q * 仅取决于上升沿到达时 输入的状态,而与此前 、后的状态无关

《数字电子技术基础》第五版

5.6 触发器的逻辑功能及其描述方法

5.6.1 触发器按逻辑功能的分类 时钟控制的触发器中 由于输入方式不同(单端,双端输入)、次态( Q * )随输 入变化的规则不同

J K CLK

Q S 主 R Q’ 从

Q Q’

《数字电子技术基础》第五版

J Q S 主 R Q’ 从 Q

K

CLK

Q’ (1)若J 1, K 0则clk 1时,

Q* 1 “主”保持 , 1 * Q 0,“主” 1

Q* 1,“主” 0 * Q 0,“主”保持 0

1. 主从 SR 触发器 ( 1 )clk 1时,“主”按 S , R翻转,“从”保持 ( 2 )clk下降沿到达时,“主” 保持, “从”根据“主”的状 态翻转 所以每个 clk周期,输出状态只可能 改变一次

0

1

1 1

1 0

0

1*

1

1 1

1*

《数字电子技术基础》第五版

2. 主从 JK触发器 为解除约束 即使出现 S R 1的情况下, Q * 也是确定的

0 0

1 1

0 1

0 1

0 0

1 1

2.特性方程 : Q* D

3.状态转换图

4.符号

。。。。

《数字电子技术基础》第五版

逻辑功能: 是 Q * 与输入及 Q 在CLK作用后稳态之间的关系 (RS, JK, D, T)

电路结构形式: 具有不同的动作特点(转换状态的动态过程) (同步,主从,边沿)

《数字电子技术基础》第五版

( 5 )有异步置1,置0端

二、动作特点 Q * 变化发生在 clk的上升沿(或下降沿) , Q * 仅取决于上升沿到达时 输入的状态,而与此前 、后的状态无关

《数字电子技术基础》第五版

5.6 触发器的逻辑功能及其描述方法

5.6.1 触发器按逻辑功能的分类 时钟控制的触发器中 由于输入方式不同(单端,双端输入)、次态( Q * )随输 入变化的规则不同

J K CLK

Q S 主 R Q’ 从

Q Q’

《数字电子技术基础》第五版

J Q S 主 R Q’ 从 Q

K

CLK

Q’ (1)若J 1, K 0则clk 1时,

Q* 1 “主”保持 , 1 * Q 0,“主” 1

Q* 1,“主” 0 * Q 0,“主”保持 0

1. 主从 SR 触发器 ( 1 )clk 1时,“主”按 S , R翻转,“从”保持 ( 2 )clk下降沿到达时,“主” 保持, “从”根据“主”的状 态翻转 所以每个 clk周期,输出状态只可能 改变一次

0

1

1 1

1 0

0

1*

1

1 1

1*

《数字电子技术基础》第五版

2. 主从 JK触发器 为解除约束 即使出现 S R 1的情况下, Q * 也是确定的

阎石第五版数字电路技术课件

数字电路基础

触发器概述

触发器的分类

触发器的工作原理

触发器的应用

01

02

03

04

触发器是一种具有记忆功能的电路,能够存储二进制信息。

根据工作原理的不同,触发器可以分为RS触发器、D触发器、JK触发器和T触发器等。

触发器通过接收输入信号,根据不同的工作模式,将存储的信息保持或翻转。

触发器广泛应用于数字系统的设计和实现,如寄存器、计数器等。

详细描述

总结词

数字电路技术的发展历程

详细描述

数字电路技术自20世纪40年代诞生以来,经历了从小规模到大规模,再到超大规模集成电路的发展历程。随着半导体工艺的不断进步,数字电路技术的集成度越来越高,性能越来越强大,应用领域也越来越广泛。

总结词

数字电路技术的应用领域

详细描述

数字电路技术广泛应用于计算机、通信、控制、测量仪器、航空航天、军事等领域。在计算机领域,数字电路技术用于构建中央处理器、存储器、输入输出接口等关键部件。在通信领域,数字电路技术用于信号传输、调制解调、信道编码等。在控制领域,数字电路技术用于实现各种控制算法和控制系统。在测量仪器领域,数字电路技术用于提高测量精度和自动化程度。在航空航天和军事领域,数字电路技术用于实现高速数据处理和精确控制系统。

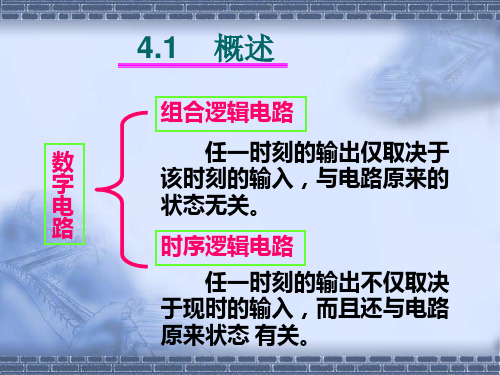

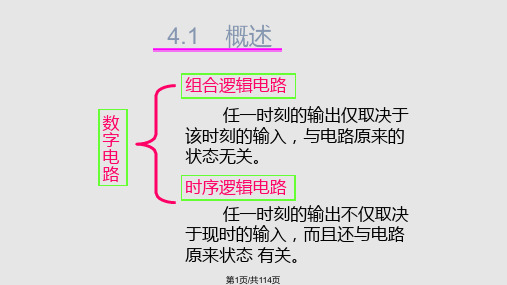

数字电路的分析与设计

根据逻辑函数表达式或真值表,设计实现特定逻辑功能的组合逻辑电路。

组合逻辑电路设计

根据给定的逻辑函数和触发器类型,设计实现特定功能的时序逻辑电路。

时序逻辑电路设计

利用可编程逻辑器件的资源和编程语言,设计实现各种数字电路和系统。

可编程逻辑器件设计

使用硬件描述语言(如Verilog或VHDL)进行数字电路和系统的设计和仿真。

数字电子技术基础课件阎石主编第五版第四章

当S1=1, S2=0, S3 =0(即S=1)时,可得输出

Y0 ( A2 A1A0 ) m0 Y1 ( A2 A1A0 ) m1 Y2 ( A2 A1A0 ) m2

Y4 ( A2 A1A0 ) m4 Y5 ( A2 A1A0 ) m5 Y6 ( A2 A1A0 ) m6

Y3 ( A2 A1A0 ) m3

c

d

BCD-七段显示译码器

A3-A0: 输入数

据

Ya

A3

Yb

A2 A1

译 码

Yc

Yd Ye

器

Yf

A0

Yg

a f gb e dc

要设计的七段显示译码器

十进制数 A3A2A1A0 Ya Yb Yc Yd Ye Yf Yg 显示字形 0 0000 1 1 1 1 1 1 0 0 1 0001 0 1 1 0 0 0 0 1 2 0010 1 1 0 1 1 0 1 2 3 0011 1 1 1 1 0 0 1 3 4 0100 0 1 1 0 0 1 1 4 5 0101 1 0 1 1 0 1 1 5 6 0110 0 0 1 1 1 1 1 6 7 0111 1 1 1 0 0 0 0 7 8 1000 1 1 1 1 1 1 1 8 9 1001 1 1 1 0 0 1 1 9

例4.3.1:试用两片74LS148组成16线-4线优先编码器。

优先权 最高

A15 ~ A8 均无信号时,才允许对A7 ~ A0 输入信号编码。

1 1 1 10 1 0 1 1

0 10 0

11 1

1

0

1

1

(1)片处于编码状态,(2)片被封锁。

11 11 11 11 1 10 10 10 1 0

关于数电第五版阎石课件

Q* ? 1 置 1

Q* ? Q? 翻转

具有多 输入端的主 从JK 触发器, 输入端J 1和 J 2、K1和K2 是与的关系。

集成主从JK 触发器

低电平有效

K ? K1K2K3

低电平有效 CP下降沿触发

J ? J1J2J3

例5.4.2

Q* ? JQ?? K?Q

脉冲触发方式的动作特点:

(1)触发器翻转分 两步动作 :第一步,在 CLK =1期间主触发器接收输入端信号,被置成 相应的状态,从触发器不变;第二步, CLK 下降 沿到来时从触发器按照主触发器的状态翻转,输 出端Q和Q′ 的状态改变发生在 CLK 下降沿。

例5.4.3

第二三个CLK==1 1期期间间,, Q=10,,J=J0=,KK==11,, 主触发 发器器被被置置1,0虽;然虽然CLK C下L降K沿下到降达沿时到又达回时到 又J=0回, 从到触K=发0器, 但保从持触输 发出器Q *输=1出。Q *=0.

1 0 11 0

异步复位端(低 电平有效)

带异步置位、复位端的电平触发 SR 触发器

电平触发方式的动作特点:

在 CLK =1期间,输入信号的变化都直接改变输 出端Q和Q′ 的状态;CLK=0 期间输出状态保持不变。

例:5.3.1

不变

不变

不变

2.D锁存器

S D?

RD?

特性方程: Q*=D

例:5.3.2

特性方程: Q*=D

特性 ?Q* ? S ? R?Q

方程

? ?

SR

?

0

CLK 下降沿到来时有效

例5.4.1

?Q* ? S ? R?Q ??SR ? 0

2.主从JK 触发器

S ? JQ? R ? KQ

数字电子技术基础(第五版)阎石课件

第二十四页,共28页。

用四位自然二进制码中的前十个码字来表示 十进制数码,因各位的权值依次为8、4、2、1,

故称8421 BCD码。

2421码的权值依次为2、4、2、1;

余3码由8421码加0011得到;

格雷码是一种循环码,其特点是任何相邻的 两个码字,仅有一位代码不同,其它位相同。

第二十五页,共28页。

=(5E.B2 )16

第十六页,共28页。

四、十六-二转换

方法:将每位十六进制数用4位二进制数表示。

( 8 F A . C 6)16

=(1000 1111 1010.1100 0110)2

第十七页,共28页。

五、八进制数与二进制数的转换

二进制数与八进制数的相互转换,按照每3 位二进制数对应于一位八进制数进行转换。

第二十六页,共28页。

2421 码 0000 0001 0010 0011 0100 1011 1100 1101 1110 1111 2421

5211 码 0000 0001 0100 0101 0111 1000 1001 1100 1101 1111 5211

例:

(1)2=(

)10 2195

常用 BCD 码

十进制数

0 1 2 3 4 5 6 7 8 9 权

8421 码 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 8421

余 3 码 格雷码 0011 0000 0100 0001 0101 0011 0110 0010 0111 0110 1000 0111 1001 0101 1010 0100 1011 1100 1100 1101

▪基 数: 进位制的基数,就是在该进位制

用四位自然二进制码中的前十个码字来表示 十进制数码,因各位的权值依次为8、4、2、1,

故称8421 BCD码。

2421码的权值依次为2、4、2、1;

余3码由8421码加0011得到;

格雷码是一种循环码,其特点是任何相邻的 两个码字,仅有一位代码不同,其它位相同。

第二十五页,共28页。

=(5E.B2 )16

第十六页,共28页。

四、十六-二转换

方法:将每位十六进制数用4位二进制数表示。

( 8 F A . C 6)16

=(1000 1111 1010.1100 0110)2

第十七页,共28页。

五、八进制数与二进制数的转换

二进制数与八进制数的相互转换,按照每3 位二进制数对应于一位八进制数进行转换。

第二十六页,共28页。

2421 码 0000 0001 0010 0011 0100 1011 1100 1101 1110 1111 2421

5211 码 0000 0001 0100 0101 0111 1000 1001 1100 1101 1111 5211

例:

(1)2=(

)10 2195

常用 BCD 码

十进制数

0 1 2 3 4 5 6 7 8 9 权

8421 码 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 8421

余 3 码 格雷码 0011 0000 0100 0001 0101 0011 0110 0010 0111 0110 1000 0111 1001 0101 1010 0100 1011 1100 1100 1101

▪基 数: 进位制的基数,就是在该进位制

数字电子技术基础阎石主编PPT课件

Y0 ((DB)(DC)) DB DC

第7页/共114页

由真值表知:该电路可用来判别输入的4位二进制数数值的范围。

第8页/共114页

A B (A B) CI ( A B)CI

AB

S A B CI CO (A B)CI AB

第9页/共114页

S A B CI CO (A B)CI AB

0 1 1 1 1 1 0 × ×低电平1表示“0 电路1 工 1 0 0 1 1 1 1 1 1 0 ×作,且1有编码1 输入0 ” 1 0

0 11111110

1 1 1 10

输入:逻辑0(低电平)有效 输出:逻辑0(低电平)有效

第24页/共114页

例4.3.1:试用两片74LS148组成16线-4线优先编码器。

f

gb

e

c

d

第43页/共114页

ab cd

a

f

b

g

e

c

d

ef gh (a) 外形图

a b c d e f g h

(b) 共阴极

第44页/共114页

+VCC a b c d e f g

h (c) 共阳极

a

510

Ya

510 b

Yb

g

510

Yg

a

发

f

g

b

光

二

极 管

e

c

d

Ya-Yg: 控制信号 高电平时,对应的LED亮 低电平时,对应的LED灭

1

1

第19页/共114页

4.3 若干常用的组合逻辑电路

§4.3.1 编码器

编码:用二进制代码来表示某一信息(文 字、数字、符号)的过程。

第7页/共114页

由真值表知:该电路可用来判别输入的4位二进制数数值的范围。

第8页/共114页

A B (A B) CI ( A B)CI

AB

S A B CI CO (A B)CI AB

第9页/共114页

S A B CI CO (A B)CI AB

0 1 1 1 1 1 0 × ×低电平1表示“0 电路1 工 1 0 0 1 1 1 1 1 1 0 ×作,且1有编码1 输入0 ” 1 0

0 11111110

1 1 1 10

输入:逻辑0(低电平)有效 输出:逻辑0(低电平)有效

第24页/共114页

例4.3.1:试用两片74LS148组成16线-4线优先编码器。

f

gb

e

c

d

第43页/共114页

ab cd

a

f

b

g

e

c

d

ef gh (a) 外形图

a b c d e f g h

(b) 共阴极

第44页/共114页

+VCC a b c d e f g

h (c) 共阳极

a

510

Ya

510 b

Yb

g

510

Yg

a

发

f

g

b

光

二

极 管

e

c

d

Ya-Yg: 控制信号 高电平时,对应的LED亮 低电平时,对应的LED灭

1

1

第19页/共114页

4.3 若干常用的组合逻辑电路

§4.3.1 编码器

编码:用二进制代码来表示某一信息(文 字、数字、符号)的过程。

数字电子技术基础课件阎石主编第五版第五章

转换步骤:

(1)写出已有触发器和待求触发器的特性方程。 (2)变换待求触发器的特性方程,使之形式与已有 触发器的特性方程一致。 (3)比较已有和待求触发器的特性方程,根据两个 方程相等的原则求出转换逻辑。 (4)根据转换逻辑画出逻辑电路图。

JK触发器→RS触发器

变换RS触发器的特性方程,使之形式与JK触发器的特性 方程一致:

1 1

J=1 K=1时,

Q=0,G7 输出0,主触发器置1,CLK↓,Q*=1;

Q=1,G8 输出0,主触发器置0,CLK↓,Q*=0。

Q*=Q′

JK触发器的特性表

J 0 0 0 0 1 1 1 1 K 0 0 1 1 0 0 1 1 Q 0 1 0 1 0 1 0 1 Q* 0 1 0 0 1 1 1 0

特性 方程

Q * S R Q SR 0

CLK下降沿到来时有效

例5.4.1

Q * S R Q SR 0

2.主从JK触发器

Q S R Q

*

S JQ

R KQ

J Q ( KQ ) Q J Q K Q CLK 下降沿时有效

例5.5.1 已知D和CP的波 形,试画出Q的 波形。设触发器 初始状态为0。

课堂练习

题目:时钟CP及输入信号D 的波形如图所示,试画 出各触发器输出端Q的波形,设各输出端Q的

初始状态为0.

D CP

D

Q

Q1

D

D

Q

Q2

CP

D CP

D

Q

Q1

CP D

Q1

D CP

D

Q

Q2

CP D Q2

5.6 触发器的逻辑功能及其描述方法

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

13

图8.3.3

具有互补输出的专用输出结构

2006年

新疆大学信息科学与工程学院 <数字电路课题组>

14

二,可编程输入/输出结构 它的输出端是一个有可编程控制端的三态缓冲器 控制端由与逻辑阵列的一个乘积项给出.同时,输出 端又经过一个互补输出的缓冲器反馈到与逻辑阵 列上.

图8.3.4 PAL的可编程输入/输出结构

2006年

新疆大学信息科学与工程学院 <数字电路课题组>

ห้องสมุดไป่ตู้

25

8.4 通用阵列逻辑GAL

要使用GAL器件,就要先进行设计。GAL器件的开发 工具包括硬件开发工具和软件开发工具。硬件开发工 具有编程器,软件开发工具有ABEL-HDL程序设计语言 和相应的编译程序。编程器的主要用途是将开发软件 生成的熔丝图文件按JEDEC格式的标准代码写入选定 的GAL器件。 典型的GAL设计流程图如图所示。

图8.6.1是FPGA基本结构形式的示意图。它由 三种 可编的单元是输入/输出模块IOB(I/O B1ock), 可编程逻辑模块CLB(Configurable Logic Block) 和互连资源IR(Interconnect Resource)。它们 的工作状态全都由编程数据存储器中的数据设定 。

31

图8.4.6

OLMC5种工作模式下的简化电路(图中NC表示不连接)

(a)专用输入模式 (b)专用组合输出模式 (c)反馈组合输出模式 (d)时序电路中的组合输出模式 (e)寄存器输出模式

返回

2006年 新疆大学信息科学与工程学院 <数字电路课题组> 32

8.4.3 GAL的输入特性和输出特性

图8.4.7

2006年

GAL的输入缓冲器电路

33

新疆大学信息科学与工程学院 <数字电路课题组>

GAL的输出缓冲器电路结构中.它除了具有 一般三态输出缓冲器的特点以外,还有两个 突出特点

第一个是输出级该用了单一类型的N沟道增强型 MOS 管,而不是采用P沟道与N沟道管互补的CMOS 机构. 第二个特点是它的输出具有“软开关特性”.

返回

2006年 新疆大学信息科学与工程学院 <数字电路课题组> 34

图8.4.8

2006年

GAL的输出缓冲器电路

返回

35

新疆大学信息科学与工程学院 <数字电路课题组>

图8.4.9 GAL的静态输出特性 (a)输出为高电平时(b)输出为低电平时

返回

2006年 新疆大学信息科学与工程学院 <数字电路课题组> 36

新疆大学信息科学与工程学院 <数字电路课题组>

2006年

37

8.5.2 EPLD的与-或逻辑阵列

2006年

图8.5.1

新疆大学信息科学与工程学院 AT22V10 的电路结构框图 <数字电路课题组>

38

图8.5.3

与-或逻辑阵列的乘积项共享结 构

返回

2006年 新疆大学信息科学与工程学院 <数字电路课题组> 39

新疆大学信息科学与工程学院 <数字电路课题组>

20

2006年

新疆大学信息科学与工程学院 <数字电路课题组>

21

图8.3.9

产生16种算术、逻辑运算的编程情况

2006年

新疆大学信息科学与工程学院 <数字电路课题组>

22

【例8.3.2 】 用PAL设计一个4为循环码计数器,并 要求所设计的计数器具有置零和对输出进行三态 控制的功能.

新疆大学信息科学与工程学院 <数字电路课题组>

49

图8.6.7

返回

2006年 新疆大学信息科学与工程学院 <数字电路课题组> 1

8.1

概

述

图8.1.1 PLD电路中门电路的惯用画法 (a)与门 (b)输出恒等于0的与门 (c)或门 (d)互补输出的缓冲器 (e)三态输出的缓冲器

返回

2006年 新疆大学信息科学与工程学院 <数字电路课题组> 2

图8.1.1

8.3.1 PAL的基本电路结构

PAL器件当中最简单一种电路结构形式,它仅包含一个可编程的与 逻辑阵列和一个固定的或逻辑阵列,没有附加其他的输出电路.

2006年

新疆大学信息科学与工程学院 <数字电路课题组>

10

由图可见,在没有编程之前,与逻辑阵列的所有交叉点上均有熔 丝接通.编程将有的熔丝保留,将无用的熔丝熔断,既得到所有的电 路.它所产生的逻辑函数为

8.5.3 EPLD 的输出逻辑宏单元(OLMC)

EPLD的输出电路结构和GAL相似,也采用了可编 程的输出逻辑宏单元OLMC.通过编程的方法能将 OLMC设置成各种不同的工作状态.而且,由于增 加了对OLMC中触发器的预置和置零功能,因而具 有更大的使用灵活性.

返回

2006年 新疆大学信息科学与工程学院 <数字电路课题组> 40

图8.3.7

2006年

PAL的异或输出结构

18

新疆大学信息科学与工程学院 <数字电路课题组>

五,运算选通反馈结构

在异或输出结构的基础上我们又增加了 一组反馈电路.

图8.3.8

2006年

PAL的运算选通反馈结构

新疆大学信息科学与工程学院 <数字电路课题组> 19

8.3.3 PAL 的应用举例

2006年

PLD电路中门电路的惯用画法

(a)与门(b)输出恒等于0的与门(c)或门 (d)互补输出的缓冲器(e)三态输出的缓冲器

返回

2006年 新疆大学信息科学与工程学院 <数字电路课题组> 3

*8.2

现场可编程逻辑阵列(FPLA)

图8.2.1 FPLA的基本电路结构 图8.2.2 FPLA的异或输出结构 图8.2.3 时序逻辑型 FPLA的电路结构

返回

2006年 新疆大学信息科学与工程学院 <数字电路课题组> 29

8.4.2 输出逻辑宏单元(OLMC)

图8.4.4

2006年

OLMC的结构框图

返回

30

新疆大学信息科学与工程学院 <数字电路课题组>

图8.4.5

GAL16V8结构控制字的组成

返回

2006年

新疆大学信息科学与工程学院 <数字电路课题组>

返回

2006年 新疆大学信息科学与工程学院 <数字电路课题组> 4

返回

2006年 新疆大学信息科学与工程学院 <数字电路课题组> 5

图8.2.1

FPLA的基本电路结构

2006年

新疆大学信息科学与工程学院 <数字电路课题组>

6

图8.2.2

FPLA的异或输出结构

返回

2006年 新疆大学信息科学与工程学院 <数字电路课题组> 7

2006年 新疆大学信息科学与工程学院 <数字电路课题组> 45

图8.6.3

XC2064的IOB电路

2006年

新疆大学信息科学与工程学院 <数字电路课题组>

46

图8.6.4

二,CLB 在XC2064 中有64个 CLB,排列成8 8矩阵。 每个CLB的电路中包含 组合路基电路,存储电 路和由一些数据选择器 组成的内部控制电路, 如图所示。

2006年

新疆大学信息科学与工程学院 <数字电路课题组>

26

图8.4.1

GAL16V8的电路结构图

2006年

新疆大学信息科学与工程学院 <数字电路课题组>

27

图8.4.2

由3个编程单元构成的与门

返回

2006年 新疆大学信息科学与工程学院 <数字电路课题组> 28

图8.4.3

GAL16V8编程单元的地址分配

它在输出三态缓冲器和与-或 逻辑阵列的输出之间串进 了由D触发器组成的寄存器.同时,触发器的状态又经过互 补输出的缓冲器反馈到与逻辑阵列的输入端.

2006年

图8.3.6 新疆大学信息科学与工程学院 PAL的寄存器输出结构

<数字电路课题组>

17

四,异或输出结构 异或的电路结构与寄存器输出结构类似只在与 -或逻辑阵列的输出端又增设了异或门

图8.2.3

时序逻辑型 FPLA的电路结构

返回

2006年 新疆大学信息科学与工程学院 <数字电路课题组> 8

8.3可编程阵列逻辑PAL

PAL的与阵列是可编程的而或阵列不可编程,类似 于一个已经写入信息的ROM,但它的与阵列是可编 程的。

不可编程

2006年 新疆大学信息科学与工程学院 <数字电路课题组> 9

2006年

XC2064的CLB电路

新疆大学信息科学与工程学院 <数字电路课题组>

47

图8.6.5

XC2064中CLB的3种组态

(a)四变量任意函数 (b)两个三变量任意函数 (c)五变量逻辑函数

2006年

新疆大学信息科学与工程学院 <数字电路课题组>

48

图8.6.6

二变量通用逻辑模块的原理图

2006年

8.5 可擦除的可编程逻辑器件(EPLD)

8.5.1 EPLD的基本结构和特点

EPLD是继PAL、GAL之后推出的一种可编程逻辑器件. 与PAL和GAL相比,EPLD有以下几个特点: 1)采用了CMOS工艺,所以EPLD具有CMOS器件低功耗、高 噪声容限的优点. 2)采用了UVEPROM工艺,以叠栅注入MOS管作为编程单元, 所以不仅可靠性高、可以改写,而且集成度高、造价也便宜. 3)特点是输出部分采用了类似于GAL器件的可编程的输出逻 辑宏单元. 此外,为了提高与-或 逻辑阵列中乘积项的利用率,有 些EPLD的或逻辑阵列部分也引入了可编辑逻辑结构.