verilog源代码第8.9章例题

大量的verilog源代码

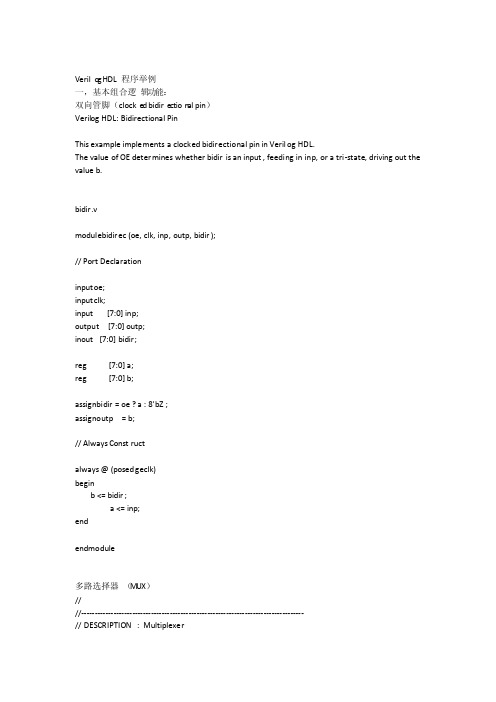

Verilo g HDL 程序举例一,基本组合逻辑功能:双向管脚(clocke d bidire ction al pin)Verilo g HDL: Bidire ction al PinThis exampl e implem entsa clocke d bidire ction al pin in Verilo g HDL.The valueof OE determ ineswhethe r bidiris an input, feedin g in inp, or a tri-state, drivin g out the valueb.bidir.vmodule bidire c (oe, clk, inp, outp, bidir);// Port Declar ationinputo e;inputc lk;input[7:0] inp;output[7:0] outp;inout [7:0] bidir;reg [7:0] a;reg [7:0] b;assign bidir= oe ? a : 8'bZ ;assign outp = b;// Always Constr uctalways @ (posedg eclk)beginb <= bidir;a <= inp;endendmod ule多路选择器(M UX)////-----------------------------------------------------------------------------------// DESCRI PTION : Multip lexer// Code style: used case statem ent// Widthof output termin al: 8// Number of termin als: 4// Output enable active: HIGH// Output valueof all bits when enable not active: 0 //-----------------------------------------------------------------------------------module mux(EN ,IN0 ,IN1 ,IN2 ,IN3 ,SEL ,OUT );inputEN ;input[7:0] IN0 ,IN1 ,IN2 ,IN3 ;input[1:0] SEL ;output [7:0] OUT ;reg [7:0] OUT ;always @(SEL or EN or IN0 or IN1 or IN2 or IN3 )beginif (EN == 0) OUT = {8{1'b0}};elsecase (SEL )0 : OUT = IN0 ;1 : OUT = IN1 ;2 : OUT = IN2 ;3 : OUT = IN3 ;defaul t : OUT = {8{1'b0}};endcas eendendmod ule二进制到BC D码转换//////-----------------------------------------------------------------------------------// DESCRI PTION : Bin to Bcd conver ter// Input(data_i n) width: 4// Output (data_o ut) width: 8// Enable (EN) active : high//-----------------------------------------------------------------------------------module bin2bc d (data_i n ,EN ,data_o ut );input[3:0] data_i n ;inputEN ;output [7:0] data_o ut ;reg [7:0] data_o ut ;always @(data_i n or EN )begindata_o ut = {8{1'b0}};if (EN == 1)begincase (data_i n [3:1])3'b000 :data_o ut [7:1] = 7'b0000000;3'b001 :data_o ut [7:1] = 7'b0000001;3'b010 :data_o ut [7:1] = 7'b0000010;3'b011 :data_o ut [7:1] = 7'b0000011;3'b100 :data_o ut [7:1] = 7'b0000100;3'b101 :data_o ut [7:1] = 7'b0001000;3'b110 :data_o ut [7:1] = 7'b0001001;3'b111 :data_o ut [7:1] = 7'b0001010;defaul t :data_o ut [7:1] = {7{1'b0}};endcas edata_o ut [0] = data_i n [0];endendendmod ule二进制到格雷码转换//----------------------------------------------------------------------------------- // DESCRI PTION : Bin to gray conver ter// Input(DATA_I N) width: 4// Enable (EN) active : high//----------------------------------------------------------------------------------- module BIN2GA RY (EN ,DATA_I N ,DATA_O UT );inputEN ;input[3:0] DATA_I N ;output [3:0] DATA_O UT ;assign DATA_O UT [0] = (DATA_I N [0] ^ DATA_I N [1] ) && EN ; assign DATA_O UT [1] = (DATA_I N [1] ^ DATA_I N [2] ) && EN ; assign DATA_O UT [2] = (DATA_I N [2] ^ DATA_I N [3] ) && EN ; assign DATA_O UT [3] = DATA_I N [3] && EN ;endmod ule7段译码器//----------------------------------------------------------------------------------- // DESCRI PTION : BIN to sevensegmen ts conver ter// segmen t encodi ng// a// +---+// f | | b// +---+ <- g// e | | c// +---+// d// Enable (EN) active: high// Output s (data_o ut) active: low//-----------------------------------------------------------------------------------module bin27s eg (data_i n ,EN ,data_o ut );input[3:0] data_i n ;inputEN ;output [6:0] data_o ut ;reg [6:0] data_o ut ;always @(data_i n or EN )begindata_o ut = 7'b1111111;if (EN == 1)case (data_i n )4'b0000: data_o ut = 7'b1000000; // 04'b0001: data_o ut = 7'b1111001; // 14'b0010: data_o ut = 7'b0100100; // 2 4'b0011: data_o ut = 7'b0110000; // 34'b0100: data_o ut = 7'b0011001; // 44'b0101: data_o ut = 7'b0010010; // 54'b0110: data_o ut = 7'b0000011; // 64'b0111: data_o ut = 7'b1111000; // 74'b1000: data_o ut = 7'b0000000; // 84'b1001: data_o ut = 7'b0011000; // 94'b1010: data_o ut = 7'b0001000; // A4'b1011: data_o ut = 7'b0000011; // b4'b1100: data_o ut = 7'b0100111; // c4'b1101: data_o ut = 7'b0100001; // d4'b1110: data_o ut = 7'b0000110; // E4'b1111: data_o ut = 7'b0001110; // Fdefaul t: data_o ut = 7'b1111111;endcas eendendmod ule二,基本时序逻辑功能:8位数据锁存器//////-----------------------------------------------------------------------------------// DESCRI PTION: Flip-flop D type// Width: 8// CLK active : high// CLR active : high// CLR type : synchr onous// SET active : high// SET type : synchr onous// LOAD active : high// CE active : high//-----------------------------------------------------------------------------------module ffd (CLR , SET , CE , LOAD , DATA_I N , DATA_O UT , CLK );inputCLR , SET , CE , LOAD , CLK ;input[7:0] DATA_I N ;output [7:0] DATA_O UT ;reg [7:0] DATA_O UT_TE MP;always @(posedg e CLK )beginif (CE == 1'b1)if (CLR == 1'b1)DATA_O UT_TE MP = {8{1'b0}};else if (SET == 1'b1)DATA_O UT_TE MP = {8{1'b1}};else if (LOAD == 1'b1)DATA_O UT_TE MP = DATA_I N ;endassign DATA_O UT = DATA_O UT_TE MP;endmod ule移位寄存器//-----------------------------------------------------------------------------------// DESCRI PTION : Shiftregist er// Type :univ// Width: 4// Shiftdirect ion: right/left (rightactive high)//// CLK active : high// CLR active : high// CLR type : synchr onous// SET active : high// SET type : synchr onous// LOAD active : high// CE active : high// SERIAL input: SI//----------------------------------------------------------------------------------- module shft_r eg (CLR , SET , DIR , CE , LOAD , DATA , SI , data_o ut , CLK );inputCLR , SET , CE , LOAD , DIR , SI , CLK ;input[3:0] DATA ;output [3:0] data_o ut ;reg [3:0] TEMP;always @(posedg e CLK )beginif (CE == 1'b1)if (CLR == 1'b1)TEMP = {4{1'b0}};else if (SET == 1'b1)TEMP = {4{1'b1}};else if (LOAD == 1'b1)TEMP = DATA ;else if (DIR == 1'b1)TEMP = {SI , TEMP [3:1]};elseTEMP = {TEMP [2:0], SI };endassign data_o ut = TEMP;endmod ule三,基本语法,元件例化与层次设计:Verilo g HDL: Creati ng a Hierar chica l DesignThis exampl e descri bes how to create a hierar chica l design usingVerilo g HDL.The file top_ve r.v is the top level, whichcallsthe two lowerlevelfilesbottom1.v and bottom2.v. vprim.vtop_ve r.vmodule top_ve r (q, p, r, out);inputq, p, r;output out;reg out, intsig;bottom1 u1(.a(q), .b(p), .c(intsig));bottom2 u2(.l(intsig), .m(r), .n(out));endmod ule-------------------------------------------------------------------------------- bottom1.vmodule bottom1(a, b, c);inputa, b;output c;reg c;alwaysbeginc<=a & b;endendmod ule-------------------------------------------------------------------------------- bottom2.vmodule bottom2(l, m, n);inputl, m;output n;reg n;alwaysbeginn<=l | m;endendmod ule四,状态机举例:同步状态机Verilo g HDL: Synchr onous StateMachin estatem.vmodule statem(clk, in, reset, out);inputc lk, in, reset;output [3:0] out;reg [3:0] out;reg [1:0] state;parame ter zero=0, one=1, two=2, three=3;always @(state)begincase (state)zero:out = 4'b0000;one:out = 4'b0001;two:out = 4'b0010;three:out = 4'b0100;defaul t:out = 4'b0000;endcas eendalways @(posedg eclk or posedg e reset) beginif (reset)state= zero;elsecase (state)zero:state= one;one:if (in)state= zero; elsestate= two; two:state= three; three:state= zero; endcas e endendmod ule。

verilog代码练习题

verilog代码练习题Verilog是一种硬件描述语言,用于描述数字电路的行为和结构。

在学习和掌握Verilog代码编写的过程中,练习题是非常重要的一环。

通过多做一些练习题,可以提高对Verilog语言的理解和运用能力,进而更好地应对实际的电路设计和开发项目。

本文将介绍一些常见的Verilog代码练习题,帮助读者提升自己的编程能力。

具体的练习题如下:练习题一:整数加法器设计一个4位整数加法器,输入两个4位的二进制整数A和B,输出它们的和。

请使用Verilog代码描述该加法器,并给出仿真结果和波形图。

练习题二:时钟分频器设计一个时钟分频器,将输入时钟信号分频为两个输出时钟信号。

其中,输出时钟信号A频率为输入时钟信号的一半,输出时钟信号B 频率为输入时钟信号的四分之一。

请使用Verilog代码描述该时钟分频器,并给出仿真结果和波形图。

练习题三:数字比较器设计一个4位数字比较器,输入两个4位的二进制整数A和B,输出A是否大于B的结果(1表示大于,0表示不大于)。

请使用Verilog代码描述该数字比较器,并给出仿真结果和波形图。

练习题四:有限状态机设计一个简单的有限状态机,实现一个计数器的功能。

输入信号CLK表示时钟信号,每个上升沿计数器加1,输出信号OUT表示计数器的值,初始值为0,最大值为9,超出后回到0。

请使用Verilog代码描述该有限状态机,并给出仿真结果和波形图。

练习题五:位宽可调的加法器设计一个位宽可调的加法器,输入为两个任意位宽的二进制整数A和B,输出为它们的和。

请使用Verilog代码描述该位宽可调的加法器,并给出仿真结果和波形图。

以上是几个常见的Verilog代码练习题,通过多做这些练习题,可以提高对Verilog语言的掌握和运用能力。

在实际的电路设计和开发中,良好的Verilog编程能力是非常重要的。

希望本文对你有所帮助,加油!。

verilog 编程题

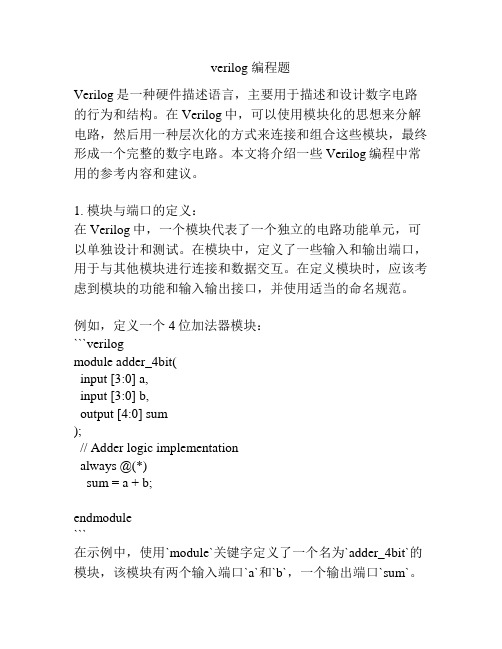

verilog 编程题Verilog是一种硬件描述语言,主要用于描述和设计数字电路的行为和结构。

在Verilog中,可以使用模块化的思想来分解电路,然后用一种层次化的方式来连接和组合这些模块,最终形成一个完整的数字电路。

本文将介绍一些Verilog编程中常用的参考内容和建议。

1. 模块与端口的定义:在Verilog中,一个模块代表了一个独立的电路功能单元,可以单独设计和测试。

在模块中,定义了一些输入和输出端口,用于与其他模块进行连接和数据交互。

在定义模块时,应该考虑到模块的功能和输入输出接口,并使用适当的命名规范。

例如,定义一个4位加法器模块:```verilogmodule adder_4bit(input [3:0] a,input [3:0] b,output [4:0] sum);// Adder logic implementationalways @(*)sum = a + b;endmodule```在示例中,使用`module`关键字定义了一个名为`adder_4bit`的模块,该模块有两个输入端口`a`和`b`,一个输出端口`sum`。

端口的定义使用了位宽表示法`[3:0]`。

2. 连续赋值语句:Verilog中的连续赋值语句用于将一个或多个逻辑信号与特定的电路元件或模块连接起来。

在连续赋值语句中,使用等号`=`来表示信号的赋值,该赋值会立即反映到模块的输出端口。

例如,将一个信号与一个寄存器连接:```verilogalways @(posedge clk)reg <= signal;```在示例中,当时钟信号`clk`上升沿出现时,`reg`的值将被赋值为`signal`。

3. 组合逻辑与时序逻辑:Verilog可以描述组合逻辑和时序逻辑。

组合逻辑是一个纯粹的函数,它的输出只取决于当前的输入。

时序逻辑则会引入时间的概念,其输出不仅仅取决于当前的输入,还取决于过去的输入和内部状态。

Verilog的135个经典设计实例

endmodule

【例 3.2】 4 位计数器

module count4(out,reset,clk); output input [3:0] out; reset,clk;

reg [3:0] out; always @( posedge clk)

begin if else end endmodule (reset) out<=0; out<=out+1; // 同步复位 // 计数

endmodule

【例 3.5】 “与 - 或 -非”门电路

module AOI(A,B,C,D,F); input output A,B,C,D; F; // 模块名为 AOI( 端口列表 A, B, C, D, F) // 模块的输入端口为 // 模块的输出端口为 A, B, C,D F

-2 -

begin if (qout[3:0]==9) begin qout[3:0]<=0; if (qout[7:4]==5) qout[7:4]<=0; // 回 0 ,并判断高位是否为 5 // 低位是否为 9 ,是则

else qout[7:4]<=qout[7:4]+1; end else qout[3:0]<=qout[3:0]+1; end end assign cout=((qout==8'h59)&cin)?1:0; // 产生进位输出信号 // 低位不为 9 ,则加 1 // 高位不为 5 ,则加 1

王金明: 《 Verilog HDL wire A,B,C,D,F; assign endmodule F= ~((A&B)|(C&D)); // 定义信号的数据类型 // 逻辑功能描述

verilog数字系统设计教程第四版例题源码

verilog数字系统设计教程第四版例题源码verilog数字系统设计教程第四版是一本深入浅出的数字系统设计教材,其中包括了丰富的例题与对应的源码。

以下是该书第四版例题的源码综述:1. `add` 模块源码:```verilogmodule add (input [3:0] a,input [3:0] b,output [3:0] sum,output carry);wire [3:0] intermediate_sum;wire intermediate_carry;assign intermediate_sum = a + b;assign carry = intermediate_sum[4];assign sum = intermediate_sum[3:0];endmodule````add` 模块实现了将两个四位数相加的功能。

本例子还演示了 verilog 的基本语法、数据类型、变量的使用、运算符的使用、模块的定义与实例化等基本概念。

2. `d_flip_flop` 模块源码:```verilogmodule d_flip_flop (input clk,input d,output reg q);always @(posedge clk) beginq <= d;endendmodule````d_flip_flop` 模块实现了一个 D 触发器的功能。

本例子还演示了时序逻辑的基本概念,包括时钟信号的使用和寄存器的使用。

3. `counter` 模块源码:```verilogmodule counter (input clk,input reset,output reg [7:0] count);always @(posedge clk or posedge reset) beginif (reset) begincount <= 0;end else begincount <= count + 1;endendendmodule````counter` 模块实现了一个八位计数器的功能。

Verilog第八章

8.3 Mealy型状态机设计

8.4 SystemVerilog的枚举类型应用

8.5 状态机图形编辑设计

8.5 状态机图形编辑设计

8.5 状态机图形编辑设计

8.5 状态机图形编辑设计

8.5 状态机图形编辑设计

8.5 状态机图形编辑设计

8.5 状态机图形编辑设计

8.5 状态机图形编辑设计

8.2.2 序列检测器及其状态机设计

8.3 Mealy型状态机设计

接下页

8.3 Mealy型状态机设计

接上页

8.3 Mealy型状态机设计

8.3 Mealy型状态机设计

接下页

8.3 Mealy型状态机设计

接上页

8.3 Mealy型状态机设计

8.3 Mealy型状态机设计

8.3 Mealy型状态机设计

8-6 通用异步收发器UART设计

实验与设计

8-6 通用异步收发器UART设计

实验与设计

8-7 点阵型与字符型液晶显示器驱动控制电路设计

8-8 串行ADC/DAC控制电路设计

8-9 硬件消抖动电路设计

8-10 数字彩色液晶显示控制电路设计

实验与设计

8-11 状态机控制串/并转换8数码静态显示

实验与设计

8.8.3 定时方式去毛刺

8.8 硬件数字技术排除毛刺

8.8.3 定时方式去毛刺

习

题

实验与设计

8-1 序列检测器设计 8-2 ADC采样控制电路设计

实验与设计

8-3 数据采集模块设计

实验与设计

8-4 五功能智能逻辑笔设计

实验与设计

8-5 比较器加DAC器件实现ADC转换功能电路设计

实验与设计

《Verilog HDL数字系统设计——原理、实例及仿真》课件第8章

1

1

1

1

1

1

1

1

1

1

1

×

×

×

×

×

××

0

0

0

0

×

×

×

×

×

×0

1

0

0

1

×

×

×

×

×

0

1

1

0

1

0

×

×

×

×

0

1

1

1

0

1

1

×

×

×

0

1

1

1

1

1

0

0

×

×

0

1

1

1

1

1

1

0

1

×

0

1

1

1

1

1

1

1

1

0

0

1

1

1

1

1

1

1

1

1

1

第8章 常用组合逻辑电路设计

7

【代码8.1】 实现普通编码器的Verilog HDL描述。

其功能仿真结果见图8.2。

10011111111110

10101111111111

10111111111111

11001111111111

11011111111111

11101111111111

11111111111111

第8章 常用组合逻辑电路设计

20

【代码8.4】 二—十进制译码器模块。

其功能仿真结果见图8.7。

第8章 常用组合逻辑电路设计

第8章 常用组合逻辑电路设计

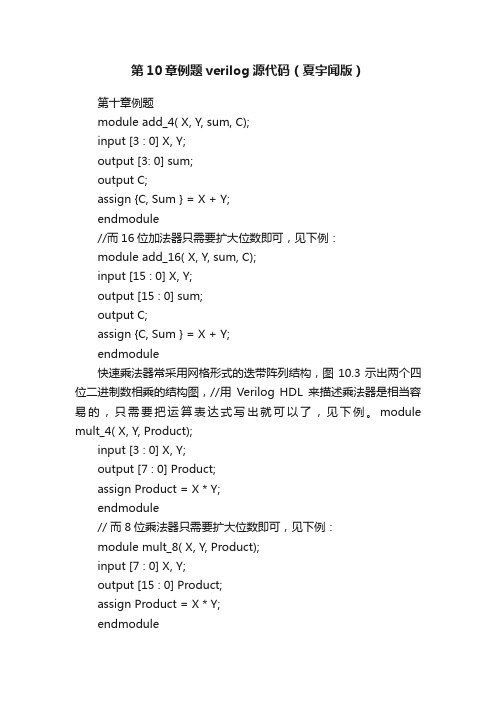

第10章例题verilog源代码(夏宇闻版)

第10章例题verilog源代码(夏宇闻版)第十章例题module add_4( X, Y, sum, C);input [3 : 0] X, Y;output [3: 0] sum;output C;assign {C, Sum } = X + Y;endmodule//而16位加法器只需要扩大位数即可,见下例:module add_16( X, Y, sum, C);input [15 : 0] X, Y;output [15 : 0] sum;output C;assign {C, Sum } = X + Y;endmodule快速乘法器常采用网格形式的迭带阵列结构,图10.3示出两个四位二进制数相乘的结构图,//用Verilog HDL来描述乘法器是相当容易的,只需要把运算表达式写出就可以了,见下例。

module mult_4( X, Y, Product);input [3 : 0] X, Y;output [7 : 0] Product;assign Product = X * Y;endmodule// 而8位乘法器只需要扩大位数即可,见下例:module mult_8( X, Y, Product);input [7 : 0] X, Y;output [15 : 0] Product;assign Product = X * Y;endmodule// 下面就是一个位数可以由用户定义的比较电路模块:module compare_n ( X, Y, XGY, XSY, XEY);input [width-1:0] X, Y;output XGY, XSY, XEY;reg XGY, XSY, XEY;parameter width = 8;always @ ( X or Y ) // 每当X 或Y 变化时beginif ( X = = Y )XEY = 1; // 设置X 等于Y的信号为1else XEY = 0;if (X > Y)XGY = 1; // 设置X 大于Y的信号为1else XGY = 0;if (X < Y)XSY = 1; // 设置X 小于Y的信号为1else XSY = 0;endendmodule//下面就是带使能控制信号(nCS)的数据位宽可以由用户定义的(8位)八路数据通道选择器模块:module Mux_8( addr,in1, in2, in3, in4, in5, in6, in7, in8, Mout, nCS);input [2:0] addr;input [width-1:0] in1, in2, in3, in4, in5, in6, in7, in8;input nCS;output [width-1:0] Mout;parameter width = 8;always @ (addr or in1 or in2 or in3 or in4 or in5 or in6 or in7 or in8 or nCS)beginif (!nCS) //nCS 低电平使多路选择器工作case(addr)3’b000: Mout = in1;3’b001: Mout = in2;3’b010: Mout = in3;3’b011: Mout = in4;3’b100: Mout = in5;3’b101: Mout = in6;3’b110: Mout = in7;3’b111: Mout = in8;endcaseelse //nCS 高电平关闭多路选择器Mout = 0;endendmodule//下面就是一个简单的与总线有接口的模块是如何对总线进行操作的例子:module SampleOfBus( DataBus, link_bus,write );inout [11:0] DataBus; // 12位宽的总线双向端口input link_bus; // 向总线输出数据的控制电平reg [11:0] outsigs; // 模块内12位的宽数据寄存器reg [13:0] insigs; // 模块内14位宽的数据寄存器assign DataBus = (link_bus) ? outsigs : 12 ‘h zzz ;//当link_bus为高电平时通过总线把储存在outsigs的计算结果输出always @(posedge write) //每当write信号上跳沿时begin //接收总线上数据并乘以三insigs <= DataBus * 3; //把计算结果存入insigsendendmodule。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第八章语法概念总复习练习1)以下给出了一个填空练习,请将所给各个选项根据电路图,填入程序中的适当位置。

a s s i g n m o d u l e;~| &i n p u t o u t p u ti n p u t s o u t p u t s e n d m o d u l eA ,B ,C , DAOI ( A, B, C, D, F )input A,B,C,D;output F;assign F = ((A&B)&(C&D));endmodule2〕 在这一题中,我们将作有关层次电路的练习,通过这个练习,你将加深对模块间调用时,管脚间连接的理解。

假设已有全加器模块FullAdder,若有一个顶层模块调用此全加器,连接线分别为W4,W5,W3,W1和W2。

请在调用时正确地填入I/O 的对应信号。

module FullAdder(A,B,Cin,Sum,Cout); input A, B, Cin;output Sum, Cout;endmodule3)initial begin endinitialSEL=0; A=0; B=0;#10 A=1;#10 SEL=1; #10 B=1;$monitor (SEL , A ,B , ,F) ; reg A, B , SEL;wire F;A Sum W1 W2 W3 W4 W5B Cin Countendmodule标准答案:module TestFixturereg A,B,SEL;wire F;MUX2M(SEL,A,B,F);initialbeginSEL=0; A=0; B=0;#10 A=1;#10 SEL=1; #10 B=1;endinitial$monitor(SEL,A,B,,F);endmodule4)指出下面几个信号的最高位和最低位。

reg [1:0] SEL; input [0:2] IP; wire [16:23] A;标准答案:MSB:SEL[1] MSB:IP[0] MSB:A[16]LSB:SEL[0] LSB:IP[2] LSB:A[23]5)P,Q,R都是4bit的输入矢量,下面哪一种表达形式是正确的。

1)input P[3:0],Q,R;2)input P,Q,R[3:0];3)input P[3:0],Q[3:0],R[3:0];4)input [3:0] P,[3:0]Q,[0:3]R;5)input [3:0] P,Q,R;标准答案:5)6)请将下面选项中的正确答案填人空的方括号中。

1. (0:2)2. (P:0)3. (Op1:Op2)4.(7:7)5. (2:0)6. (7:0)reg [7:0] A;reg [2:0] Sum, Op1, Op2;reg P, OneBit;initialbeginSum=Op1+Op2;P=1;A[ ]=Sum;.....end标准答案:57)请根据以下两条语句,从选项中找出正确答案。

7.1) reg [7:0] A;A=2'hFF;1) 8'b0000_0011 2) 8'h03 3) 8'b1111_1111 4) 8'b11111111标准答案:1)、2)7.2) reg [7:0] B;B=8 'bZ0;1) 8'0000_00Z0 2) 8'bZZZZ_00003) 8'b0000_ZZZ0 4) 8'bZZZZ_ZZZ0标准答案:4)8)请指出下面几条语句中变量的类型。

8.1) assign A=B;8.2) always #1Count=C+1;标准答案:A(wire) B(wire/reg) Count(reg) C(wire/reg)9)指出下面模块中Cin,Cout,C3,C5,的类型。

module FADD(A,B,Cin,Sum,Cout);input A, B, Cin;output Sum, Cout;....endmodulemodule Test;...FADDM(C1,C2,C3,C4,C5);...endmodule标准答案:Cin(wire) Cout(wire/reg) C3(wire/reg) C5(wire)10〕在下一个程序段中,当ADDRESS的值等于5'b0X000时,问casex执行完后A和B 的值是多少。

A=0;B=0;casex(ADDRESS)5'b00???: A=1;5'b01???: B=1;5'b10?00,5'b11?00:beginA=1;B=1;endendcase标准答案: A=1 and B=0;11)在下题中,事件A分别在10,20,30发生,而B一直保持X状态,问在50时Count的值是多少。

reg [7:0] Count;initialCount=0;alwaysbegin@(A) Count=Count+1;@(B) Count=Count+1;end标准答案:Count=1;(这是因为当A第一次发生时,Count的值由0变为1,然后事件控制 @(B) 阻挡了进程。

)12)在下题中initial块执行完后I,J,A,B的值会是多少。

reg [2:0] A;reg [3:0] B;integer I, J;initialbeginI=0;A=0;I=I-1;J=I;A=A-1;B=A;J=J+1;B=B+1;end标准答案:I=-1 (整数可为负数)J=0A=7 (A为reg型为非负数,又因为A为3位即为111)B=8 (在B=A时,B=0111,然后B=B+1,所以B=4’b1000)13)在下题中,当V的值发生变化且为-1时,执行完always块后Count的值应是多少?reg[7:0]V;reg[2:0]Count;always @(V)beginCount=0;while(~V[Count])Count=Count+1;end标准答案:Count=0;14)在下题中循环执行完后,V的值是多少?reg [3:0] A;reg V ,W;integer K;....A=4'b1010;for(K=2;K>=0;K=K-1)beginV=V^A[k];W=A[K]^A[K+1];end标准答案:V的值是它进人循环体前值的取反。

(因为V的值与0,1,0 进行了异或,与1的异或改变了V的值。

)15)在下题中,给出了几种硬件实现,问以下的模块被综合后可能是哪一种?always @(posedge Clock)if(A)C=B;1.不能综合。

2.一个上升沿触发器和一个多路器。

3.一个输入是A,B,Clock的三输入与门。

4.一个透明锁存器。

5.一个带clock有始能引脚的上升沿触发器。

标准答案:2,516)在下题中,always状态将描述一个带异步Nreset和Nset输入端的上升沿触发器,则空括号内应填入什么,可从以下五种答案中选择。

always @( )if(!Nreset)Q<=0;else if(!Nset)Q<=1;elseQ<=D;1.negedge Nset or posedge Clock2.posedge Clock3.negedge Nreset or posedge Clock4.negedge Nreset or negedge Nset or posedge Clock5.negedge Nreset or negedge Nset标准答案:417)在下题中,给出了几种硬件实现,问以下的模块被综合后可能是哪一种?1.带异步复位端的触发器。

2.不能综合或与预先设想的不一致。

3.组合逻辑。

4.带逻辑的透明锁存器。

5.带同步复位端的触发器。

1.always @(posedge Clock)beginA<=B;if(C)A<=1'b0;end标准答案:52.always @( A or B)case(A)1'b0: F=B;1'b1: G=B;endcase标准答案:23.always @( posedge A or posedge B )if(A)C<=1'b0;elseC<=D;标准答案:14.always @(posedge Clk or negedge Rst)if(Rst)A<=1'b0;elseA<=B;标准答案:2 (产生了异步逻辑)18)在下题中,模块被综合后将产生几个触发器?always @(posedge Clk)begin: Blkreg B, C;C = B;D <= C;B = A;end1. 2个寄存器 B 和 D2. 2个寄存器 B和 C3. 3个寄存器 B, C 和 D4. 1个寄存器 D5. 2个寄存器 C 和D标准答案:219)在下题中,各条语句的顺序是错误的。

请根据电路图调整好它们的次序。

标准答案:1) 2)20)根据左表中SEL与OP的对应关系,在右边模块的空括号中填入相应的值。

SEL:OP000:1001:3 casex(SEL)010:1 3'b( ): OP=3;011:3 3'b( ): OP=1;100:0 3'b( ): OP=0;101:3 endcase110:0111:3标准答案:casex(SEL)3'bXX1: OP=3;3'b0X0: OP=1;3'b1X0: OP=0;endcase21)在以下表达式中选出正确的.1) 4'b1010 & 4'b1101 = 1'b12) ~4'b1100 = 1'b13) !4'b1011 || !4'b0000 = 1'b14) & 4'b1101 = 1'b15) 1b'0 || 1b'1 = 1'b16) 4'b1011 && 4'b0100 = 4'b11117) 4'b0101<<1 =5'b010118) !4'b0010 is 1'b09) 4'b0001 || 4'b0000 = 1'b1标准答案:3), 5), 8), 9)22)在下一个模块旁的括号中填入display的正确值。

integerI;reg[3:0]A;reg[7:0]B;initialbeginI=-1;A=I;B=A;$display("%b",B);( )A=A/2;$display("%b",A);( )B=A+14$diaplay("%d",B);( ) A=A+14;$display("%d",A);( ) A=-2;I=A/2;$display("%d",I);( ) end标准答案:I=-1;A=I;B=A;$display("%b",B);(00001111) A=A/2;$display("%b",A);(0111) B=A+14$diaplay("%d",B);(21) A=A+14;$display("%d",A);(5)(A 为4位,所以21被截为5)23)]。