东南大学 电子系统设计实验指导书(FPGA基础篇)介绍

FPGA初级实践指南

混合编程语言

概念:结合硬件描述语言和软件 编程语言的特点

应用:广泛应用于FPGA设计, 如Verilog、VHDL等

添加标题

添加标题

添加标题

添加标题

优点:提高了编程效率,降低了 开发难度

发展趋势:随着FPGA技术的发 展,混合编程语言将继续发挥重 要作用

PART 04 FPGA应用实例

数字信号处理

型号

Lattice Diamond: Lattice公司推 出的FPGA开发 工具,支持多种 FPGA型号

ModelSim: Mentor公司推 出的FPGA仿真 工具,支持多

种FPGA型号

PART 02 FPGA设计流程

需求分析

确定设计目标: 明确FPGA设计的 功能和性能要求

需求细化:将设 计目标分解为具 体的功能和性能 指标

逻辑设计

逻辑设计是FPGA设计的核心 步骤,包括功能定义、逻辑 划分和逻辑优化等环节。

功能定义:根据需求,明确 FPGA需要实现的功能,并转化 为逻辑表达式。

逻辑划分:将逻辑表达式划分 为多个子模块,每个子模块实 现特定的功能。

逻辑优化:对子模块进行优化, 提高性能和资源利用率。

逻辑设计完成后,需要进行仿 真验证,确保设计的正确性和 可靠性。

PART 05

FPGA实践经验 分享

常见问题及解决方法

问题:FPGA设计过程中出现错误或警告 解决方法:仔细检查设计 代码,找出错误或警告的原因,并进行修改 解决方法:仔细检查设计代码,找出错误或警告的原因,并进行修改

FPGA设计实验指导书

4'b1101:{q1,q2}<=2'b01;

4'b1110:{q1,q2}<=2'b00;

endcase

end

endmodule

2、设计一个2位信号的比较器,该比较器的电路符号如图2.1所示。

图2.1比较器电路符号

module bijiaoqi (A,B,E,L,G,CLK,RST);

3、异步复位的D触发器;

module DFF1(CLK,RST,Q,D)

input CLK,D,RST;

output Q;

reg Q;

always@(posedge CLK or negedge RST)

begin

if(!RST) Q<=O;

else Q<=D;

end

endmodule

4、同步置位/复位的D触发器;

end

always@(Q1)

if(Q1==5'h23) COUT<=1'b1;

else COUT<=1'b0;

endmodule

2、设计24分频时序电路。

module fenpinqi (CLK_1HZ,CLK_24MHZ,RST);

input CLK_24MHZ,RST;

output CLK_1HZ;

reg [4:0] Q1;

always@(posedge clk_in ,negedge RST)

begin

if(!RST)

begin Q1<=0; end

else if(EN) begin

if(!LOAD) Q1<=Q1;

FPGA实验指导书

目录第1章FPGA系统 (1)1.1 系统简介 (1)1.2 系统功能特点 (1)1.3 开发平台标准配置 (2)1.4 功能模块介绍 (2)1.4.1 电源 (2)1.4.2 系统时钟 (3)1.4.3 LED灯 (3)1.4.4 8位拨码开关 (3)1.4.5 数码管显示 (4)1.4.6 键盘阵列 (5)1.4.7 独立矩形波信号源 (5)1.4.8 蜂鸣器 (6)第2章基础门电路及触发器 (8)2.1 实验一基本门电路 (8)2.1.1 实验目的 (8)2.1.2 实验内容 (8)2.1.3 实验原理及说明 (8)2.1.4 实验步骤 (8)2.1.5 参考程序及引脚分配 (9)2.2 实验二基本触发器 (10)2.2.1 实验目的 (10)2.2.2 实验内容 (10)2.2.3 实验原理及说明 (10)2.2.4 实验步骤 (10)2.2.5 参考程序及引脚分配 (11)2.3 实验三3-8译码器 (13)2.3.1 实验目的 (13)2.3.2 实验内容 (13)2.3.3 实验原理 (13)2.3.4 实验步骤 (13)2.3.5 参考程序及引脚分配 (14)2.4 实验四8—3编码器 (15)2.4.1 实验目的 (15)2.4.2 实验内容 (15)2.4.3 实验原理 (15)2.4.4 实验步骤 (15)2.4.5 参考程序及引脚分配 (16)2.5 实验五BCD八段显示译码器 (17)2.5.1 实验目的 (17)2.5.2 实验内容 (17)2.5.4 实验步骤 (17)2.5.5 参考程序及引脚分配 (17)2.6 实验六四选一数据选择器 (19)2.6.1 实验目的 (19)2.6.2 实验内容 (19)2.6.3 实验原理及说明 (19)2.6.4 实验步骤 (19)2.6.5 实验参考程序及引脚分配: (20)2.7 实验七数值比较器 (21)2.7.1 实验目的 (21)2.7.2 实验内容 (21)2.7.3 实验原理及说明 (21)2.7.4 实验步骤 (21)2.7.5 参考程序及引脚分配 (22)2.8 实验八4位二进制加法器 (23)2.8.1 实验目的 (23)2.8.2 实验内容 (23)2.8.3 实验原理及说明 (23)2.8.4 实验步骤 (24)2.8.5 参考程序及引脚分配 (24)2.9 实验九4位二进制乘法器 (26)2.9.1 实验目的 (26)2.9.2 实验内容 (26)2.9.3 实验原理及说明 (26)2.9.4 实验步骤 (27)2.9.5 参考程序及引脚分配 (27)第3章逻辑电路 (31)3.1 实验十移位寄存器 (31)3.1.1 实验目的 (31)3.1.2 实验内容 (31)3.1.3 实验原理 (31)3.1.4 实验步骤 (31)3.1.5 参考程序及引脚分配 (31)3.2 实验十一串行并行转换 (33)3.2.1 实验目的 (33)3.2.2 实验内容 (33)3.2.3 实验原理及说明 (33)3.2.4 实验步骤 (34)3.2.5 参考程序及引脚分配 (34)3.3 实验十二单时钟同步可逆计数器 (35)3.3.1 实验目的 (35)3.3.2 实验内容 (35)3.3.3 实验原理及说明 (36)3.3.5 参考程序及引脚分配 (36)3.4 实验十三顺序脉冲发生及其检测 (38)3.4.1 实验目的 (38)3.4.2 实验内容 (38)3.4.3 实验原理及说明 (38)3.4.4 实验步骤 (39)3.4.5 参考程序及引脚分配 (39)3.5 实验十四按键数码管循环左移显示 (41)3.5.1 实验目的 (41)3.5.2 实验内容 (41)3.5.3 实验原理 (41)3.5.4 实验步骤 (42)3.5.5 参考程序和引脚分配 (42)3.6 实验十五电子时钟 (45)3.6.1 实验目的 (45)3.6.2 实验内容 (45)3.6.3 实验原理 (46)3.6.4 实验步骤 (46)3.6.5 参考程序及引脚分配 (46)3.7 实验十六按键控制 (52)3.7.1 实验目的 (52)3.7.2 实验内容 (52)3.7.3 实验原理 (52)3.7.4 实验步骤 (53)3.7.5 参考程序及引脚分配 (53)第4章FPGA综合应用 (60)4.1 实验十七数字密码锁 (60)4.1.1 实验目的 (60)4.1.2 实验内容 (60)4.1.3 实验原理 (60)4.1.4 实验步骤 (61)4.1.5 参考程序及引脚分配 (61)4.2 实验十八智力抢答器 (66)4.2.1 实验目的 (66)4.2.2 实验内容 (66)4.2.3 实验原理及说明 (66)4.2.4 实验步骤 (67)4.2.5 参考程序及引脚分配 (68)4.3 实验十九自动售货机 (74)4.3.1 实验目的 (74)4.3.2 实验内容 (74)4.3.3 实验原理 (74)4.3.4 实验步骤 (75)4.3.5 参考程序和引脚分配 (75)4.4 实验二十数字频率计 (80)4.4.1 实验目的 (80)4.4.2 实验内容 (80)4.4.3 实验原理 (80)4.4.4 实验步骤 (81)4.4.5 参考程序及引脚分配 (81)第1章 FPGA系统1.1系统简介FPGA系统教学开发平台采用国际著名可编程逻辑器件公司Altera 的Cyclone系列5万门芯片为核心,整个平台采用模块化设计,各种模块可以自由组合,同时提供丰富的扩展接口,非常适合于FPGA初学者。

FPGA实验指导书(1)

实验一组合逻辑3-8译码器的设计 .................... 错误!未定义书签。

实验二基于FPGA的数字钟的设计 ................... 错误!未定义书签。

实验三基于NIOS的交通灯实验 .......................... 错误!未定义书签。

实验四静态图像显示 ............................................. 错误!未定义书签。

实验一组合逻辑3-8译码器的设计一、实验目的:1、通过3-8译码器的设计,让学生掌握组合逻辑电路的设计方法。

2、掌握组合逻辑电路的静态测试方法。

3、初步了解可编程器件设计的全过程。

二、实验步骤:1、打开QuartusII软件。

2、选择路径。

选择File/New Project Wizard,指定工作目录,指定工程和顶层设计实体称;注意:工作目录名不能有中文。

3、添加设计文件。

将设计文件加入工程中。

单击“Next”,如果有已经建立好的VHDL 或者原理图等文件可以在File name中选择路径然后添加,或者选择Add All添加所有可以添加的设计文件(.VHDL ,.Verilog原理图等)。

如果没有直接点击“Next”,等建立好工程后再添加也可,这里我们暂不添加。

4、选择FPGA器件。

Family选择Cyclone II,Available device选EP2C35F484C8,Packge选择Any,Pin Count 选择484,Speed grade选择Any;点击“Next”。

5、选择外部综合器、仿真器和时序分析器。

Quartus II支持外部工具,可通过选中来指定工具的路径。

这里我们不做选择,默认使用Quartus II自带的工具。

6、结束设置。

单击“Next”,弹出“工程设置统计”窗口,上面列出了工程的相关设置情况。

最后单击“Finish”,结束工程设置。

7、建立原理图文件。

电子系统设计实验指导书(FPGA基础篇Vivado版)

实验指导书(FPGA 基础篇 Vivado 版)

东南大学 电子科学 ........................................................................................................................................................... 1

安全使用规范

东南大学 电子科学与工程学院

无论何时,外部电源供电与 USB 两种供电方式只能用其中一种,避免因为电压有所差别而烧坏电路板。 采用电压高于5.5V的任何电源连接器可能造成永久性的损害。 插拔接插件前请关闭电路板总开关,否则易损坏器件。 电路板应在绝缘平台上使用,否则可能引起电路板损坏。 不同编码机制不要混接。 安装设备需防止静电。 液晶显示器件或模块结雾时,不要通电工作,防止电极化学反应,产生断线。 遇到正负极连接时需谨慎,避免接反引起开发板的损坏。 保持电路板的表面清洁。 小心轻放,避免不必要的硬件损伤。

实验目的 ....................................................................................................................................................... 17 实验内容 ....................................................................................................................................................... 17 实验要求 ....................................................................................................................................................... 17 实验步骤 ....................................................................................................................................................... 17 实验结果 ....................................................................................................................................................... 22

FPGA方向课程设计指导书(2013)

《电子系统设计》方向组方向课程设计指导书电子系统设计方向组编中原工学院电子信息教研室2011年12月1日前言电子信息类基础专业课程主要包括《模拟电子技术》、《数字电子技术》、《微机原理与应用》、《单片机原理与应用》、《信号与系统》、《数字信号处理》、《EDA基础》等。

电子系统设计方向在原有基础课程上增加了《集成电路原理与应用》、《FPGA系统设计与应用》及《锁相技术》等专业课程。

《数字信号处理》是电子信息工程、通信工程专业的一门重要的理论性和实践性都很强的专业必修课,目的是让学生了解数字信号处理的基本理论、基本分析方法、基本算法和基本实现方法。

包括离散时间LSI系统的理论及其时域、频域分析方法,DFT算法,FFT算法,以及IIR、FIR滤波器的结构和设计方法,为后续课程的学习和工作实践打下理论基础。

《集成电路原理与应用》是一门应用性较强的专业课程,是研究模拟和数字集成电路的器件和电路结构、工作原理以及设计方法的学科,本课程应用半导体器件等基础知识,在模拟电子技术与数字电子技术等课程内容的基础上进一步深入学习,目的是培养学生掌握集成电路的设计方法, 培养学生分析、解决电子系统基本问题和能力。

《FPGA系统设计与应用》是一门发展十分迅速、应用非常广泛的前沿交叉学科,由于高密度现场可编程逻辑器件(CPLD/FPGA)和专用集成电路的飞速发展,传统的设计技术已经不适合大规模及超大规模集成电路,FPGA技术正是为了适应现代电子产品设计的要求,吸收多学科最新成果而形成的一门新技术。

课程目的是使学生了解FPGA的内部原理、结构,并学会利用EDA开发工具进行电子系统的设计,以及在信号、通信领域方面的应用。

为了帮助学生深入理解和消化基本理论、进一步提高综合应用能力并且锻炼独立解决问题的能力,我们将《数字信号处理》、《集成电路原理与应用》和《FPGA系统设计与应用》几门课程融合在一起开设的FPGA综合实验课程设计。

FPGA实验指导书2

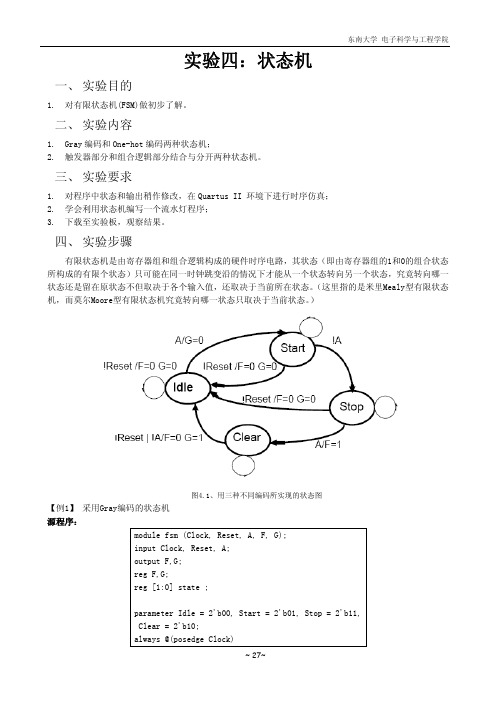

实验四:状态机一、 实验目的1.对有限状态机(FSM)做初步了解。

二、 实验内容1.Gray编码和One-hot编码两种状态机;2.触发器部分和组合逻辑部分结合与分开两种状态机。

三、 实验要求1.对程序中状态和输出稍作修改,在Quartus II 环境下进行时序仿真;2.学会利用状态机编写一个流水灯程序;3.下载至实验板,观察结果。

四、 实验步骤有限状态机是由寄存器组和组合逻辑构成的硬件时序电路,其状态(即由寄存器组的1和0的组合状态所构成的有限个状态)只可能在同一时钟跳变沿的情况下才能从一个状态转向另一个状态,究竟转向哪一状态还是留在原状态不但取决于各个输入值,还取决于当前所在状态。

(这里指的是米里Mealy型有限状态机,而莫尔Moore型有限状态机究竟转向哪一状态只取决于当前状态。

)图4.1、用三种不同编码所实现的状态图【例1】 采用Gray编码的状态机源程序:module fsm (Clock, Reset, A, F, G);input Clock, Reset, A;output F,G;reg F,G;reg [1:0] state ;parameter Idle = 2'b00, Start = 2'b01, Stop = 2'b11,Clear = 2'b10;always @(posedge Clock)beginif (!Reset)beginstate <= Idle; F<=0; G<=0;endelse begincase (state)Idle: beginif (A) beginstate <= Start;G<=0;endelse state <= Idle;endStart: beginif (!A) state <= Stop;else state <= Start;endStop: beginif (A) beginstate <= Clear;F <= 1;endelse state <= Stop;endClear: beginif (!A) beginstate <=Idle;F<=0; G<=1;endelse state <= Clear;endendcaseendendendmodule【例2】采用One-hot编码的状态机源程序:module fsm (Clock, Reset, A, F, G);input Clock, Reset, A; output F,G;reg F,G;reg [3:0] state ;parameter Idle = 4'b1000,Start = 4'b0100,Stop = 4'b0010,Clear = 4'b0001;always @(posedge Clock)beginif (!Reset)beginstate <= Idle; F<=0; G<=0;endelsebegincase (state)Idle: beginif (A) beginstate <= Start;G<=0;endelse state <= Idle;endStart: beginif (!A) state <= Stop;else state <= Start;endStop: beginif (A) beginstate <= Clear;F <= 1;endelse state <= Stop;endClear: beginif (!A) beginstate <=Idle;F<=0; G<=1;endelse state <= Clear;enddefault: state <=Idle;endcaseendendendmodule例1中采用Gray编码,例2中采用的是One-hot编码。

数字电子技术FPGA实验指导书资料

数字电子技术基础与FPGA实验指导书前言FPGA是英文Field Programmable Gate Array的缩写,即现场可编程门阵列,它是在PAL、GAL、EPLD等可编程器件的基础上进一步发展的产物。

它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个新概念,内部包括可配置逻辑模块CLB(Configurable Logic Block)、输出输入模块IOB(Input Output Block)和内部连线(Interconnect)三个部分。

FPGA的基本特点主要有:1)采用FPGA设计ASIC电路,用户不需要投片生产,就能得到合用的芯片。

2)FPGA可做其它全定制或半定制ASIC电路的中试样片。

3)FPGA内部有丰富的触发器和I/O引脚。

4)FPGA是ASIC电路中设计周期最短、开发费用最低、风险最小的器件之一。

5)FPGA采用高速CHMOS工艺,功耗低,可以与CMOS、TTL电平兼容。

可以说,FPGA芯片是小批量系统提高系统集成度、可靠性的最佳选择之一。

目前FPGA的品种很多,有XILINX的XC系列、TI公司的TPC系列、ALTERA 公司的FIEX系列等,本实验平台选用了ALTERA公司Cyclone II系列芯片FPGA是由存放在片内RAM中的程序来设置其工作状态的,因此,工作时需要对片内的RAM进行编程。

用户可以根据不同的配置模式,采用不同的编程方式。

加电时,FPGA芯片将EPROM中数据读入片内编程RAM中,配置完成后,FPGA进入工作状态。

掉电后,FPGA恢复成白片,内部逻辑关系消失,因此,FPGA能够反复使用。

FPGA的编程无须专用的FPGA编程器,只须用通用的EPROM、PROM编程器即可。

当需要修改FPGA功能时,只需换一片EPROM 即可。