集成锁相环及其相关3

集成锁相环简介

谐振荡器,它由压控电流源 I 0 、施密特触发器、开

开关转换电路、电压跟随器 A1和放大器 A2 组成。 其中,压控电流源 I 0 轮流地向外接电容C进行正 向和反向充电,产生对称的三角波电压,施密特触发器 将它变换为对称方波电压,通过 A1 和 A2 去控制开关S, 实现 I 0 对C轮流充电。 6.5

复和施密特触发电路,用来对FSK信号进行整形。为

便于使用,VCO的输出通过电平变换电路产生TTL和

ECL兼容的电平。

Hale Waihona Puke 6.5NE564如图6.5.2(b)所示, NE564的工作频 率可达50 MHz,它的VCO也采用和L562相同,采用的 是射极耦合多谐振荡器。NE564是一种更适宜于用作 调频信号和移频键控信号解调器的通用器件,因此, 在它的组成方框图中,输入端增加了振幅限幅器,用 来消除输入信号中的寄生调幅,输出端增加了直流恢

6.5 集成锁相环简介

L562是工作频率可达30MHz的多功能单片

集成锁相环路,它的内部除包含鉴相器和压控振

荡器之外,还有三个放大器和一个限幅器,其内

部组成如图6.5.1(a)所示,外引脚排列如图

6.5.1(b)所示。

6.5

图6.5.1

L562通用集成锁相环路内部电路组成及其引脚排列

SL565的组成方框图如图6.5.2(a)所示,它 的主要组成部分仍是鉴相器和VCO。鉴相器都是采 用双差分对相乘器的乘积型鉴相器。SL565的工作 频率可达500kHz,VCO采用积分一施密特触发型多

第11-12讲单片集成锁相环

第11讲单片集成锁相环单片集成锁相环是将锁相环路的重要部件鉴相器、压控振荡器以及某些特殊的器件集成在同一基片之上,各部件之间部分连接或均不连接的一种集成电路。

使用者可以按需要在电路外部连接各部件来实现锁相环路的各种功能,因此,这种集成锁相环具有多功能或部分多功能的性质,可称之为“通用”。

通用单片集成锁相环的产品已经很多,它们所采用的集成工艺不同,使用的频率也不同。

考虑到国内外已有的产品及使用情况,本章介绍几种典型的单片集成锁相环。

国内外总的情况另附录三说明。

高频单片集成锁相环NE一560NE——561NE一562(L一562)HA——2800XR一2l0一、NE一560电路说明NE一560是56系列电路中最基本的一种电路,其方框图如图5-30所示。

它包括鉴相器、压控振荡器、环路滤波器、限幅器和两个缓冲放大器。

鉴相器由双平衡模拟相乘器组成,输入信号加在12、13端。

内部各部件均已接好。

当环路对输入信号锁定时电路可提供两种输出,一是与输入信号频率和压控振荡器之间的频差成比例的电压,即鉴频输出,一是与输入信号频率相同的压控振荡器方波输出。

图5-30 NE560的内部方广框图NE一560的线路图如图5—2,压控振荡器由Q11—Q14组成,是一个射极定时多谐振荡器,其工作电压是由Q26射极的l4V经6.3V的齐纳二极管D1之后所得到的7.7V。

这样就免除了电源电压对压控振荡器工作频率的影响。

Q20、Q21、Q23、Q24四个管子的基极电压由二极管D6、D7置定,构成四个恒流源为压控振荡器供给工作电流。

Q22和Q25组成差分放大器,用以调整压控振荡器的频率。

当Q22的偏压高于Q25的偏压时,就会从Q12和Ql3中多拉出一部分电流,使得对外按定时电容C。

的充电和放电电流相应地加大。

因为压控振荡的的振荡频率正比于定时电容的充放电电流,所以振荡频率就随之提高。

反之,若Q22的偏压低于Q25的偏压,压控振荡器振荡频率则降低。

锁相环的电路组成、器件参数及工作原理

摘要:简单介绍了锁相环电路的基本概念及原理,以通用型集成锁相环4046为例主要介绍了锁相环的电路组成、器件参数及工作原理,并对COMS集成锁相环CC4046的应用做了简单研究。

关键词:锁相环鉴相器压控振荡器1 引言锁相环作为一种重要的功能电路在通信、导航、控制、仪器仪表等领域得到了广泛的应用。

20世纪70年代以后随着集成电路技术的飞速发展,出现了多种型号的集成锁相环产品,其中模拟式集成锁相环以NE/SE 560系列最为常用,COMS集成锁相环CD/CC4046最具代表性。

两者基本原理相同,区别在于前者的鉴相器由模拟电路组成,而后者由逻辑电路组成。

2 锁相环的基本概念所谓锁相,就是相位同步的自动控制。

完成两个信号间相位同步的自动控制系统的环路叫做锁相环,也称PLL(Phase Locked Loop)。

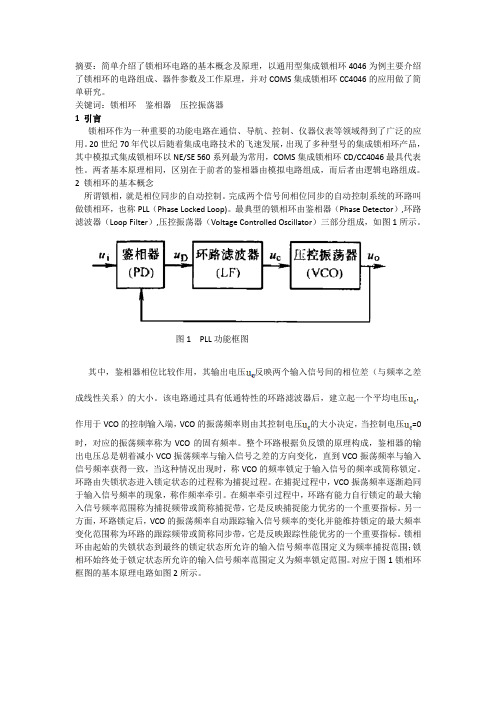

最典型的锁相环由鉴相器(Phase Detector),环路滤波器(Loop Filter),压控振荡器(Voltage Controlled Oscillator)三部分组成,如图1所示。

图1 PLL功能框图其中,鉴相器相位比较作用,其输出电压反映两个输入信号间的相位差(与频率之差成线性关系)的大小。

该电路通过具有低通特性的环路滤波器后,建立起一个平均电压,作用于VCO的控制输入端,VCO的振荡频率则由其控制电压的大小决定,当控制电压=0时,对应的振荡频率称为VCO的固有频率。

整个环路根据负反馈的原理构成,鉴相器的输出电压总是朝着减小VCO振荡频率与输入信号之差的方向变化,直到VCO振荡频率与输入信号频率获得一致,当这种情况出现时,称VCO的频率锁定于输入信号的频率或简称锁定。

环路由失锁状态进入锁定状态的过程称为捕捉过程。

在捕捉过程中,VCO振荡频率逐渐趋同于输入信号频率的现象,称作频率牵引。

在频率牵引过程中,环路有能力自行锁定的最大输入信号频率范围称为捕捉频带或简称捕捉带,它是反映捕捉能力优劣的一个重要指标。

集成锁相环及其相关3

集成锁相环及其相关3集成锁相环及其相关(三)上面的几节课我们研究了电荷泵锁相环的动态特性。

也提到了由于不同的电路结构所导致的锁相环的VCO输出的相位抖动,在本课的开头我们首先讨论这些相位抖动对锁相环路的影响。

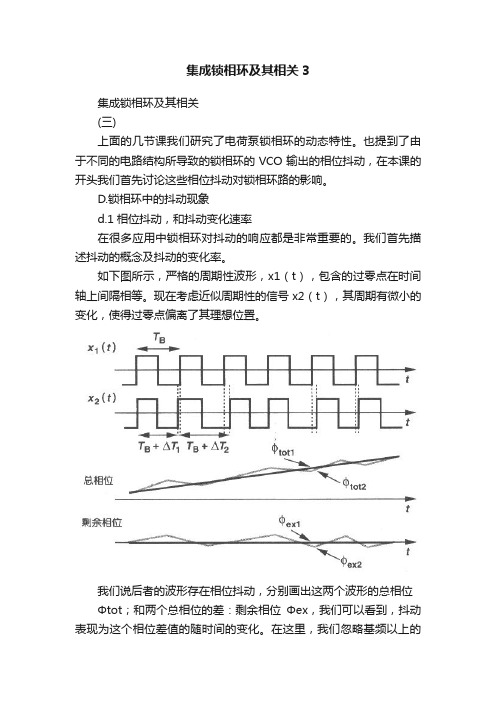

D.锁相环中的抖动现象d.1相位抖动,和抖动变化速率在很多应用中锁相环对抖动的响应都是非常重要的。

我们首先描述抖动的概念及抖动的变化率。

如下图所示,严格的周期性波形,x1(t),包含的过零点在时间轴上间隔相等。

现在考虑近似周期性的信号x2(t),其周期有微小的变化,使得过零点偏离了其理想位置。

我们说后者的波形存在相位抖动,分别画出这两个波形的总相位Φtot;和两个总相位的差:剩余相位Φex,我们可以看到,抖动表现为这个相位差值的随时间的变化。

在这里,我们忽略基频以上的各次谐波的分量,描述x1(t),和x2(t)我们可以写出:x1(t)=A×cos(ωt)和x2(t)=A×cos(ωt+Φn(t))其中Φn(t)表示相位的抖动变化,Φn(t)也被称之为相位噪声。

在实际的应用中,抖动的变化速率也很重要。

考虑如下图所示的两个有抖动的波形。

第一个信号y1(t),表现为慢抖动特性,因为从一个周期到下一个周期,它的瞬间频率变化很慢。

第二个信号y2(t),表现出快抖动特性。

相位变化率的快慢可以从这两个波形的剩余相位曲线明显看出。

d.2锁相环输入信号和输出信号之间相位抖动的低通关系在实际的锁相环中,存在两种可能的相位抖动现象.输入信号自身的抖动、以及前面几节课中我们提到的VCO自身产生的抖动。

我们下面来研究每一种情况.假设输人和输出波形可表达为:xin(t)=A×cos(ωt+Φin(t))和xout(t)=A×cos(ωt+Φout(t))原来我们提到过电荷泵锁相环CPPLL的线性模型,推导出这个模型,的开环传递函数为:因为环路传递函数在原点处有两个极点,这种环又被称之为II类锁相环;原来的那种单极点的简单环路称之为I类环路。

集成锁相环简介

3 集成锁相环简介目前利用线性集成电路技术,可以方便,经济的把锁相环制成单片形式。

单片集成锁相环是将锁相环路的重要部件鉴相器,压控振荡器以及某些特殊的器件,集成在同一基片上。

3.1集成鉴相器鉴相器是锁相环路三个最基本的部件之一,用来比较输入信号与压控振荡器输出信号的瞬时相位,产生一个相应于两信号相位差的误差电压输出,在锁相环路中,他完成相位差---电压的变换作用。

在不同用途中,对鉴相器的要求主要有:1.鉴相特性形状;2.鉴相特性斜率和鉴相灵敏度;3.最高工作频率;4.对输入信号的泄露;5.鉴相器的门限;6.鉴相能力;鉴相器的具体线路很多,考虑到宜于集成化,单片集成鉴相器主要有:1.相乘鉴相器:包括双平衡差分模拟相乘器和电流比率(线性化)模拟相乘器等;2.门鉴相器:包括或门。

异或门,与非门,或非门和异或非门等;3.数字式鉴相器:包括触发器型鉴相器和电压器,电流型数字式鉴相器等。

门鉴相器随着数字锁相环的发展,现在的锁相环路中的鉴相器基本都是门电路或触发器电路实现的。

门电路常见的有或门和异或门;触发器有D触发器,RS触发器等。

现在的鉴相器均有鉴频鉴相功能,其鉴频鉴相特性如图3.1所示。

图3.1鉴频鉴相特性3.2是一个典型的鉴频鉴相电路3.2典型的鉴频鉴相电路数字鉴相器1是一个鉴频器-相器。

它有九个TTL与非门组成,2,3门和5,6门分别构成两个R-S触发器,上下两部分电路完全对称。

8门或9门输出宽带正比于两鉴相信号相差和频差的开关信号。

鉴相器2由两个TTL与非门10,11和一个反向器组成。

在环路中,它通常用于正交锁定或锁定指示器。

3.3集成压控振荡器压控振荡器的作用是完成电压与频率的变换,压控振荡器主要有以下一些指标:1.控制灵敏度:单位电压引起的频率变化量;2.线性度:输入控制电压与输出振荡频率的控制特性偏离直线的程度;3.线性范围:电压-频率控制保持线性的控制电压的范围;4.最大频偏:最大控制电压作用下的最大频偏量;5.最高工作频率;6.频率稳定度:振荡频率随各种因素(如环境温度。

集成电路锁相环及其应用电路设计.pptx

相位锁定。

wi

wo

wo

1

锁相环路基本组成方框图

第2页/共18页

压控振荡器

压控振荡器是一个电压-频率变换装置,在环路

中 作 为 被 控 振 荡 器 , 它 的 振 荡 频 率 应 随 输 入 控 制 电 ωV(t)

压 Uc(t) 线 性 地 变 化 ( 在 一 定 范 围 内 ) , 可 用 线 性

without frequency

offset).

8

固有振荡频率f第v9与页/共R181页,C1的关系

锁相环电路的应用

倍频:

i 鉴相器

i (t )

'

y

yn

环路 滤波器

分频器

÷n

压控 y

振荡器 y (t )

wi

wy n

9

wy nwi

第10页/共18页

锁相环电பைடு நூலகம்的应用

分频:

i 鉴相器

i (t )

方程来表示

即

ωV(t)=ωV + KV Uc(t)

当Uc(t)=0时,VCO的固有振荡频率为ωV 。

ωV

Uc(t)

wi

wo

wo

2

锁相环路基本组成方框图

第3页/共18页

wi

wo

wo

锁相环路基本组成方框图

输入信号和输出信号的相位关系

系统的瞬时相差θe(t)=θ1(t)-θ2(t)

3

第4页/共18页

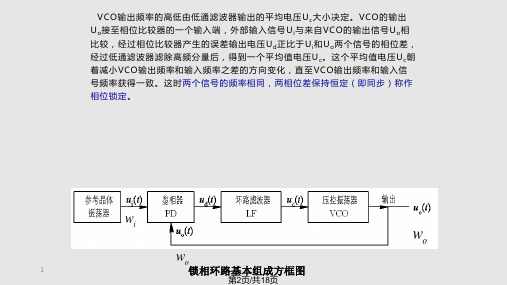

wi wo

VCO输出频率的高低由低通滤波器输出的平均电压Uc大小决定。VCO的输出 Uo接至相位比较器的一个输入端,外部输入信号Ui与来自VCO的输出信号Uo相 比较,经过相位比较器产生的误差输出电压Ud正比于Ui和Uo两个信号的相位差, 经过低通滤波器滤除高频分量后,得到一个平均值电压Uc。这个平均值电压Uc朝 着减小VCO输出频率和输入频率之差的方向变化,直至VCO输出频率和输入信

锁相环原理及应用PLL

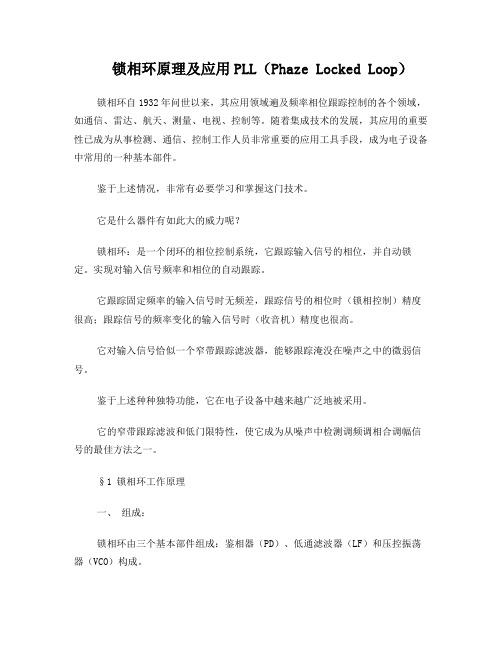

锁相环原理及应用PLL(Phaze Locked Loop)锁相环自1932年问世以来,其应用领域遍及频率相位跟踪控制的各个领域,如通信、雷达、航天、测量、电视、控制等。

随着集成技术的发展,其应用的重要性已成为从事检测、通信、控制工作人员非常重要的应用工具手段,成为电子设备中常用的一种基本部件。

鉴于上述情况,非常有必要学习和掌握这门技术。

它是什么器件有如此大的威力呢?锁相环:是一个闭环的相位控制系统,它跟踪输入信号的相位,并自动锁定。

实现对输入信号频率和相位的自动跟踪。

它跟踪固定频率的输入信号时无频差,跟踪信号的相位时(锁相控制)精度很高;跟踪信号的频率变化的输入信号时(收音机)精度也很高。

它对输入信号恰似一个窄带跟踪滤波器,能够跟踪淹没在噪声之中的微弱信号。

鉴于上述种种独特功能,它在电子设备中越来越广泛地被采用。

它的窄带跟踪滤波和低门限特性,使它成为从噪声中检测调频调相合调幅信号的最佳方法之一。

§1 锁相环工作原理一、组成:锁相环由三个基本部件组成:鉴相器(PD)、低通滤波器(LF)和压控振荡器(VCO)构成。

与相敏检测器的不同之处在于参考信号由输出的信号闭环形成。

1.鉴相器:是一个相位比较环节,它把输入信号与压控振荡器输出信号的相位进行比较,产生对应两信号相位差的误差电压。

是两信号相位差鉴相器特性可以是多种多样的,有正弦形、方波、三角形、锯齿形特性。

它的电路有各种形式,主要有两类:1)相乘器电路2)序列电路:它的输出电压是输入信号过零点与反馈电压过零点之间时间差的函数。

这类鉴相器的输出只与波形的边沿有关,适用于方波,通常用电路构成。

2.低通滤波器(环路):具有低通特性,滤除中的变频成分和噪声,以保证环路要求的性能,增加环路的稳定性,产生对应的一个直流控制电压。

常用的环路滤波器有:RC积分滤波器、无源比例积分滤波器和有源比较积分滤波器3.VCO(Voltage Controlled Oscillator):它是一个电压—频率转换器,由控制产生相应频率,使其频率朝着输入信号的频率靠拢,由于相位负反馈的作用直至消除频差实现环路锁定。

锁相环的电路组成、器件参数及工作原理

摘要:简单介绍了锁相环电路的基本概念及原理,以通用型集成锁相环4046为例主要介绍了锁相环的电路组成、器件参数及工作原理,并对COMS集成锁相环CC4046的应用做了简单研究。

关键词:锁相环鉴相器压控振荡器1 引言锁相环作为一种重要的功能电路在通信、导航、控制、仪器仪表等领域得到了广泛的应用。

20世纪70年代以后随着集成电路技术的飞速发展,出现了多种型号的集成锁相环产品,其中模拟式集成锁相环以NE/SE 560系列最为常用,COMS集成锁相环CD/CC4046最具代表性。

两者基本原理相同,区别在于前者的鉴相器由模拟电路组成,而后者由逻辑电路组成。

2 锁相环的基本概念所谓锁相,就是相位同步的自动控制。

完成两个信号间相位同步的自动控制系统的环路叫做锁相环,也称PLL(Phase Locked Loop)。

最典型的锁相环由鉴相器(Phase Detector),环路滤波器(Loop Filter),压控振荡器(Voltage Controlled Oscillator)三部分组成,如图1所示。

图1 PLL功能框图其中,鉴相器相位比较作用,其输出电压反映两个输入信号间的相位差(与频率之差成线性关系)的大小。

该电路通过具有低通特性的环路滤波器后,建立起一个平均电压,作用于VCO的控制输入端,VCO的振荡频率则由其控制电压的大小决定,当控制电压=0时,对应的振荡频率称为VCO的固有频率。

整个环路根据负反馈的原理构成,鉴相器的输出电压总是朝着减小VCO振荡频率与输入信号之差的方向变化,直到VCO振荡频率与输入信号频率获得一致,当这种情况出现时,称VCO的频率锁定于输入信号的频率或简称锁定。

环路由失锁状态进入锁定状态的过程称为捕捉过程。

在捕捉过程中,VCO振荡频率逐渐趋同于输入信号频率的现象,称作频率牵引。

在频率牵引过程中,环路有能力自行锁定的最大输入信号频率范围称为捕捉频带或简称捕捉带,它是反映捕捉能力优劣的一个重要指标。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

集成锁相环及其相关(三)上面的几节课我们研究了电荷泵锁相环的动态特性。

也提到了由于不同的电路结构所导致的锁相环的VCO输出的相位抖动,在本课的开头我们首先讨论这些相位抖动对锁相环路的影响。

D.锁相环中的抖动现象d.1相位抖动,和抖动变化速率在很多应用中锁相环对抖动的响应都是非常重要的。

我们首先描述抖动的概念及抖动的变化率。

如下图所示,严格的周期性波形,x1(t),包含的过零点在时间轴上间隔相等。

现在考虑近似周期性的信号x2(t),其周期有微小的变化,使得过零点偏离了其理想位置。

我们说后者的波形存在相位抖动,分别画出这两个波形的总相位Φtot;和两个总相位的差:剩余相位Φex,我们可以看到,抖动表现为这个相位差值的随时间的变化。

在这里,我们忽略基频以上的各次谐波的分量,描述x1(t),和x2(t)我们可以写出:x1(t)=A×cos(ωt)和x2(t)=A×cos(ωt+Φn(t))其中Φn(t)表示相位的抖动变化,Φn(t)也被称之为相位噪声。

在实际的应用中,抖动的变化速率也很重要。

考虑如下图所示的两个有抖动的波形。

第一个信号y1(t),表现为慢抖动特性,因为从一个周期到下一个周期,它的瞬间频率变化很慢。

第二个信号y2(t),表现出快抖动特性。

相位变化率的快慢可以从这两个波形的剩余相位曲线明显看出。

d.2锁相环输入信号和输出信号之间相位抖动的低通关系在实际的锁相环中,存在两种可能的相位抖动现象.输入信号自身的抖动、以及前面几节课中我们提到的VCO自身产生的抖动。

我们下面来研究每一种情况.假设输人和输出波形可表达为:xin(t)=A×cos(ωt+Φin(t))和xout(t)=A×cos(ωt+Φout(t))原来我们提到过电荷泵锁相环CPPLL的线性模型,推导出这个模型,的开环传递函数为:因为环路传递函数在原点处有两个极点,这种环又被称之为II类锁相环;原来的那种单极点的简单环路称之为I类环路。

简单的I型和II型锁相环的传输函数都具有低通特性,如果Φin(t)变化很快,那么Φout(t)不能完全跟上变化。

也就是说: l 输人的慢抖动可以传递和影响到到VCO的输出的相位抖动;l 而较为快速的抖动却衰减了,而不会影响到VCO的输出抖动因此我们可以说,锁相环对Φin(t)具有低通滤波作用。

参见下图:d.3锁相环VCO固有抖动和输出信号之间相位抖动的高通关系然后我们假设输人波形是严格周期性的,但假设VCO本身存在固有的相位抖动情况。

我们将这种抖动看成是随机相位变化,我们构造了如下图所示的模型:(上图对应于下图所示的电荷泵锁相环:)假设其中输入的剩余相位为零(即,x1(t)=A×cos(ωt))并且在VCO的输出中增加了一个随机分量Φvco来表示其相位的抖动。

我们不经推导得出对于II型锁相环,从Φvco到Φout的传输函数等于:上式具有高通的特性,显示由VCO所产生的慢抖动分量被抑制了,而快抖动分量没有被抑制。

参考下图可以理解这一点:如果Φvco(t)变化非常缓慢(例如,VCO振荡频率随着温度的飘移),那么它与Φin=0的信号(也就是完全的周期性信号)比较会产生一个缓慢变化的相位误差信号,它传输经过LPF的滤波,然后去调节VCO的振荡频率,从而可以抵消VCO的变化。

另一方面如果VCO的变化非常快(例如,VCO受到电路中较高频率噪声对它的振荡频率的调制作用)那么由鉴相器输出的相位误差信号将被环路的低通作用(环路的极点)严重衰减,导致相位误差无法传递到Vcont中,从而使得VCO无法对相位的快速变化作出正确的修正。

导致如上图所示的Φout(t)/Φvco(t)相对于Φvco(t)变化速率的高通效应。

上面从概念上总结了锁相环对输人抖动和VCO抖动的响应。

在实际的应用中其中的一种或者两种抖动都是必须要考虑的,具体的情况与实际的应用环境有关,要求设计人员对对环路带宽进行适当的优化和电路构型的适当选择。

E 延迟锁相环在目前的高速数字电路系统应用中比较常用的有一种称之为:延迟锁相环DLL的锁相环路。

e.1延迟锁相环简介如下图所示:我们假设在一个数字电路中需要四个时钟相位,相邻时钟沿之间的延迟必须准确地间隔为∆T=1ns。

那么如何产生满足上述相位要求的时钟信号呢?首先我们可以简化的考虑使用一种两级差动环路振荡器来产生四个相位(这里要指出的是在实际的CMOS集成电路中,这种简单的两级CMOS环路是不能够起振的)。

在实际的应用中,我们必须保证在不同的工艺条件和温度变化的情况下,都具有稳定的∆T=1ns,这就要求振荡器必须锁定在250 MHz(/ns)的参考时钟下,使得输出时钟的周期正好等于 4 ns,原理如下,Vcont控制和调整两个差动放大器输出延迟,使得每个单级差动放大器的延迟等于2ns,此时两级放大起的输出延迟为4ns,即250MHz。

这种电路的结构较为复杂,同时两个差动放大器的最小延迟不可能作的非常小,为此需要考虑其他的方法。

利用简单门电路的延迟效应,可以提出产生这些所需时钟的另外一个方法:由上图,使输人时钟经过四级门电路构成的串联延迟电路。

但是这种方法不能够产生精确的时钟沿间隔,因为每一级门电路的延迟时间会随工艺和温度而变化,因此在有严格的定时要求的电路中是不能直接使用这种电路的。

这里再给出另外的一种的电路,如下图所示:其中CKin和CK4之间的相位差用一个鉴相器来检测产生与Ckin和CK4之间相位差成比例的平均控制电压Vcont,通过这个负反馈电压的来调节每一个门级的延时。

对于大的环路增益,CKin和CK4之间的相位差很小,即这四级电路将时钟几乎准确地延时了一个周期,从而建立了准确的时钟沿间隔。

这种电路结构被称为延迟锁相环。

这是由于它采用了一个电压控制延迟线(VCDL)电路而不是一个真正的VCO。

实际的电路中为获得无穷大的环路增益,需要在PD和LPF之间插人电荷泵。

每级延时电路可以根据下图所示的环形振荡器的变种电路来设计。

e.2延迟锁相环DLL与传统锁相环电路PLL的比较l 首先,延迟线与振荡器相比受噪声影响小;这是因为,波形中被噪声破坏的过零点在延迟线的末端就被多级延迟门电路整形而消失了,而在振荡器电路中,由于振荡器自身的正反馈,必然会导致这个被噪声破坏的过零点再次循环到这个振荡器的反馈输入端,从而产生因而产生更多连锁过零点的损坏。

l VCDL的相应函数的简单导致,稳定性的提高;如下图所示的VCDL电路中控制电压的变化能迅速改变延迟时间,也就是说,传输函数Φout(s)/Vcont(s)简单地等于VCDL的增益Kvcdl。

因此,上面图中的反馈系统与LPF的阶数相同,但其稳定性和稳定速度等重要问题比PLL的要减轻许多。

下面我们给出如下图所示的DLL的闭环传输函数:也就是上节课我们给出的那种接近于实际电路的CPPLL电路中的VCO部分我们更换为一个压控延迟线VCDL。

它的传递函数我们不经证明的给出:需要注意的一点是,在实际的应用中因为整个环路在原点处只有一个极点,因此可以不需要电阻Rp。

e.3延迟锁相环DLL的缺点l 首先DLL主要的缺点是不能产生可变的输出频率。

我们在后面的关于锁相环路应用的课程中会研究PLL的频率合成功能,将会讲述这一点。

l 其次DLL可能还有锁定延迟时间不确定性的缺点。

也就是说,如原来图中四级电路所示电路的总延时从低于Tin的值变化到高于2Tin的值时,延迟锁相环可能会把CKin 到CK4的延时锁定在Tin或2Tin。

如果要求DLL电路必须提供十分准确的时钟沿间隔,则这种不确定性是很有问题的,因为相邻时钟沿的时间间隔可能被定在2Tin/4而不是Tin/4。

在这种情况下,需要通过附加电路来避免这种不确定性。

l 另外,每级延迟电路与其负载之间的不匹配也会导致时钟沿间隔的误差。

在实际的电路中往往使用大输出电流的大尺寸的输出器件和仔细的版图设计来避免或者减轻这一情况。

F锁相环和延迟环的应用锁相电路的实际应用例子包括内存控制电路、微处理时钟电路,硬盘信号还原驱动电路、射频载频和本振的合成电路,光纤和网络通讯电路的时钟还原电路等等。

我们前面介绍的理想的和简单的,在环路内部没有附加其他器件的锁相环的输入参考信号的频率和相位与VCO或者VCDL的输出相位完全相等。

对于纯粹的数字电路,这样的PLL或者DLL和一根直联的导线从效果上讲是没有任何区别的。

因为两者都可以保证Vin 和Vout的相位和频率完全一致,因此我们必须举例说明PLL和DLL 在实际集成电路系统中的重要性!f.0锁相环倍频在模拟特别是高频电路中,通常有两种方法来或者不同频率的,高精度的频率信号1. 使用选频放大器从包含丰富的非线性输出分量的基频振荡器,比如晶体振荡器中选出3,5,7….或者2,4,….次谐波的方式来获得基频的2,3,4,5…倍的频率信号。

(图)2. 两个或者数个精确频率通过非线性的混频器获得他们的差频或者和频,或者他们的谐波的差频和和频。

但是从后面大家可以看到这两种方法存在很多的局限性,例如谐波分量太多,多个精细的频率间隔不容易获得,等等问题,而采用PLL的频率发生电路却非常容易搞定这些问题,它并且通过这两种方法的结合可以获得满足各种要求的频率源。

简单的M倍频器请参考下面的电路图:这里的“除M”表示一个分频比为M的数字分频器,普通的由一个定周期的计数器就可以实现,由前面讲述的原理可以知道,当锁相环锁定后有:fin=fd,而fd=fout/M因此可以得到:fout=M×fin;理论上通过这个电路可以获得fin的任意倍频,但是实际的电路当中M的数值会影响锁相环的各个特性,因此有一定的限制。

这个电路的变种可以实现多种多样的倍频电路,包括小数倍频等等。

PLL的倍频电路主要应用于各种系统的频率合成电路中,在后面的课程里我们会讲述更数字化的,和可以获得更精密输出的DDS 合成器。

f.1一个处理器系统中pll的应用这里我们首先以一个实际的32位嵌入处理器系统为例,说明锁相环路在处理器内存时钟分配,和PCI时钟分配电路中的应用:f1.1 结构简介这里我们考虑第二代的使用G2 core的PPC处理器,MOTOROLA公司的MPC82XX系列处理器,这些处理器内部包括:1. 一个PPC G2的core,内部包含一个提供系统时钟的时钟合成PLL单元;用以产生CORE运行所需的几百M的时钟和SDRAM运行所需的几十到一百多M时钟以及各种定时信号。

通过对处理器相应的CORE PLL 配置寄存器的配置可以实现对输入的SYSTEM CLK或者PCI CLK时钟的N,或者N.5(N为整数)的倍频。

2. 各种的外设模块,包括通用串行口、SPI接口、I2C接口、DMA控制器、内存控制器、以及用于SDRAM时钟还原的一个0延迟DLL等等。