数电课程设计 射击自动报靶器

数字电路课程设计实例---24秒计时器

河南理工大学万方科技学院《数字电子技术基础》课程设计电气与自动化工程系电气工程及其自动化10届电气3班1016301013张克科李宝平2012.6.18—2012.6.2424秒计数器概述1.1篮球竞赛24秒计时器功能数字电子技术在社会生活中发挥着越来越重要的作用,在生活中有着各种各样的应用。

因此课程设计是数字电子技术学习中非常重要的一个环节,它将学生的理论知识和实践能力统一起来,为以后的工作做好准备。

在篮球比赛中,规定了球员的持球时间不能超过24秒,否则就犯规了。

本课程设计的“篮球竞赛24秒计时器”可用于篮球比赛中,用于对球员持球时间24秒限制。

一旦球员的持球时间超过了24秒,它就自动报警从而判定此球员的犯规。

本课程设计是脉冲数字电路的简单应用,设计了篮球竞赛24秒计时器。

此计时器功能齐全,有显示24秒倒计时的功能,同时系统设置外部操作开关,控制计时器的直接清零、启动、暂停、连续功能。

而在直接清零时,数码管显示器灭灯,计时器为24秒递减计时其计时间间隔为1秒,计时器递减计时到零时,数码管显示器不灭灯,同时发出光电报警信号。

1.2设计任务及要求1.2.1 基本要求(1)显示24秒计时功能。

(2)设置外部操作开关控制计时器直接清零、启动、暂停/连续功能。

(3)在直接清零时,要求数码显示器灭灯。

(4)计时器为24秒递减计时器,其计时间隔为1秒。

(5)递减计时到零时,显示器不能灭灯,同时发出光电报警信号。

(6)秒脉冲由555多谐振荡器给出。

1.2.2设计任务及目标(1)根据原理图分析各单元电路的功能;(2)熟悉电路中所用到的各集成块的管脚及其功能;(3)进行电路的装接、调试、直到电路能达到规定的设计要求;(4)写出完整、详细的课程设计报告电路设计原理与单元模块2.1设计原理24秒计时器的总体参考方案框图如图2.1所示。

它包括秒脉冲发生器、计数器、译码显示电路、报警电路和辅助时序控制电路等五个模块组成。

自动报靶开题报告

自动报靶开题报告自动报靶开题报告一、研究背景自动报靶是一种利用现代技术手段实现的射击训练辅助系统,它可以模拟实际战场环境,提供准确的射击数据和反馈,帮助射击运动员提高射击技能。

随着科技的不断发展,自动报靶系统在射击训练中的应用越来越广泛,成为提高射击训练效果的重要工具。

二、研究目的本研究旨在设计和开发一种基于自动报靶的射击训练系统,通过对射击数据的收集和分析,帮助射击运动员改进射击技巧,提高射击命中率和反应速度。

同时,通过对自动报靶系统的改进和优化,提升系统的稳定性和可靠性,满足射击训练的实际需求。

三、研究内容1. 自动报靶系统的设计与开发:本研究将设计一种基于传感器和图像识别技术的自动报靶系统,用于实时监测射击过程中的各项指标,如命中率、射击速度、射击稳定性等。

系统将通过传感器采集射击数据,并通过图像识别技术对射击靶进行实时监测和分析,提供准确的射击反馈。

2. 射击数据的收集与分析:本研究将开发一种数据采集与分析模块,用于收集射击过程中的各项数据,并进行综合分析。

通过对射击数据的统计和比对,可以发现射击过程中存在的问题和不足之处,并提供相应的改进建议。

同时,通过对射击数据的历史记录和对比分析,可以帮助射击运动员了解自身射击水平的变化和提高情况。

3. 自动报靶系统的优化与改进:本研究将对自动报靶系统进行不断的优化和改进,提升系统的稳定性和可靠性。

通过对系统的硬件和软件进行改进,减少系统的误差和漏报率,提高系统的精度和灵敏度。

同时,优化系统的用户界面和操作流程,提升用户体验,减少射击训练的时间和精力消耗。

四、研究方法本研究将采用实验研究法和实地调查法相结合的方法进行研究。

通过实验室内外的射击训练场地,收集射击数据和用户反馈,并进行数据分析和系统改进。

同时,通过与射击运动员和教练的深入交流和访谈,了解他们对自动报靶系统的需求和期望,从而指导系统的设计和改进。

五、预期成果本研究的预期成果包括:1. 自动报靶系统的设计与开发,实现射击数据的实时监测和反馈。

基于单片机控制的自动报靶系统设计

1 引言1.1 课题研究背景及发展方向在军队射击训练和各种体育射击比赛中,示靶、检靶、报靶和成绩的记录统计,是训练和比赛过程中的主要保障工作。

目前,这些保障工作大部分还是依靠人工来完成的。

人工报靶有着工作量大、效率低、安全性差的特点。

想要提高射击比赛或训练中报靶的效率,最主要是要解决自动报靶的问题[1]。

因此,设计制作并采用安全有效的自动报靶系统具有重要的现实意义也是迫切的现实需求。

当今较为先进的报靶系统包括光电坐标靶、图像处理坐标靶、CCD线阵靶、声电坐标靶、光纤编码坐标靶刚、双电极短路坐标靶等[2][3]。

但以上这些方法也存在着各自的不足:有的技术过于复杂、有的不能用于野外实弹射击报靶、有的成本过高、有的着弹实报率较低、不适用于连发射击训练等缺点。

目前应用较多的还有红外光电定位测试、基于图像处理模板匹配法、基于声电坐标定位法、基于光纤编码定位法、广义Hough变换法(基于图像处理)、面阵CCD 精度靶等报靶系统,都是较有效的测试方法[3]。

近年来发展起来一种新型智能自动报靶系统,与传统的实弹射击准备工序繁琐且隐藏着极大的安全隐患比较,利用这种报靶系统开展的训练将会更安全高效。

这一智能自动报靶系统由主机、从机、靶面传感器三部分构成。

具有可对射击过程全程监控,并作数据处理、自动统计以及查询成绩等功能,还可对射手存在的问题作出分析,极大地提高了训练效率[4]。

可以预见,这种新型智能自动报靶系统将会在不远的将来取代传统自动报靶系统并向更加智能化、自动化、数字化方向发展,它将可能成为未来研制报靶系统的新趋势。

1.2 基于激光坐标定位法实现的自动报靶系统简介激光坐标定位法在一些资料中也称为光电坐标定位法,光电靶是由X、Y两个方向上的激光网络构成,如图l 所示。

图1.1 光电靶将普通靶纸置于激光网络之前并与之同轴,当子弹打破靶纸,并穿越激光网络时,会阻断相应位置处X和Y两个方向上的各一路激光,从而使接收装置(光敏管)开关状态发生变化[5][6]。

一种自动报靶系统的设计与实现

一种自动报靶系统的设计与实现传统的报靶主要依靠人工实现,存在精度不高、安全隐患较大及人力资源浪费的不足。

现在市场上一些自动报靶的产品中普片存在成本高、系统比较复杂,并且占用场地等缺陷,本文所设计的报靶系统是基于多靶多人同时射击时,射手和检查监控都能实时检测子弹是否击中靶子并实现自动报靶,系统能科学、精确、实时地测量射击的环数和方位,客观、公正地评价射击训练成绩,有效地指导射击训练,满足信息化建设和训练的急需。

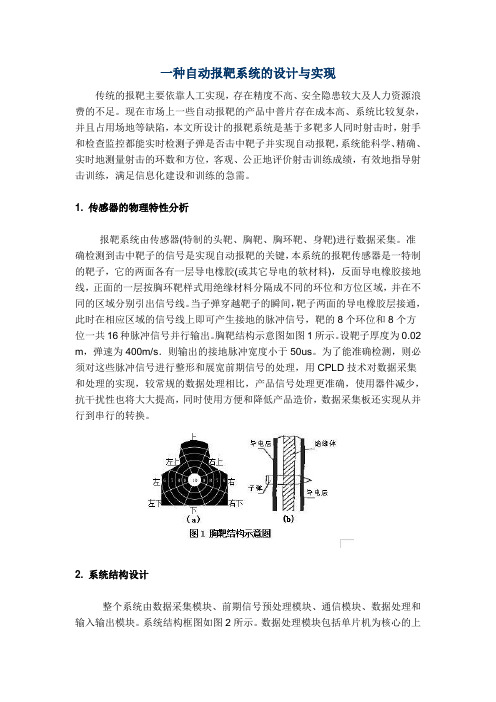

1. 传感器的物理特性分析报靶系统由传感器(特制的头靶、胸靶、胸环靶、身靶)进行数据采集。

准确检测到击中靶子的信号是实现自动报靶的关键,本系统的报靶传感器是一特制的靶子,它的两面各有一层导电橡胶(或其它导电的软材料),反面导电橡胶接地线,正面的一层按胸环靶样式用绝缘材料分隔成不同的环位和方位区域,并在不同的区域分别引出信号线。

当子弹穿越靶子的瞬间,靶子两面的导电橡胶层接通,此时在相应区域的信号线上即可产生接地的脉冲信号,靶的8个环位和8个方位一共16种脉冲信号并行输出。

胸靶结构示意图如图1所示。

设靶子厚度为0.02 m,弹速为400m/s.则输出的接地脉冲宽度小于50us。

为了能准确检测,则必须对这些脉冲信号进行整形和展宽前期信号的处理,用CPLD技术对数据采集和处理的实现,较常规的数据处理相比,产品信号处理更准确,使用器件减少,抗干扰性也将大大提高,同时使用方便和降低产品造价,数据采集板还实现从并行到串行的转换。

2. 系统结构设计整个系统由数据采集模块、前期信号预处理模块、通信模块、数据处理和输入输出模块。

系统结构框图如图2所示。

数据处理模块包括单片机为核心的上位机和以Delphi为基础开发的一个PC机监控终端。

系统可以同时进行12名射手射击,单片机上位机为每个射手显示实时成绩,PC机监控终端则可以实时显示所有射手的成绩,用于对射击的检查监控。

数据采集由特制的信号靶传感器采集;前期信号预处理采用大规模数字集成电路CPLD设计,把前几个单元电路集成在一个顶层电路,将其所实现功能写入一片CPLD芯片中,减少了电路空间,提高了总体可靠性;通信模块由微功率无线数传模块ZT—TR43U组成,具有低功耗、高可靠性、传输性能优良等特点,同时它还具备USB接口的方式,与PC机进行良好的通信;输入输出模块由键盘、液晶模块和PC机等组成。

数字电路课程设计弹道设计

淮海工学院课程设计报告书课程名称:电子技术课程设计(二)题目:弹道计时器设计系(院)://////学期:2010-2011-1专业班级:88姓名:999999学号:555555一、所选课题: 弹道计时器的设计 二、任务与要求设计一个用来测量手枪子弹等发射物速度的便携式电池供电计时器,这种计时器可用来测定子弹或其他发射物的速度。

竞赛射手通常用这种设备来测定装备的性能。

基本操作要:射手在两个分别产生起始测量脉冲和终止测量脉冲的光敏传感器上方射出一个发射物,两个光传感器(本例中假定为阴影传感器)分开放置,两者之间的距离已知。

发射物在两个传感器之间的飞行时间直接与发射物的速度成正比。

如下图所示,当子弹等发射物从上方经过起始传感器产生ST 信号,经过终止传感器时产生SP 信号。

传感器之间的距离是固定的。

通过测量子弹等发射物经过传感器之间的时间T 就可计算出子弹的速度V=S/t 。

起始传感器终止传感器阳光弹道图1三、方案制定使用中规模集成电路设计弹道计时器。

此方案中主要用到555定时器、十进制计数器、译码器、七段数码管以及一些小型门电路和触发器等。

四、弹道计时器的原理运用中规模集成电路设计本课题要分为一下几点:(1)传感器对计数器的控制。

在传感器的选择上,要注意传感器的输出信号能否直接控制下一级电路。

此论文中采用天幕靶控制计数器的工作与停止。

天幕靶是一种光电传感器,它能将光信号转变成电信号,在子弹遮蔽第一个天幕靶时,即会产生一个脉冲,此脉冲带动计数器工作,在子弹遮蔽下一个天幕靶时又产生一个脉冲,让计数器停止工作。

若将此脉冲作为使能信号,就必须使其从子弹到达第一个天幕靶一直维持到子弹到达第二个天幕靶。

由此便想到了利用T 触发器的特性达到此要求。

(2)脉冲发生器的设计。

用石英晶体振荡器和分频器构成时钟脉冲。

因为555定时器组成的多谐振荡器最高振荡频率只有500KHz,而本设计要求脉冲频率较高,故采用石英晶体振动器。

数字电子技术课程设计报告-射击自动报靶器

题目:射击自动报靶器班级:目录一、设计任务要求—————————1二、方案设计与论证————————2三、各单元电路设计与分析—————3四、总体电路原理图及元器件清单——6五、电路仿真及仿真结果分析————9六、作品照片———————————9七、结论与心得体会————————10射击自动报靶器一、设计任务与要求1,用11个开关信号模拟环数取样信号,分别表示(0,1,2,3,4,5,6,7,8,9,10环,其中0表示没射中,每次射击完毕后立刻显示环数2,每个人可以射击5次,5次后射击次数自动清零,表示此人不能再射击3,自动统计累计环数并显示。

二,方案设计与论证从设计要求可以看出是要设计出一个能够实现自动显示射击次数,单次射击环数,中靶次数以及中靶总次数的自动报靶器。

由其功能可以看出在此设计中要用到编码器,计数器,加法器,寄存器,译码器,门电路以及一些基础元件来设计出相对应的功能。

1 设计方案(1)电路原理框图(2)设计思路1开关信号模拟环数取样信号选用十一个开关,分别代表打靶成绩:1,2,3,4,5,6,7,8,9,10环,其中10环用一个显示,每次只有一个开关从高电平变到低电平。

2编码电路选用74ls148优先编码器,将两个编码器,非门和与非门连接成16--4线优先编码器,对十一个摸拟信号进行编码。

3计数器电路计数器电路分为射击次数计数和中靶次数计数两部分。

两部分都选用74 ls160计数器,射击次数部分用反馈置零法接成5进制计数器,并用十一个开关模拟信号用组合逻辑电路连接成CP脉冲,当第五次射击完成立即清零。

中靶次数部分则以优先编码器的四个输出通过组合逻辑电路连接成CP脉冲。

4显示电路选用七段显示译码器对单次靶数,射击次数、中靶次数、中靶总次数进行显示。

5复位清零电路通过一个接电源的开关连接在对中靶次数进行计数的74 ls160的CLR的端和两个寄存器的CLR的端,对中靶次数和总次数进行手动复位清零。

自动射击报靶装置

自动射击报靶装置徐暑葛宇清李亚运南京医科大学基础医学院生物医学工程系一.引言 (5)二.硬件部分方案设计 (5)1.激光笔方位控制方案论证 (6)1.1电机选择方案 (6)1.2电机驱动模块的方案论证 (6)1.3电机组合方案 (7)1.4激光枪控制方案论证 (8)2.图像采集方案 (8)3.无线通讯模块 (9)4.显示模块 (9)四:软件部分设计 (11)1.射击位控制 (11)2.靶位检测的分析 (12)四.系统调试 (17)2.测试内容 (17)a.基础要求 (17)b.发挥部分 (18)3.结果分析 (18)附录: (19)摘要:系统采用两片MSP430F149作为激光枪自动射击装置控制系统的控制核心,其中1片作为主MCU控制激光枪模块的击发、自动瞄准程序、通过弹着点坐标判定打靶环数及方位,自动报靶及在12684液晶屏上显示弹着点位置等功能,另外1片MSP430F149单片机进行图像识别处理,确定弹着点坐标,并通过nrf905无线发送给主MCU,其中弹着点检测采用带有FIFO的OV7670摄像头模块进行图像信息的采集。

主控制模块单片机接收弹着点的坐标信息,进而控制电机运转方向及步数进行弹着点的调整。

本系统可实现激光枪自动射击,通过键盘控制激光枪的弹着点在胸靶上位置,通过摄像头识别激光枪投射在胸环靶上的弹着点光斑,并显示弹着点的环数与方位信息,同时具有易于操作,精确控制,低功耗等优点。

关键词:MSP430;ov7670摄像头;自动射击;nrf905Abstract:The system uses two MSP430s as Cybernetics Core of the laser gun automatic shooting device .One MSP430 is used as main MCU.It controls the shooting of the laser gun ,also used in auto-targeting program. It determines the number of target loop and location through the coordinate of the impact point.Another MSP430F149 MCU is for image recognition processing, determing the coordinates of the spot and send the message to the main MCU through the NRF905 wireless. The impact point detection module acquires an OV7670 camera with a FIFO. The camera is for the acquisition of the image information.After receiving the impact point location information, the MSP430 would control the motor so that it could make adjustments about the impact point.This system can realize automatic shooting ,. We can set Where the impact point locates on the target through the keyboard.. It also can show tthe number of target loop and the locate information of the impact point.Meanwhile it has such advantages like easy operation, accurate control and low power consumption. Keyword: MSP430;ov7670camera;automatically shooting;一.引言题目要求制作一个能够控制激光枪击发、自动报靶及自动瞄准等功能的电子系统。

自动报靶系统设计与实现

自动报靶系统设计与实现摘要:文章结合惠更斯原理的子波思想提出一种超声传感器报靶系统,当子弹穿过靶标时,弹头波在其脉冲压力作用下通过空气介质向四周传播,直至遇上微孔管,部分激波通过微孔管到达传感器。

接收信号采用无线传输模块,通过解析各个传感器的时差值来计算弹丸位置,以此实现弹着点自动报靶的系统。

本系统对射击瞄准点指示物无特定要求,结构简单、定位精度高、不受外界环境影响,通过孔式传感器和幕布的方式解决多位无干扰和连发的问题。

引言为了更好、更高效地训练枪械持有者的射击技能,解决传统训练设备技术落后、效率低等问题,更好地适应高效、通用、科学的训练形势,发展与之相适应的新的现代化训练设备迫在眉睫。

现有大多数自动报靶定位装置的靶标皆为有形靶标。

多数采用封闭式声空腔结构,采用前后封闭靶板,对前后封闭靶板受弹数有一定的技术要求,1cm2多者8发、少者4发前后靶板就要修补。

因而靶标的使用寿命低,更换修补次数多。

另外,现有技术中的定位方法是利用弹丸的弹头波到达靶面上的不同传感器所产生的时间差,确定弹丸在靶面上的坐标。

虽能较好解决弹丸精确定位,但是不能解决连发问题。

因此,现有的声电定位装置存在以上缺陷,而且适用范围也有一定的局限性。

针对现有技术的上述不足,提出一种敞开形超声传感器的报靶系统,其结构简单、体积小、重量轻、无耗材并且野外布设、便携、射击瞄准指示物材料无特定要求,定位精度高,能解决弹丸单、连发精确定位问题。

是一种能很好适用于野外实弹连发射击训练、演习、战场杀伤破坏评估中弹丸定位及自动报靶的声电定位装置。

1 声电定位原理声电定位的主要优点在于测量精度高,工作与光照条件无关,可以全天候工作。

对装于“口”型布阵靶框内侧的声学传感器来说,枪械类型和射击距离不同,其探测到的传感器信号不同,波形也会有所不同。

在一个矩形木质框架上装入若干个声电传感器,当弹头从框架内穿过时,冲击框架内的空气使之产生扰动,形成一个冲击波向周围扩散(弹头穿过点即为波源),离波源最近的传感器最先捕捉到该波,启动检靶仪开始计时,其余各传感器依次接收到该波,这样就获得若干个时间差,通过这些时间差及弹头速度(波速),进行运算处理,就可以确定波源位置,即弹头穿过位置。

CX20l06A制作的射击枪靶电路

由于红外线发射电路设计应用的电源电压较高,为 12 V ,所以发射电路发出的红外线 信号功率也较大,使得发射电路与接收电路之间相距 8m 之远都能有效进行准确无误的遥控 控制,因此,非常适合制作成射击枪靶用于室内射击训练。

3. 元件选择

在图 8-7 所示的红外线遥控发射电路和图 8-8 所示的红外线遥控接收电路中, Al 、A2

均选用 NE555 型时基集成电路A3选用 LM386 型音频功率放大集成电路 KD9561 型声响集成电路A5选用 CX20106A 型遥控接收集成电路。

VT1 选用 8050 型 PNP 硅三极管

A4 选用

VT2选用 9014 型 NP~ 硅三极管。 VDl 、 VD7 选用

1N4148 型硅开关二极管 二极管

线发射驱动电路,如图 8-7 所示 c

R6 6.2

图 8-7

红外线发射电路

低频调制信号产生电路实际上是用 NE555 型时墓集成电路 Al 与电阻器 Rl 和R2,二极

管 VDl 及电容器。 和口均成的多谐振荡电路 c

高频载波信号产生电路是用另 a块 NE555 型时基集成电路应与电阻器 R3 和 R4 及电 容器c6组成的二

图 8-8

用 CX20l 06A 制作的射击枪靶电路

由阻~561 型音乐集成电路、电阻器R8和 R10 ,以及稳压二极管 V团组成音频产生电路。

音频放大电路由 LM386 型集成电路,以及搞合电容器(卫、 C9 、 ClO构成。

电一声转换电路就是扬声器 B" 闪光驱动电路由双向晶闸管 VS 驱动红色发光二极管 LED2 组成。这里 LED2 是由一串 红色发光二极管串联组成,图 8-8 中只画出了一个发光二极管符号为代表。

本科毕业设计论文--基于单片机控制的自动报靶系统设计

目录1 引言 (1)1.1 自动报靶国内研究状况 (1)1.1.1 基于图像处理技术的自动报靶系统 (1)1.1.2 基于CCD线阵实现的自动报靶系统 (2)1. 2 各类自动报靶系统利弊分析 (3)1.3 本设计选取方案——激光坐标定位法 (3)2 基于激光坐标定位法的自动报靶系统设计 (5)2.1 光电靶的设计 (6)2.1.1 激光网格的设计 (6)2.1.2 激光发射电路的设计 (7)2.1.3 激光接收电路的设计 (8)2.1.4 数据采集电路的设计 (9)2.2 单片机最小系统 (11)2.2.1 AT89S52单片机简介 (11)2.2.2 单片机最小系统 (12)2.3 无线收发模块 (12)2.3.1 nRF24L01概述 (13)2.3.2 引脚功能及描述 (14)2.3.3 工作模式 (15)2.3.4 工作原理 (15)2.3.5 配置字 (16)2.4 液晶显示模块 (16)2.5 RS232通信模块 (18)2.5.1 RS232通信简介 (18)2.5.2 RS232通信模块 (20)2.6 声音提示模块 (21)3 系统软件设计 (22)3.1 上位机VB程序设计 (22)3.1.2 MSComm控件简介 (22)3.1.2 自动报靶数据管理系统界面介绍 (23)3.2 下位机C语言程序设计 (26)3.2.1 Keil软件简介 (26)3.2.2 靶机系统程序设计 (27)3.2.3 无线收发显示系统程序设计 (31)4 系统软件仿真与调试 (38)4.1 Proteus软件简介 (38)4.2 软件仿真 (38)4.3 系统调试 (38)4.3.1 光电靶供电问题及其解决方案 (39)4.3.2 无线通信模块通信问题及其解决方案 (39)5 总结 (40)附录A系统原理图 (41)附录B打靶模块实物图 (42)附录C无线通信显示模块实物图 (43)参考文献 (44)致谢 (46)1 引言射击是军队常见的训练科目,而报靶是射击的重要环节。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

题目:射击自动报靶器班级:

目录

一、设计任务要求—————————1

二、方案设计与论证————————2

三、各单元电路设计与分析—————3

四、总体电路原理图及元器件清单——6

五、电路仿真及仿真结果分析————9

六、作品照片———————————9

七、结论与心得体会————————10

射击自动报靶器

一、设计任务与要求

1,用11个开关信号模拟环数取样信号,分别表示

(0,1,2,3,4,5,6,7,8,9,10环,其中0表示没射中,每次射击完毕后立刻显示环数2,每个人可以射击5次,5次后射击次数自动清零,表示此人不能再射击3,自动统计累计环数并显示。

二,方案设计与论证

从设计要求可以看出是要设计出一个能够实现自动显示射击次数,单次射击环数,中靶次数以及中靶总次数的自动报靶器。

由其功能可以看出在此设计中要用到编码器,计数器,加法器,寄存器,译码器,门电路以及一些基础元件来设计出相对应的功能。

1 设计方案

(1)电路原理框图

(2)设计思路

1开关信号模拟环数取样信号

选用十一个开关,分别代表打靶成绩:1,2,3,4,5,6,7,8,9,10环,其中10环用一个显示,每次只有一个开关从高电平变到低电平。

2编码电路

选用74ls148优先编码器,将两个编码器,非门和与非门连接成16--4线优先编码器,对十一个摸拟信号进行编码。

3计数器电路

计数器电路分为射击次数计数和中靶次数计数两部分。

两部分都选用74 ls160计数器,射击次数部分用反馈置零法接成5进制计数器,并用十一个开关模拟信号用组合逻辑电路连接成CP脉冲,当第五次射击完成立即清零。

中靶次数部分则以优先编码器的四个输出通过组合逻辑电路连接成CP脉冲。

4显示电路

选用七段显示译码器对单次靶数,射击次数、中靶次数、中靶总次数进行显示。

5复位清零电路

通过一个接电源的开关连接在对中靶次数进行计数的74 ls160的CLR的端和两个寄存器的CLR的端,对中靶次数和总次数进行手动复位清零。

三、单元电路设计与参数计算

1、开关模拟环数取样信号电路单元设计

分析:该单元利用开关来模拟数字电路中的高电平与低电平,高电平用二进制数1表示,低电平用二进制数0表示。

因此用十一个开关来摸拟高低电平,并送入芯片74LS184优先编码器早进行编码。

从而达到了模拟打靶环数的目的。

2、优先编码器单电路设计

分析:该单元电路用到两片74LS148优先编码器,将第1片的EO'接第2片的EI' 端,则只有当第1片没有编码输入信号时,第2片才能工作,这样就把两片74LS148进行了优先权排队,第1片的优先权高于第2片。

由于每片74LS148本身已经对它的8个输入端按优先权高、低进行了排队,所以就形成了16—4优先编码器。

输出最高位则由第一片的GS’产生。

3、计数器和CP脉冲单元电路设计

分析:射击次数计数部分的CP脉冲是由十一个开关模拟信号通过组合逻辑电路连接而成的,这个CP脉冲同时也是两个74LS175寄存器的CP脉冲。

将计数器用反馈置零法接成5进制计数器,其它没有引脚接相应的高低电平。

这样射击次数的功能就实现了。

中靶次数计数部分的CP脉冲则由编码单元电路的四个输出通过组合逻辑电路连接而成的。

其它引脚接相应输入输出即可。

四总电路工作原理和元器件清单

1总原理图

2.电路完整工作过程描述(总体工作原理)

电路开始工作后,由开关控制输出模拟的环数取样信号,每次输出一组二进制代码,和一个由处理产生的CP脉冲。

这组代码经过优先编码器进行编码并输出,然后在七段显示译码器上显示出这次射击的环数。

同时统计中靶次数的计数器在以优先编码器输出处理而成的CP脉冲的作用下开始计数,每个下降沿的到来计数加一,当没射中时,则CP脉冲不产生下降沿,从而不加一。

而由开关模拟的环数取样信号处理而成的CP信号则直接对统计射击次数的计数器起作用,同样也是每个下降沿来时计数加一。

这个CP信号还通过一个非门与两个74LS175寄存器的CLK相连,从而控制寄存器内容的更新,每一个上升沿更新一次。

优先编码器产生的四位二进制代码将输入到六位串行进位加法器中,与寄存器所寄存的数相加,相加后的结果就

寄存在寄存器中。

寄存器寄存的六位二进制数则输入六位二进制—8421BCD码转换组合逻辑电路中,经过转换后输出的8位8421BCD码能过两个七段显示译码器显示。

以上过程重复5次后,由于统计射击次数的计数器被连接成五进制计数器,所以在计数到五时会立即清零。

而统计中次数和寄存器不被清零,分别计下了一个选手的中靶次数和总成绩。

等到计下成绩后,经手复位清零电路对其进行清零复位。

3.元件清单

五.电路仿真

六.作品照片

七.结论与心得

在这次设计中遇到了很多实际性的问题,在实际设计中才发现,书本上理论性的东西与在实际运用中的还是有一定

的出入的,所以有些问题不但要深入地理解,而且要不断地更正以前的思维。

一切问题必须要靠自己一点一滴的解决,而在解决的过程当中你会发现自己在飞速的提升。

对于教材管理系统,其理论知识相对而言是比较简单的,主要是讲解一些基本的概念以及一些简单的设计中需要用到的一些基本芯片的排线,各个接口的功能以及整个芯片可以实现的功能,然而程序设计是一个很灵活的东西,它不仅需要你对一些基本芯片的功能的了解,而且还需要你解决问题的逻辑思维能力和创新能力,而且逻辑思维能力和创新能力才是一个设计的灵魂所在。

因此在整个设计过程中大部分时间是用在设计是如何实现上面的。

很多子功能的实现是可以借鉴书本上的一些基本芯片的功能的,但怎样衔接各个子程序才是关键的问题所在,这需要对系统的结构很熟悉。

因此可以说系统的设计是各个子功能协调合并才能够实现的。

通过这次课程设计我也发现了自身存在的不足之处,虽然感觉理论上已经有了一定的掌握,但在运用到实践的过程中仍有很多想不到的困惑,经过一番努力才得以解决。

通过这次对电子自动报靶器的设计,让我了解到数字电子技术电路设计的基本步骤,也让我了解到了关于电子自动报靶器的设计原理以及设计理念;要设计数字电子电路首先要对该次设计要达成的主要功能进行了解,其次就是要对可以实现相关的功能的元器件进行选择。

想要完成电子电路的设计,就需要对课本知识

有一个比较深入的了解.我觉得课程设计是理论与实践相结合的,通过课程设计我们可以更好的理解课本中的相关知识,对课本中的理论知识就有了一个更加深入了解;同时还可以将我们所学习的课本知识很灵巧的应用于实际生活当中,这就更好的达成了教学任务。

与此同时,我们不再是那种只会读课本知识而无法应用于实践,相反的,通过课程设计不仅使我们对课本知识有了更深入的理解,还使我们成为具有一定动手实践的能力。

最重要的是课程设计可以提高我们的逻辑思维能力以及解决实际问题的能力。