bandgap带隙基准源电路

无运放带隙基准电路设计

无运放带隙基准电路设计

运放带隙基准电路(opamp bandgap reference circuit)是一种基于运放的电路,用于提供稳定的参考电压。

它的设计基于运放的放大特性和电压反馈机制,通过差分放大和反馈调整,产生一个相对稳定的参考电压。

下面是一种常见的运放带隙基准电路的设计:

1. 选择一个适当的运放芯片,具有低噪声、高增益和低温漂移等特性。

2. 将运放芯片的非反相输入端与反相输入端相连,形成一个差分输入。

3. 将一个稳定的参考电压Vref1与非反相输入端相连。

4. 将运放芯片的反相输入端与一个电阻R1相连,然后将R1与一个稳流二极管D1的阴极相连。

5. 通过调整R1的值,使得二极管D1的电流可以产生一个正向电压降,并且与稳定的参考电压Vref1相等。

6. 将运放芯片的输出端与R1与D1的连接处相连,形成一个反馈回路。

7. 调整运放芯片的反馈电阻R2的值,使得输出电压与稳定的参考电压Vref2相等。

通过以上设计,运放正向反馈的放大特性和电压反馈机制可以保证输出电压与参考电压的稳定性。

同时,稳定的参考电压Vref1的产生通过差分放大和反馈调整的方式可以减少温度、电源等参数的影响。

需要注意的是,具体的设计参数需要根据具体的应用要求来确定,比如参考电压的稳定性要求、输出电压的范围等。

同时,在实际设计过程中,还需要考虑电源稳定性、电路布局和滤波等因素,以确保设计的稳定性和可靠性。

bandgap电路设计报告

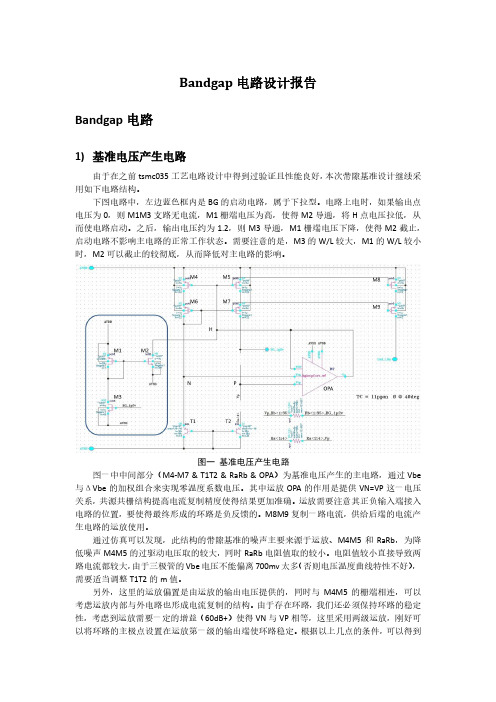

Bandgap电路设计报告Bandgap电路1)基准电压产生电路由于在之前tsmc035工艺电路设计中得到过验证且性能良好,本次带隙基准设计继续采用如下电路结构。

下图电路中,左边蓝色框内是BG的启动电路,属于下拉型。

电路上电时,如果输出点电压为0,则M1M3支路无电流,M1栅端电压为高,使得M2导通,将H点电压拉低,从而使电路启动。

之后,输出电压约为1.2,则M3导通,M1栅端电压下降,使得M2截止,启动电路不影响主电路的正常工作状态。

需要注意的是,M3的W/L较大,M1的W/L较小时,M2可以截止的较彻底,从而降低对主电路的影响。

图一基准电压产生电路图一中中间部分(M4-M7 & T1T2 & RaRb & OPA)为基准电压产生的主电路,通过Vbe 与ΔVbe的加权组合来实现零温度系数电压。

其中运放OPA的作用是提供VN=VP这一电压关系,共源共栅结构提高电流复制精度使得结果更加准确。

运放需要注意其正负输入端接入电路的位置,要使得最终形成的环路是负反馈的。

M8M9复制一路电流,供给后端的电流产生电路的运放使用。

通过仿真可以发现,此结构的带隙基准的噪声主要来源于运放、M4M5和RaRb,为降低噪声M4M5的过驱动电压取的较大,同时RaRb电阻值取的较小。

电阻值较小直接导致两路电流都较大,由于三极管的Vbe电压不能偏离700mv太多(否则电压温度曲线特性不好),需要适当调整T1T2的m值。

另外,这里的运放偏置是由运放的输出电压提供的,同时与M4M5的栅端相连,可以考虑运放内部与外电路也形成电流复制的结构。

由于存在环路,我们还必须保持环路的稳定性,考虑到运放需要一定的增益(60dB+)使得VN与VP相等,这里采用两级运放,刚好可以将环路的主极点设置在运放第一级的输出端使环路稳定。

根据以上几点的条件,可以得到运放的结构如下图二所示。

其中的两个P管电流源可以看成是与图一中M4和M5成电流复制结构。

eetop Bandgap and LDO_带隙基准与线性稳压器讲解

1 : 1V REF∂V 考虑版图,N可取8R3=R0, R4=R2, M3=M2,R3R0R4R2M3M2运放的失调必须控制好具体设计请参考基准电压与电流201R R V V V BEBE REF ⋅Δ+=Ref:sansen 0ln 21R R N q kT V V BE REF ⋅⋅+=−~m1156mVchapter 16()T C T V V g BE +=λ00For I DS T ln qR N kT I BG ⋅=Is PTAT0qVBG 通常在1.2左右VBG 的温度特性包含抛物线型非线性项,设计中令顶点位于常温附近更高精设计中令顶点位于常温附近,更高精度要求可采用二次补偿电路(例sansen ppt 1626)在高温与低温下其值变换较大IBG~T ,在高温与低温下其值变换较大,若用它直接去偏置其他电路,这一点须特别注意启动与稳定性启动:这个电路有两个稳定工作点,其中一个是两个支正反馈负反馈启动电路回路回路静态损耗:VDD/RESOpa RC VBG MOSCAPVREF ‐Vos +抑制/噪声采1/f噪声还可采用chopping技术V/I转换V/V转换R1=R2VBG的大小可通过整, 不影响温度系数IBG=VBG/R3,由IBG温漂较小,主要取决于电阻温度系数最低电源电压可正反馈环负反馈环MOSResistor正常输出下VBG>VTn, 否则应采用其他形式的启动电路MOSCAPPMOS采用folded结构采用PMOS输入差分对, 减少1/f噪声, 并适合于低输入共模的情况VGS‐VT小, 其他电流镜VGS‐VT大, 晶体管的L要大一些, 减输入差分对GS GS要大些少失调, 1/f噪声, 以及沟道调制效应自便置设计启动时,vb1若为高,则无法启动,故需增加拉低vb1低压设计将R1, R2由两个电阻串联,取中间点接运放输入,可降低输共模步降低压压入共模,进一步降低电压电压要求运放采用PMOS输入的folded‐cascode结构或symmetrical结构可进一步采用电路设计技术来降低运放对电源电压的要求‐Sub1V Bandgap ExampleRef: Ka Nang Leung, JSSC2002采用symmetrical结构和电平移位(level shifting)来降低输入共模要求ip inPhase 1in ipPhase 2基本LDO 电路g ma g mp REFL V R R R V ⋅+≈221R Off ‐chipdecoupleVREF 由bandgap 来提供Z g R g mp oa ma cap加中间级buffer的LDO静态功耗稳定性设计!BufferB ff加buffer的好处:1 减小err amp的负载电容,降低其静态功耗, 更易使p2与z1接近2 与MPT栅电容并联的是1/gm, not1/gds,更容易实现高极点X:1Buffer bias: IMB = IB+IMBA = IB+X*IMTP IB = ? X = ?↓ÆIMTP ↑ÆIMB ↑Æp3 ↑Æstable3t bl↑ÆIMTP ↓ÆIMB ↓Ækeep high efficiency at low loadMillercap 注意电压的范围, Cc尽量采用MOS CAP来实现,以节约面积或兼容逻辑工艺;MTP须工作在饱和区,以保证gm,保证稳定性At稳定性不依靠片外电容P2 boosting example通过miller补偿和miller boosting效应,来推高p2, 保证LDO的稳定性Ref: Kae Wong: A 150mA Low Noise, High PSRR Low‐Dropout Linear Regulator in0.13um Technology for RF SoC ApplicationsVOUT/VIN个载保护路的例子一个过载保护电路的例子(适合MTP一直饱和区工作的情况)片内解藕电容Bonding Wire使得片内高频扰动难以被片外电容滤除Bonding wireOn‐chip decouple Off‐chip decoupleMiller补偿结构MTPgmCcCL: 4n0.6V MTP: 40uACG: 2.3pCc: 5pCL: 4n输入管:W/L=4u/1u R1: 60k R2:30kIds=2u251.98u 586.35u 1.3644m 3.1748m 7.3875m MTP: 40uA CG: 2.3p 17.19m 40m p Cc: 5p CL: 4nCz: 8p 输入管:W/L 4u/1u Z1, p3R1: 60k R2: 30k W/L=4u/1u Ids=2uPSRR时Vdd 加Vac=1时,Vout 端的幅频响应IL=40mA, @6.2MHzcase =PSRR 与负载有关Worst 11.1dB低频由环路增益决定30uAgmCc Cz 对于全集成LDO, 带宽至关重要!因为此时无片外大解藕电容缓冲,负载的变化需要环路自己迅速作出响应,避免电压出现大的波形PSRRVdd 时加Vac=1时,Vout 端的幅频响应Worst case @~27.5MHz=PSRR 与负载有关 11.4dB低频由环路增益决定CLCz R2第一级输出加零点补偿电容可用MOS管实现这个电路中的问题???这个电路中的问题LDO1LDO25V 3.3V LDO1LDO25V 3.3V CHIPCHIP ???5V3.3VLDO1 1.8VLDO2VDD=3V输入偏高时, 右边的放大器工作,偏低, 则左边的工作, 在中间,两个都工作Gm没有做均衡处理, 对此应用不重要最低电源: VGS + 2VdsatLDO2VIN VBG1VIN BG VBG2LDO1CHIP f1f2。

Bandgap(带隙)_Circuit

BroadGalaxy Confidential

11

bandgap电路设计

此结构是在一个负反馈运

算放大器的两个输入端各 接一个稳压电路。两路稳

R3

R2

压电路并联。它们并联的

I1

总电压作为我们所要的参

考电压,连接到运放的输 I2 出端输出。电源电压包含

BroadGalaxy Confidential

2

电压基准和电流基准的作用

模拟电路的设计中须广泛的应用到电压基准和电流基准, 它们是直流量,为核心电路提供偏置,建立直流工作点;

一般来说,从芯片外部引入的供电电压都存在着一定的波 动,而模拟电路对偏置电压的稳定性要求较高,因此一般 会使用一个参考电压源,它将电源电压转化为一个具有良 好电压稳定性和温度稳定性的电压,以提供良好的偏置。

I

rR1

rR2 I

BroadGalaxy Confidential

6

电压基准结构选择

这说明 V在R1、R2上的分

配与R1、R2的动态电阻成 正比。如果我们能让R1的动 态电阻很小,R2的动态电阻

很大,则 V大部分落在R2

上,一小部分落在R1上, 对电源电压的灵敏度会大大

降低,稳压性能就会得到很 大提高。

r= V I

BroadGalaxy Confidential

5

电压基准结构选择

对一个一般的分压网络进行 分析,R1、R2为阻性元件。

假定电源电压变化了V ,因 为R1和R2串联,V 会以一

定比例分配在这两个电阻上 ,并且两者的电流改变量一 致。

R2 R1

VREF

一种用于LED背光驱动的带隙基准源

一种用于LED背光驱动的带隙基准源何晓宇【摘要】依据带隙基准源的基本原理设计了一种用于LED背光驱动芯片的带隙基准源,与传统带隙基准源相比,设计的带隙基准源采用了无运放电路结构。

该电路在基于0.5m BCD工艺下完成设计,通过Hspice仿真表明,当温度在–40~+125℃变化时,基准源输出电压在1.2275~1.2298 V之间变化,温漂系数仅为11.36×10–6,基准源供电电压在6~8 V之间变化时,基准源输出电压相对变化量为0.85%,满足了设计要求。

%Based on the basic theory of bandgap reference, a bandgap reference circuit for LED backlight driver was designed. Compared with the traditional ones, there is no amplifier in the present bandgap reference circuit. The circuit was designed on 0.5 m BCD process and simulated by Hspice. When the circuit is operated at 7.5 V power supply with the temperature range of–40~+125℃, the variation of the bandgap reference output voltage is 2.3 mV, and the temperature drift coefficient is only 11.36×10–6. When the power supply varies from 6 V to 8 V, the relative variation of the bandgap reference output voltage is only 0.85%. It meets the design requirements.【期刊名称】《电子元件与材料》【年(卷),期】2016(035)007【总页数】4页(P23-26)【关键词】LED背光驱动;带隙基准;共源共栅;沟道长度调制;启动电路;仿真【作者】何晓宇【作者单位】中国电子科技集团公司第四十七研究所,辽宁沈阳 110032【正文语种】中文【中图分类】TN432随着照明技术的发展,人们对于全球性的能源短缺和环保问题越来越关注,纷纷研究节能环保技术[1]。

带隙基准源研究现状与发展前景综述

带隙基准源研究现状与发展前景综述摘要:带隙基准源(Bandgap Reference),又称能隙基准源。

由于其具有优异的温度稳定性,常用于高精度的电压参考。

基准电压源是集成电路中一个重要的单元模块。

它的温度稳定性以及抗噪声能力影响到整个系统的精度和性能。

近年来,芯片系统集成(SOC)技术已经受到学术界及工业界广泛关注。

随着电路系统结构的进一步复杂化,对模拟电路基本模块提出了更高精度及速度的要求。

而带隙基准源相较于传统基准源有诸多优点,应用广泛,研究价值大,发展前景良好。

关键词:带隙基准源;集成电路;芯片系统集成;高精度1、引言输出不随温度、电源电压变化的基准源在模拟和混合集成电路中应用非常广泛,例如数据转换电路与稳压电路[1]。

在集成电路中,有三种常用的基准源:掩埋齐纳(Zener)基准源、XFET基准源和带隙(Bandgap)基准源[2]。

随着片上系统(SOC)的迅速发展,系统要求模拟集成模块能够兼容标准CMOS工艺,在SOC上,数字集成模块的噪声容易通过电源和地耦合到模拟集成模块,这要求模拟集成模块的PSRR非常高。

同时,由于移动电子设备的逐渐增多,要求模拟集成电路的电源电压能够降至1 V左右,功耗在μW量级上[3]。

所以,尽管掩埋齐纳基准源和XFET基准源的输出温度稳定性非常好,但是它们的制造流程都不能兼容标准CMOS工艺,并且掩埋齐纳基准源的输出电压一般大于5V。

带隙基准电压源包括双极型带隙基准源和CMOS带隙基准源,工艺条件宽。

带隙基准电压源的性能较其他基准有了很大的飞跃。

带隙基准输出电压受温度和电源电压影响小,并且其精度高。

基准的初始精度、温度系数、长期漂移、噪声电压等性能指标从低到高覆盖面比较宽,适用于多种不同精度要求的系统中。

该类基准既有为通常目的设计的类型,也有静态电流小至几十微安,输入输出电压差较低而适用于电池供电场合的产品,因而应用范围很宽。

综合来看,带隙基准性能良好,价格适中,是性价比最高的电压基准。

带隙基准电压源BandGap的调节与理论分析

Cascode电路结构

为保证NM20与NM21处的电压保持跟随,采用 Cascode结构使得Vo1与Vo2稳定在近似相等的电压, 那么有:

VBE1 RI VBE 2 RI VBE1 VBE 2 VT ln n VO2 VBE 2 VT ln n

产生一个和绝对温度成正比的PTAT电流。 这里的Cascode结构主要是近似为一个电路源使得 流过Q4,Q5这两条电路的电流相等使得Vo1与Vo2 VO 2稳定在近似相等的电压,所以在调试cascode电路 时要使输出电阻尽可能的大。

BandGap电路仿真结果分析

从BandGap电路的仿真结果分析得出,电路在3.3V时

候工作的比较稳定,输出的基准电压为1.235V到 1.265V之间,温漂系数低于20ppm(但是ss情况下为 26),当电源电压为3.0V或者3.6V时,在其他的不 同工艺角(tt,ff,ss,sf,fs)下,输出的基准电压 波动范围较大,且温漂系数大于20ppm(3.6V,ss情 况下为13ppm以及3v时,ff情况下为15ppm)。3V各 个工艺角下的基准电压输出范围为1.235V到1.255V 之间,3.6V各个工艺角下的基准电压输出范围为 1.265V到1.275V之间。

mV 。 K

VBE 的温度系数与温度有关。

正温度系数电压

若两个双极晶体管工作在不相等的电流密度下,那

么基极-发射极电压的差值就与绝对温度成正比。 nI0 I0 VBE VBE1 VBE 2 VT ln VT ln VT ln n I S1 IS2

VBE k ln Βιβλιοθήκη T q与温度关系变化的确定。

带隙电压基准的基本原理:将两个拥有相反温度系

数的电压以合适的权重相加,最终获得具有零温度 系数的基准电压。

带隙基准电压源(Bandgap)设计范例

图 1.1

Bandgap 模块线路图

二. 等效架构图

(a)

(b)

(c) 图 1.2 Bandgap 模块等效原理图

三. 电路功能描述

正常工作时,Bandgap 模块为系统提供稳定、高精度的 1.28v 的基准电压, 并为其它电路模块提供稳定的偏置电流。

四. 输出、输入信号线功能描述

I = I S (e qVB E / kT − 1)

(1.1) 当 VBE >> kT / q 时, I ≈ I S e q.VBE / k .T

VBE = VT . ln( I ) IS

(1.2) 其中 VT = kT 为热电压,k 是 Boltzmann 常数,q 是电荷量。 q

图 1.2(b) 是参考电压产生的实际等效架构电路, R19 、R20 、R21 、Q11 和 Q12、Q19 构成带隙电压产生器的主题部分,由 Qx10 、Qx8 、 Q19、 Qx7 、 Q10 以及 Q18 组成了放大器及补偿电路,保证了参考电压输出的稳定。 由运算放大器的性质,得:

Q12 和 Q19 的电流相等;R19、R20、R21 和二极管连接的 Q11 组成分压网络, 将 Q12、Q19 产生的 ? VBE 放大(R19+R20+R21)/R21 倍后与 VBE11 相加,产 生基准电压 VREF ;放大管 QX7 、Q18 和负载管 Q10 组成符合放大电路,将 IC19 和 IC12 的差值放大,反馈到分压网路中的 R21,从而调整 Q12、Q19 的工作点, 保证 IC19 等于 IC12 ;电容 C2 和 R23 用来进行频率补偿。 电流偏置 IBias2 产生电路(图 2(c)) :由 P39、Q3、R8 组成。Q3 的基极连 接 VREF ,其射极电位即 R8 的一端电位 VEQ3=VREF -VBEQ3,与电源电压无关, 从而流过电阻 R8 的电流与电源无关,即 IBias2 与电源无关。 1.使能原理: ENB 高电平时,使能关断有效。当 ENB 为高电平时,使能管 N15、N18、 N17 工作,则 N19 的漏极电压、P8 的漏极电压、VREF 被拉到低电平,电路关 断。 BIAS_EN 低电平时,使能关断有效。当 BIAS2_EN 低电平时,使能管 P13 工作,P7、P1 的栅极即 Bias 为高电平,电流偏置为 0,同时,基准电压 VREF 为零电平。 BIAS2_EN 低电平时,使能关断有效。当 BIAS_EN 低电平时,使能管 P34 工作,Bias2 为高电平,电流偏置 IBias2 为 0。 2.启动原理 P14、R15、N19、N16 组成启动电路。启动过程:ENB 为低电平,当未启 动时,P7、P8 两支路的电流为 0,此时 P8 的漏极电压为 0 电位,N19 不通,N19 的漏极为高电位,此时 N16 管导通,形成从电源到地的通路 R12、P7、N16,使 P7 有电流流过,从而打破 0 电流的状态;之后 P8 漏极电位上升, N19 导通, N16 截止,启动过程结束。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

bandgap带隙基准源电路

Bandgap带隙基准源电路是一种用于产生带隙基准电压的电路,它在模拟电路设计和集成电路设计中具有重要的作用。

带隙基准电压是一种与温度和电源电压无关的直流电压,它可以用于电路的偏置、ADC的基准、温度传感器等。

带隙基准源电路的设计原理是基于硅材料的带隙能量,它的带隙能量为1.12eV,对应于温度为273.15K。

带隙基准源电路的核心思想是将带隙能量转化为直流电压,并通过一定的放大和调节电路,得到温度和电源电压无关的基准电压。

带隙基准源电路的基本结构包括三个部分:偏置电路、带隙电压产生电路和放大电路。

其中,偏置电路用于产生一个与电源电压无关的直流电流,带隙电压产生电路用于将带隙能量转化为直流电压,并且放大电路用于调节带隙基准电压的大小和精度。

偏置电路通常采用一个PNP晶体管和一个电阻组成,PNP晶体管的基极-发射极电压作为偏置电压。

这个偏置电压具有负的温度系数,即随着温度的升高,它的值会减小。

为了使整个电路的温度系数为零,需要将这个偏置电压与一个具有正温度系数的电压进行补偿。

带隙电压产生电路通常采用两个晶体管和电阻组成,其中一个晶体管的基极-发射极电压作为带隙电压,另一个晶体管的基极-发射极电压具有正的温度系数。

通过调节两个晶体管的发射极电流比值,可

以得到一个与温度无关的带隙电压。

放大电路用于调节带隙基准电压的大小和精度。

通常采用一个高精度、低噪声的放大器,将带隙基准电压进行放大和调节。

放大器的增益和带宽需要满足一定的要求,以确保带隙基准电压的精度和稳定性。

在实际应用中,带隙基准源电路还需要考虑一些其他的因素,如电源噪声、温度范围、功耗等。

为了实现高精度的带隙基准电压,需要采用一些优化设计方法,如低噪声电源、温度补偿技术、自偏置电路等。

在实际应用中,带隙基准源电路有着广泛的应用。

它可以用于各种类型的模拟电路和数字电路中,如运算放大器、比较器、ADC、DAC、PLL等。

它可以提供高精度的基准电压,帮助这些电路实现高精度、低噪声、稳定的性能。

另外,带隙基准源电路也可以用于温度传感器的设计。

通过在带隙基准源电路中增加一些温度补偿机制,可以得到一个具有高精度和高灵敏度的温度传感器。

这种温度传感器可以用于各种温度监测和控制应用中,如医疗、航空航天、汽车等。

带隙基准源电路是一种重要的模拟电路设计技术,它在集成电路设计中具有广泛的应用。

它可以帮助各种类型的模拟电路和数字电路实现高精度、低噪声、稳定的性能。

随着集成电路技术的不断发展,带隙基准源电路的设计和优化将变得越来越重要。