verilog数字系统设计教程_夏宇闻编著_课后习题答案_考试重点

verilog数字系统设计教程习题答案

verilog 数字系统设计教程习题答案第二章HDL 既是一种行为描述语言,也是一种结构描述语言。

如果按照一定的规则和风格编写代码,就可以将功能行为模块通过工具自动转化为门级互联的结构模块。

这意味着利用Verilog 语言所提供的功能,就可以构造一个模块间的清晰结构来描述复杂的大型设计,并对所需的逻辑电路进行严格的设计。

2.模块的基本结构由关键词module和endmodule构成。

3.一个复杂电路系统的完整Verilog HDL 模型是由若干个VerilogHDL模块构成的,每一个模块又可以由若干个子模块构成。

其中有些模块需要综合成具体电路,而有些模块只是与用户所设计的模块交互的现存电路或激励信号源。

利用Verilog HDL语言结构所提供的这种功能就可以构造一个模块间的清晰层次结构来描述极其复杂的大型设计,并对所作设计的逻辑电路进行严格的验证。

HDL和VHDL乍为描述硬件电路设计的语言,其共同的特点在于:能形式化地抽象表示电路的结构和行为、支持逻辑设计中层次与领域的描述、可借用高级语言的精巧结构来简化电路的描述、具有电路仿真与验证机制以保证设计的正确性、支持电路描述由高层到低层的综合转换、硬件描述与实现工艺无关(有关工艺参数可通过语言提供的属性包括进去)、便于文档管理、易于理解和设计重用。

5.不是6.将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配的过程。

7.综合工具可以把HDL变成门级网表。

这方面Synopsys工具占有较大的优势,它的Design Compile 是作为一个综合的工业标准,它还有另外一个产品叫Behavior Compiler ,可以提供更高级的综合。

另外最近美国又出了一个软件叫Ambit ,据说比Synopsys 的软件更有效,可以综合50万门的电路,速度更快。

今年初Ambit 被Cadence 公司收购,为此Cade nee放弃了它原来的综合软件Syn ergy。

Verilog教程-夏宇闻

发表

4

3.1 引言

三、不同层次的Verilog HDL抽象

▪ Verilog HDL模型可以是实际电路的不同级别的抽象。

抽象级别可分为五级:

➢ 系统级(system level): 用高级语言结构(如case语句)

实现的设计模块外部性能的模型;

▪ 用小写字母定义! ——如always,assign,begin,case,casex,else, end,for,function,if,input,output,repeat, table,time,while,wire

▪ 见《数字系统设计与Verilog HDL 》P285附录A。

19

3.2 Verilog HDL基本结构

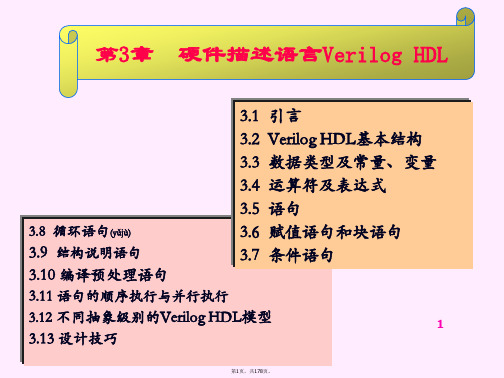

第3章 硬件描述语言Verilog HDL

3.1 引言

3.2 Verilog HDL基本结构

3.3 数据类型及常量、变量

3.4 运算符及表达式

3.5 语句

3.8 循环语句

3.6 赋值语句和块语句

3.9 结构说明语句

3.7 条件语句

3.10 编译预处理语句

3.11 语句的顺序执行与并行执行

3.12 不同抽象级别的Verilog HDL模型

➢ 每个Verilog HDL源文件中只准有一个顶层模块,其他为子模块。 ➢ 每个模块要进行端口定义,并说明输入输出端口,然后对模块的

功能进行行为逻辑描述。 ➢ 程序书写格式自由,一行可以写几个语句,一个语句也可以分多

行写。 ➢ 除了endmodule语句、begin_end语句和fork_join语句外,每个语

➢ / * …ቤተ መጻሕፍቲ ባይዱ * /内表示注释部分,一般可占据多行。 对编译不起作用!

数字系统设计与veriloghdl课后答案

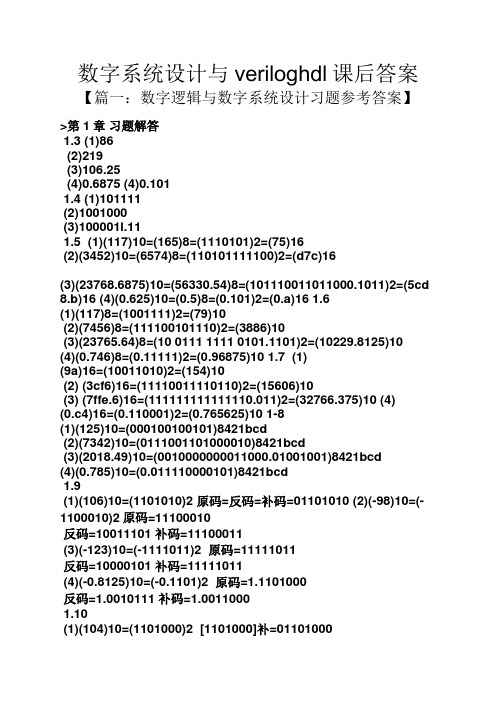

数字系统设计与veriloghdl课后答案【篇一:数字逻辑与数字系统设计习题参考答案】>第1章习题解答1.3 (1)86(2)219(3)106.25(4)0.6875 (4)0.1011.4 (1)101111(2)1001000(3)100001l.111.5 (1)(117)10=(165)8=(1110101)2=(75)16(2)(3452)10=(6574)8=(110101111100)2=(d7c)16(3)(23768.6875)10=(56330.54)8=(101110011011000.1011)2=(5cd 8.b)16 (4)(0.625)10=(0.5)8=(0.101)2=(0.a)16 1.6(1)(117)8=(1001111)2=(79)10(2)(7456)8=(111100101110)2=(3886)10(3)(23765.64)8=(10 0111 1111 0101.1101)2=(10229.8125)10(4)(0.746)8=(0.11111)2=(0.96875)10 1.7 (1)(9a)16=(10011010)2=(154)10(2) (3cf6)16=(11110011110110)2=(15606)10(3) (7ffe.6)16=(111111*********.011)2=(32766.375)10 (4)(0.c4)16=(0.110001)2=(0.765625)10 1-8(1)(125)10=(000100100101)8421bcd(2)(7342)10=(0111001101000010)8421bcd(3)(2018.49)10=(0010000000011000.01001001)8421bcd(4)(0.785)10=(0.011110000101)8421bcd1.9(1)(106)10=(1101010)2 原码=反码=补码=01101010 (2)(-98)10=(-1100010)2原码=11100010反码=10011101 补码=11100011(3)(-123)10=(-1111011)2 原码=11111011反码=10000101 补码=11111011(4)(-0.8125)10=(-0.1101)2 原码=1.1101000反码=1.0010111 补码=1.00110001.10(1)(104)10=(1101000)2 [1101000]补=01101000(-97)10=(-1100001)2 [-1100001]补=1001111101101000 + 10011111 0000011110000011 + 01001111 11010010[104-97]补=01101000+10011111=00000111, 104-97=(00000111)2=7 (2) (-125)10=(-1111101)2(79)10=(01001111)2[-1111101]补=10000011 [01001111]补=0100111101111000 [-125+79]补=10000011+01001111=11010010,-125+79=(-0101110)2=-46 (3) (120)10=(1111000)2[01111000]补=01111000(-67)10=(-1000011)2[-1000011]补=10111101[120-67]补=10000011+01001111=00110101,-125+79=(00110101)2=53 (4) (-87)10=(-1010111)2[-1010111]补=10101001(12)10=(1100)2[1100]补=00001100[-87+12]补=10101001+00001100=10110101,-125+79=(-1001011)2=-75+ 10111101 0011010110101001+ 00001100 10110101第2章习题解答2.3 解:根据逻辑图可直接写出逻辑表达式:(a) f=ab?bc;(b)f=abbcac解:设3个输入变量分别为a、b、c,输出为f,按题意,其中有奇数个为1,则输出f=1,因此可写出其逻辑表达式为f=abc?abc?abc?abc。

Verilog 教程(第三版)夏闻宇 第三部分练习题答案(精品资料).doc

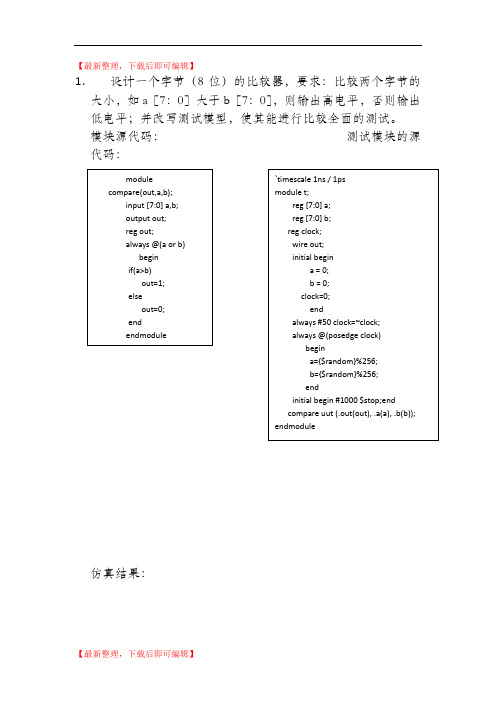

【最新整理,下载后即可编辑】1.设计一个字节(8位)的比较器,要求:比较两个字节的大小,如a[7:0]大于b[7:0],则输出高电平,否则输出低电平;并改写测试模型,使其能进行比较全面的测试。

模块源代码:测试模块的源代码:仿真结果:由图有:当a=8'01100101,b=8'00010010(即a>b 时),输出out 为高电平;当a=8'00000001,b=8'00001101(即a<b 时),输出out 为低电平,故满足要求。

2.依然作clk_in 的2分频clk_out ,要求输出时钟的相位与上面的1/2分频器的输出正好相反。

编写测试模块,给出仿真波形。

书上1/2分频器时序波形模块源代码: 测试模块源代码:仿真波形:由上图可知clk_out 的输出波形相位与前面输出波形相反。

3. 利用10 MHZ 的时钟,设计一个单周期形状的周期波形。

分析:时钟信号f=10MHZ ,分频1/20,f1=500KHZ时,j 从0计到9(10个数)跳转完成半个周期,T0/2 =0.1us ;图中可把T 分为三段即T1=T3=20us=200*0.1us(所以在T1阶段j 要计200个数),而T2=10us 可用延迟10000ns 翻转达到。

图中T=50us 之后不显示,所以测试时到达50000ns 时停止。

故其模块源代码和测试模块源代码如下:模块源代码: 测试模块源代码:仿真波形:4.在blocking模块中按如下两种写法,仿真与综合的结果会有什么样的变化?作出仿真波形,分析综合结果。

⑴综合结果 ⑵综合结果由以上图形可知,其综合结果一样。

其仿真图形如下所示:分析:当时钟上升沿来临,b1、b2的值一样都等于时钟上升沿到来前a的值,两种写法的区别在于c值的不同。

第一种写法c1的值等于前一个b1的值;第二种写法c2的值等于b2的值即c1比c2慢一个时钟信号周期。

5.运用always块设计一个8路数据选择器。

《Verilog数字系统设计教程》夏宇闻第四版思考题答案(第2章)

《Verilog数字系统设计教程》夏宇闻第四版思考题答案(第2章)1.Verilog语⾔有什么作⽤?可描述顺序执⾏和并⾏执⾏的程序结构;⽤延迟表达式或事件表达式来明确的控制过程的启动时间;通过命名的事件来触发其它过程⾥的激活⾏为或停⽌⾏为;提供了条件如if-else,case等循环程序结构;提供了可带参数且⾮零延续时间的任务程序结构;提供了可定义新的操作符的函数结构;提供了⽤于建⽴表达式的算术运算符,逻辑运算符,位运算符;Verilog HDL语⾔作为⼀种结构化的语⾔⾮常适⽤于门级和开关级的模型设计;提供了⼀套完整的表⽰组合逻辑的基本元件的原话;提供了双向通路和电阻器件的原话;可建⽴MOS器件的电荷分享和电荷衰减动态模型;Verilog HDL的构造性语句可以精确地建⽴信号的模型;2.构成模块的关键词是什么?module,endmodule。

3.为什么说可以⽤Verilog构成⾮常复杂的电路结构?因为Verilog可描述顺序执⾏和并⾏执⾏的程序结构;⽤延迟表达式或事件表达式来明确的控制过程的启动时间;通过命名的事件来触发其它过程⾥的激活⾏为或停⽌⾏为;提供了条件如if-else,case等循环程序结构;提供了可带参数且⾮零延续时间的任务程序结构;提供了可定义新的操作符的函数结构;提供了⽤于建⽴表达式的算术运算符,逻辑运算符,位运算符;Verilog HDL语⾔作为⼀种结构化的语⾔⾮常适⽤于门级和开关级的模型设计;提供了⼀套完整的表⽰组合逻辑的基本元件的原话;提供了双向通路和电阻器件的原话;可建⽴MOS器件的电荷分享和电荷衰减动态模型Verilog HDL的构造性语句可以精确地建⽴信号的模型;4.为什么可以⽤⽐较抽象的描述来设计具体的电路结构?因为有可以⽤⽐较抽象描述设计电路结构的语⾔,⽽这种语⾔是适合数字系统设计的语⾔。

5.是否任意抽象的符合语法的Verilog模块都可以通过综合⼯具转变为电路结构?不能。

[工学]西安电子科技大学verilog教程1-2

![[工学]西安电子科技大学verilog教程1-2](https://img.taocdn.com/s3/m/7e9aa877240c844768eaeea1.png)

西安电子科技大学

雷达信号处理国防科技重点实验室

2. 数字信号处理

数字信处理系统往往要进行一些复杂的数字运算和数据处理, 并且又有实时响应的要求,他们通常是由高速专用数字逻辑系统或专 用数字信号处理器所构成,电路是相当复杂的。因此只有在高速大规 模集成电路设计制造技术进步的基础上,才有可能实现真正有意义的 实时数字信号处理系统。对实时数字信号处理系统的要求不断提高, 也推动了高速大规模集成电路设计制造技术的进步。现代专用集成电 路的设计是借助于电子电路设计自动化(EDA)工具完成的。学习和 掌握硬件描述语言(HDL)是使用电子电路设计自动化工具的基础。

• 由传统的观点出发,可以从三个不同的方面来研究计算,即从数 学、科学和工程的不同角度;由比较现代的观点出发,可以从四 个主要的方面来研究计算,即从算法和数据结构、编程语言、体 系结构、软件和硬件设计方法学。

• 一个复杂的数字系统设计往往是从算法到由硬线连接的门级逻辑 结构,再映射到硅片的逐步实现的过程。

&Moorby,刘明业等译。

西安电子科技大学

雷达信号处理国防科技重点实验室

课时及考试安排

授课时数:30课时 上机时数;14课时 考试时数:90分钟 成绩计算:大作业*40%+考试*60%

西安电子科技大学

雷达信号处理国防科技重点实验室

课程内容安排

第一部分 初级篇

第一章. 概述及设计工具介绍 第二章. Verilog HDL的基本知识 第三章. Verilog HDL基本概念 第四章. 常用Verilog语法之一 第五章.常用Verilog语法之二 第六章.常用Verilog语法之三 第七章.常用Verilog语法之四 第八章.常用Verilog语法之五

Verilog数字系统设计教程[夏宇闻]PPT课件

![Verilog数字系统设计教程[夏宇闻]PPT课件](https://img.taocdn.com/s3/m/4645846c58fafab069dc0258.png)

设计示例四(续) 用激励信号对进位计数器进行测试

module stimulus; reg clk; reg reset; wire[3:0] q; // instantiate the design block ripple_carry_counter r1(q, clk, reset); // Control the clk signal that drives the design block. initial clk = 1'b0; always #5 clk = ~clk;

设计示例四 带异步复位端的 D 触发器

module DFF(q, d, clk, reset); output q; input d, clk, reset; reg q; always @(posedge reset or negedge clk) if (reset) q <= 1'b0; else q <= d; endmodule

设计示例二

由已设计的模块来构成高一级的模块

q3

q2

q1

q0

d

q

d

f4

clk clr

f3

clk clr

q

d

f2

clk clr

q

d

f1

clk clr

q

clrb

clk

d3

d2

d1

d0

四位寄存器电路结构图

设计示例二 `include “ flop.v ” module hardreg(d,clk,clrb,q); input clk,clrb; input[3:0] d; output[3:0] q; flop f1(d[0],clk,clrb,q[0],), f2(d[1],clk,clrb,q[1],), f3(d[2],clk,clrb,q[2],), f4(d[3],clk,clrb,q[3],); endmodule

Verilog教程-夏宇闻(共178张)

第13页,共178页。

3.2 Verilog HDL基本(jīběn)结构

二、Verilog HDL模块的结构

▪ Verilog的基本设计单元是“模块 (block) ” 。 ▪ Verilog 模块的结构由在module和endmodule关键词

之间的4个主要部分组成:

1 端口定义 2 I/O说明

(3)用 “always” 块语句 结构说明语句

always @(posedge clk) // 每当时钟上升沿到来时执行一遍块内语句

begin

if(load)

out = data; // 同步预置数据 else

out = data + 1 + cin; // 加1计数

end

❖注1:“always” 块语句常用于描述时序逻辑,也可 描述组合逻辑。

3.12 不同抽象级别的Verilog HDL模型

1

3.13 设计技巧

第1页,共178页。

引言 3.1

(yǐnyán)

内容概要

一、什么是Verilog HDL 二、Verilog HDL的发展历史 三、不同层次的Verilog HDL抽象

四、Verilog HDL的特点

2

第2页,共178页。

3.1 引言(yǐnyán)

❖ Verilog HDL模块的模板(仅考虑用于逻辑综合的部分)

module <顶层模块名> (< 输入输出端口列表>) ;

output 输出端口列表;

input 输入端口列表;

//(1)使用assign语句定义逻辑功能

wire 结果信号名;

assign <结果信号名> = 表达式 ;